| Citation: |

Tommaso Zanotti, Tommaso Rizzi, Emilio Pérez-Bosch Quesada, Andrea Baroni, Keerthi Dorai, Swamy Reddy, Eduardo Pérez, Christian Wenger, Paolo Pavan, Francesco Maria Puglisi. Physics-based RRAM compact model for multilevel programming across multiple timescales[J]. Journal of Semiconductors, 2026, In Press. doi: 10.1088/1674-4926/25100024

****

T Zanotti, T Rizzi, E P Quesada, A Baroni, K Dorai, S Reddy, E Pérez, C Wenger, P Pavan, and F M Puglisi, Physics-based RRAM compact model for multilevel programming across multiple timescales[J]. J. Semicond., 2026, accepted doi: 10.1088/1674-4926/25100024

|

Physics-based RRAM compact model for multilevel programming across multiple timescales

DOI: 10.1088/1674-4926/25100024

CSTR: 32376.14.1674-4926.25100024

More Information-

Abstract

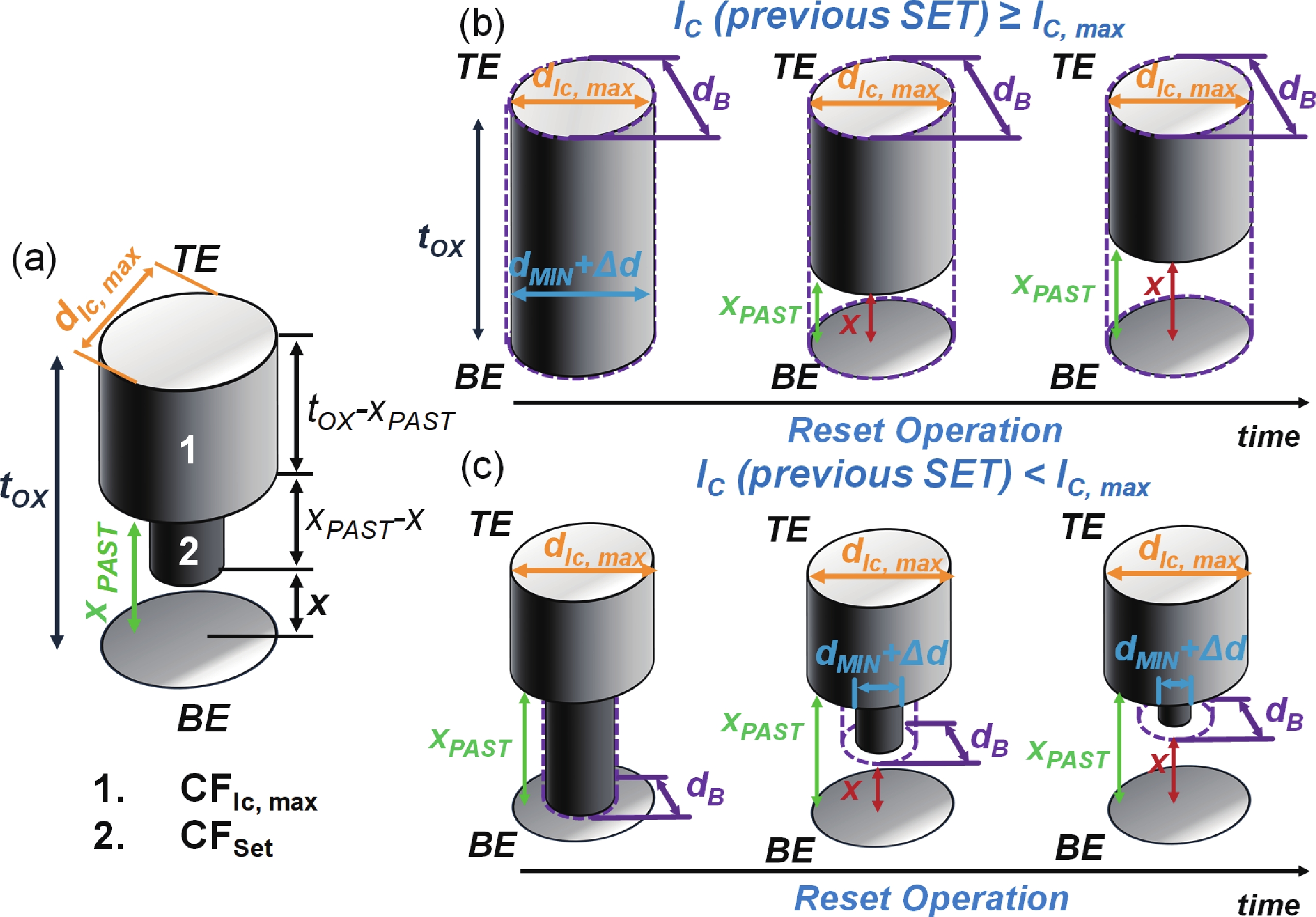

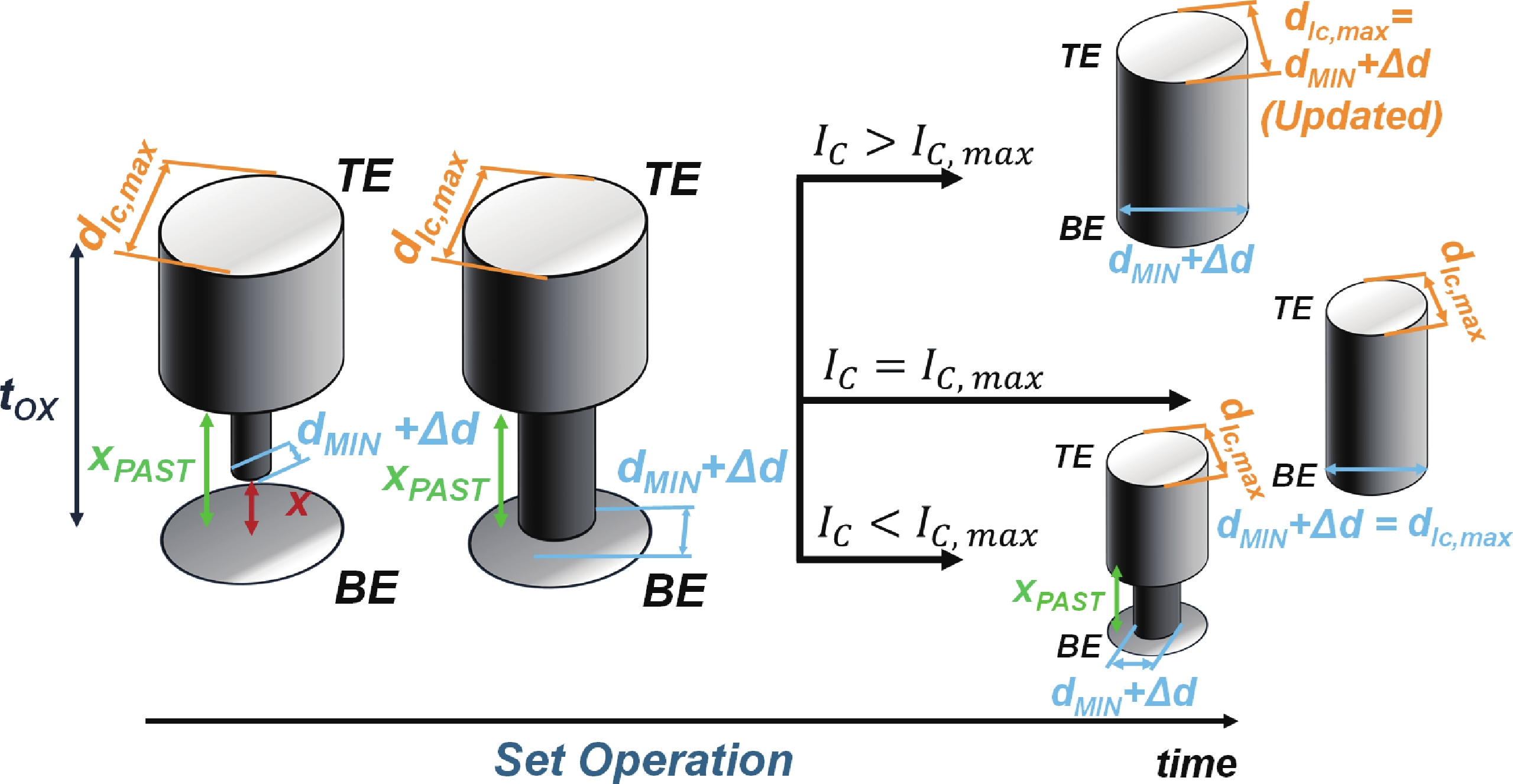

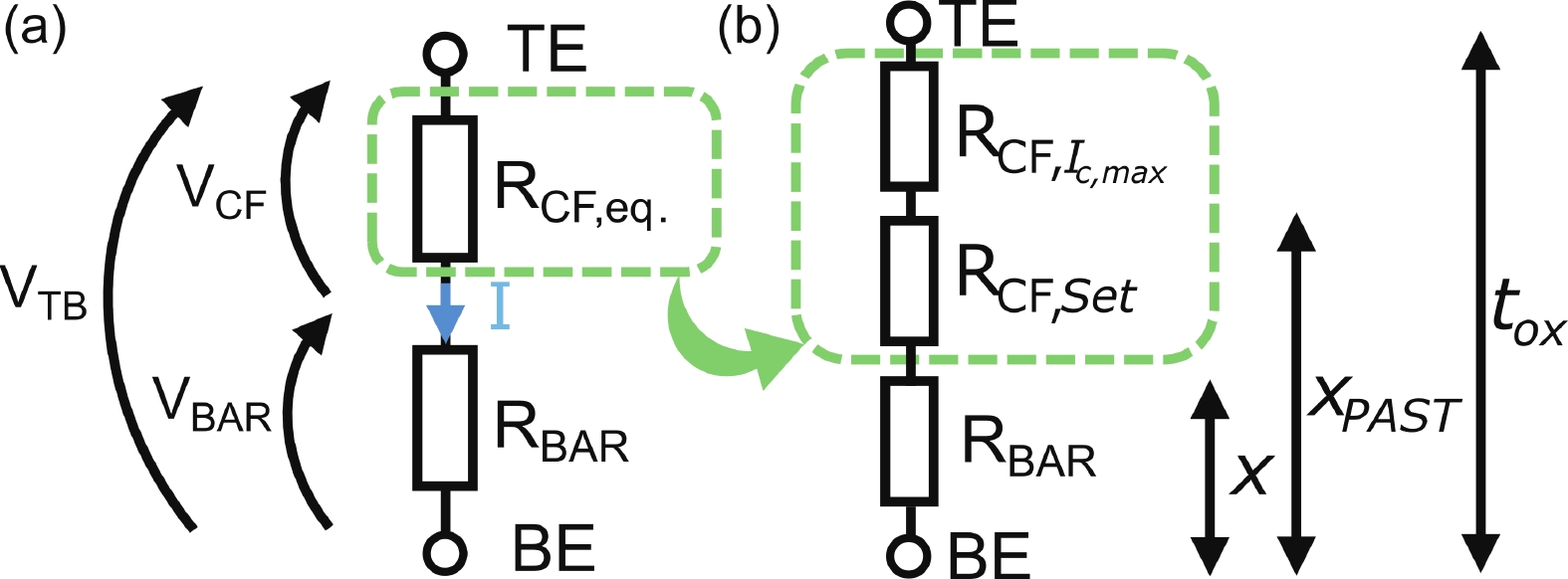

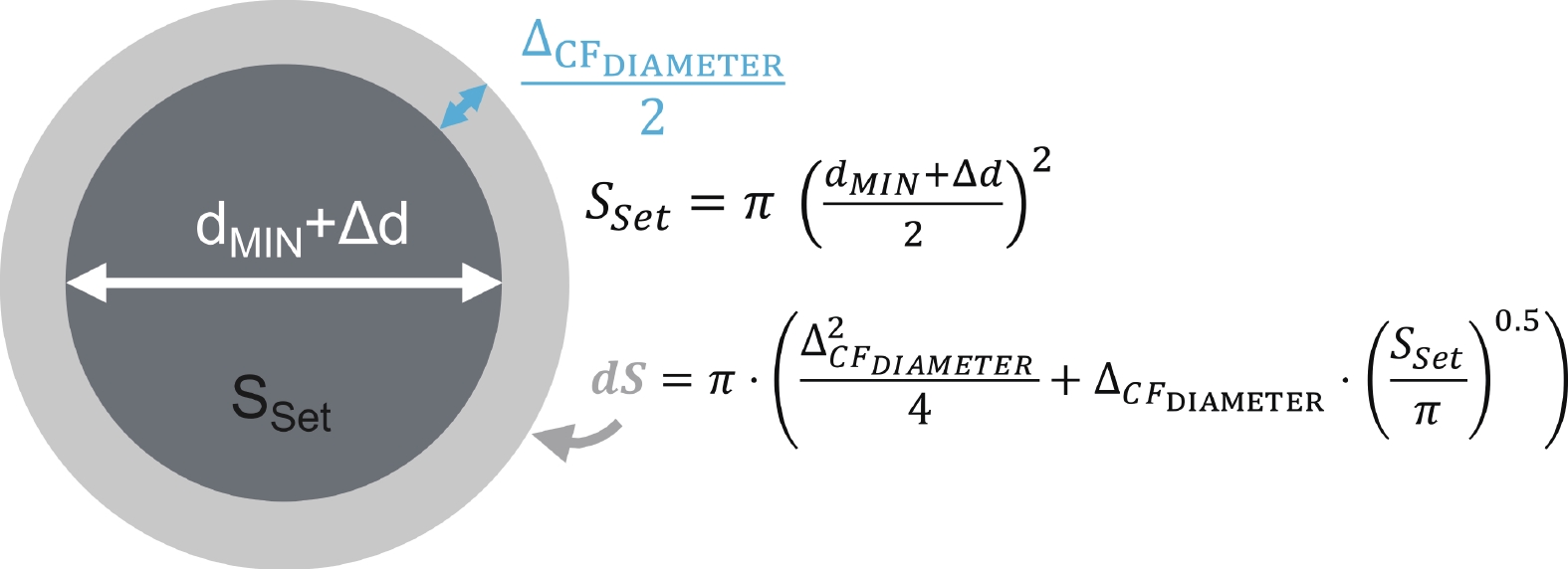

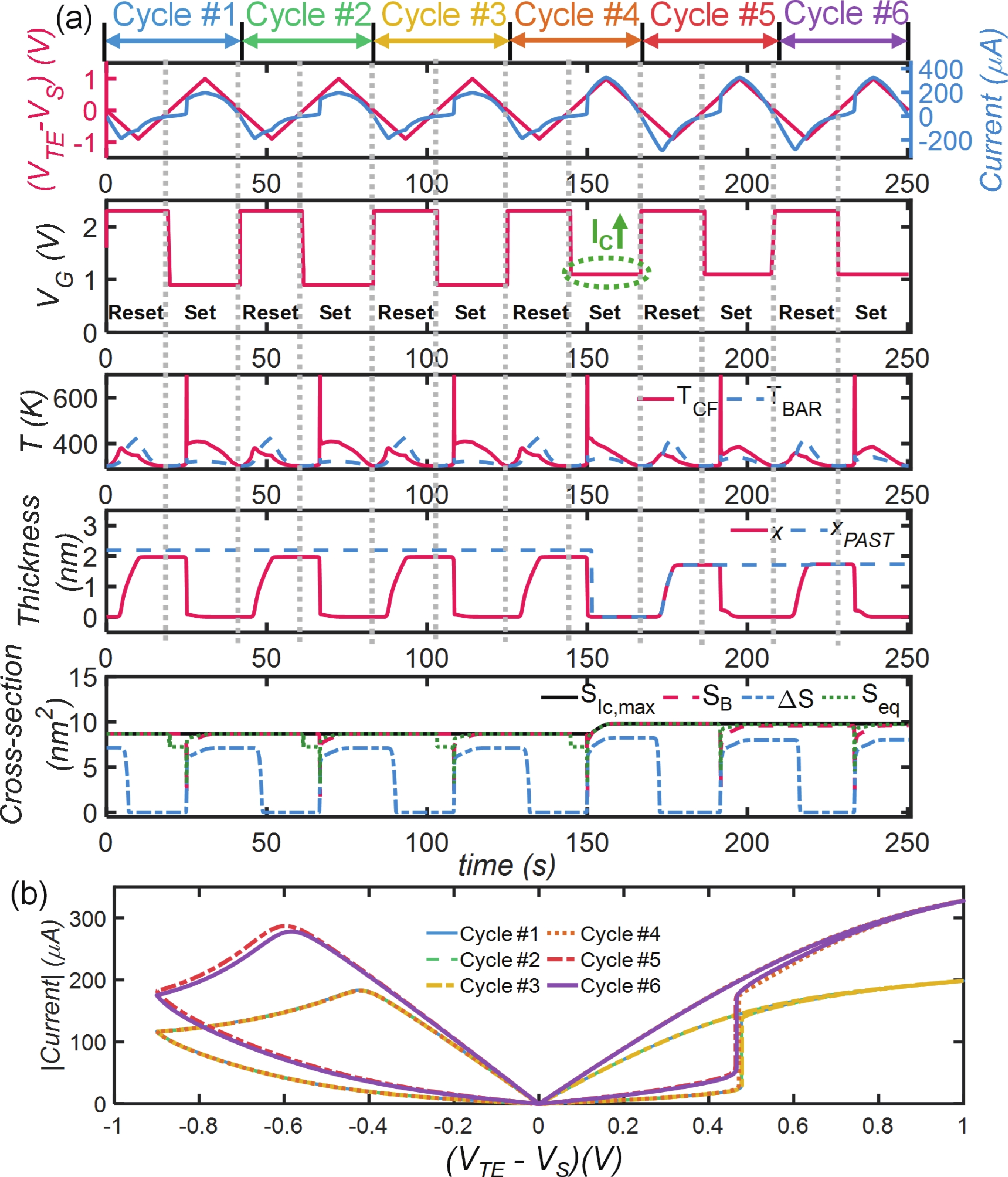

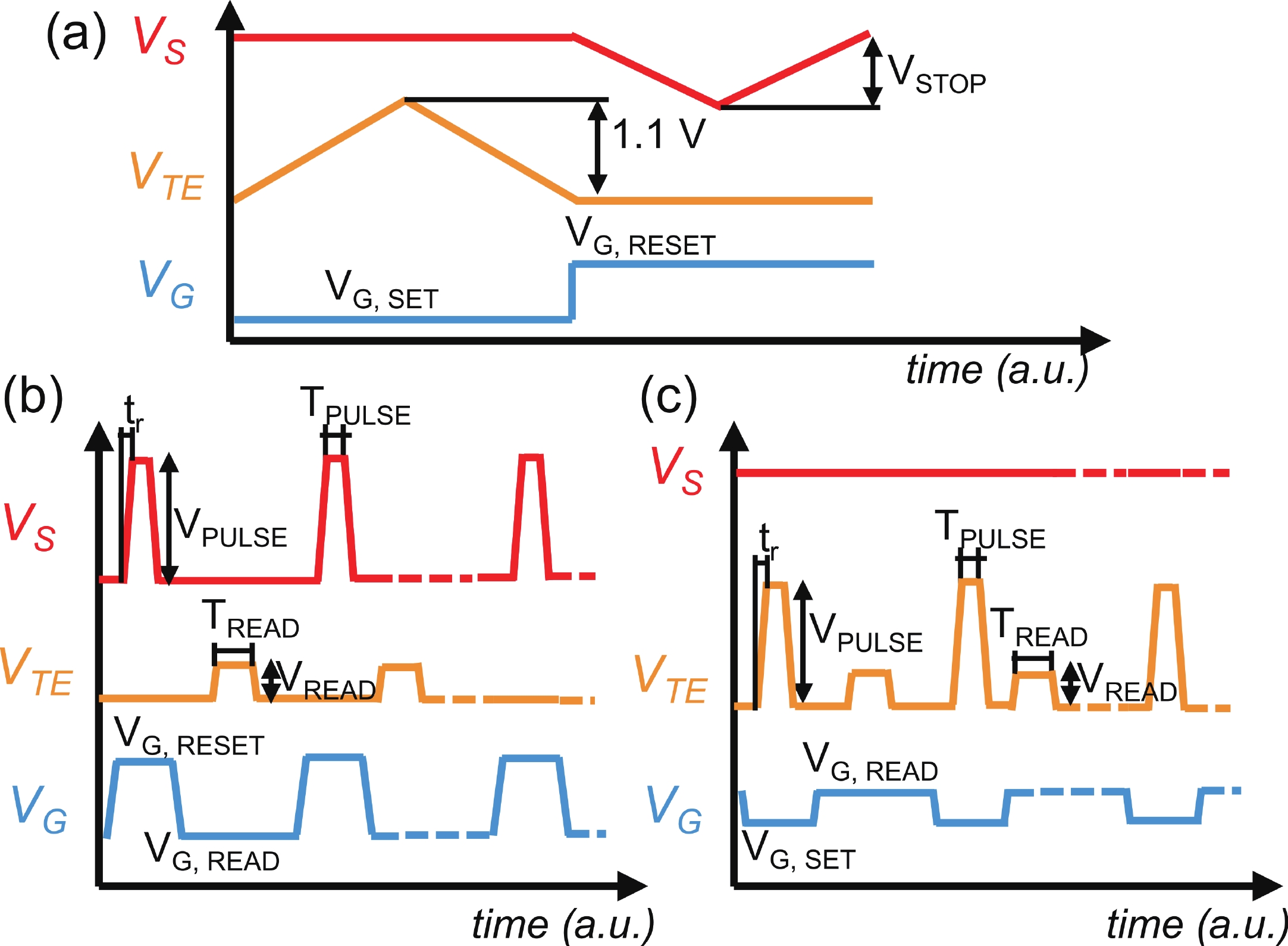

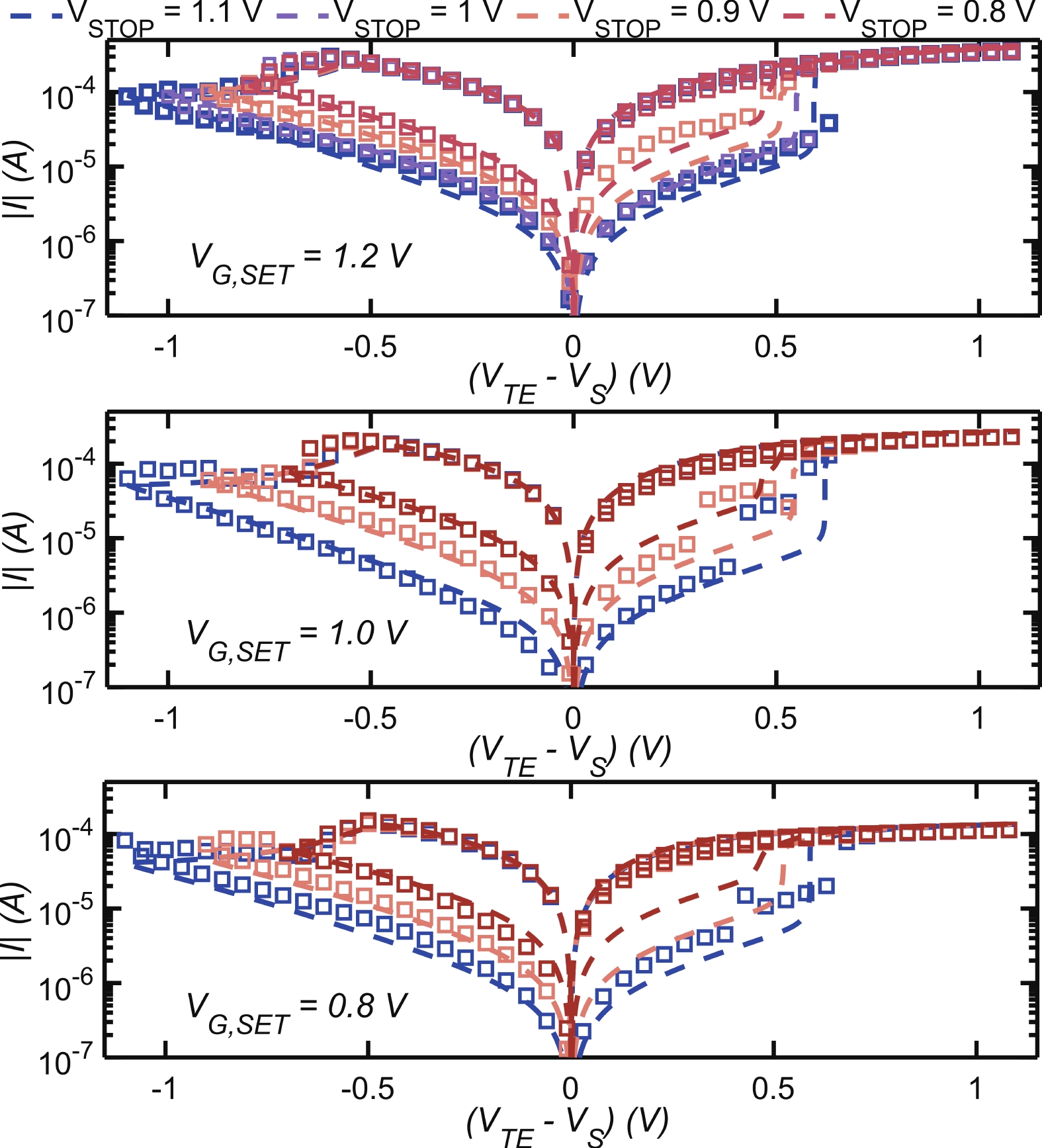

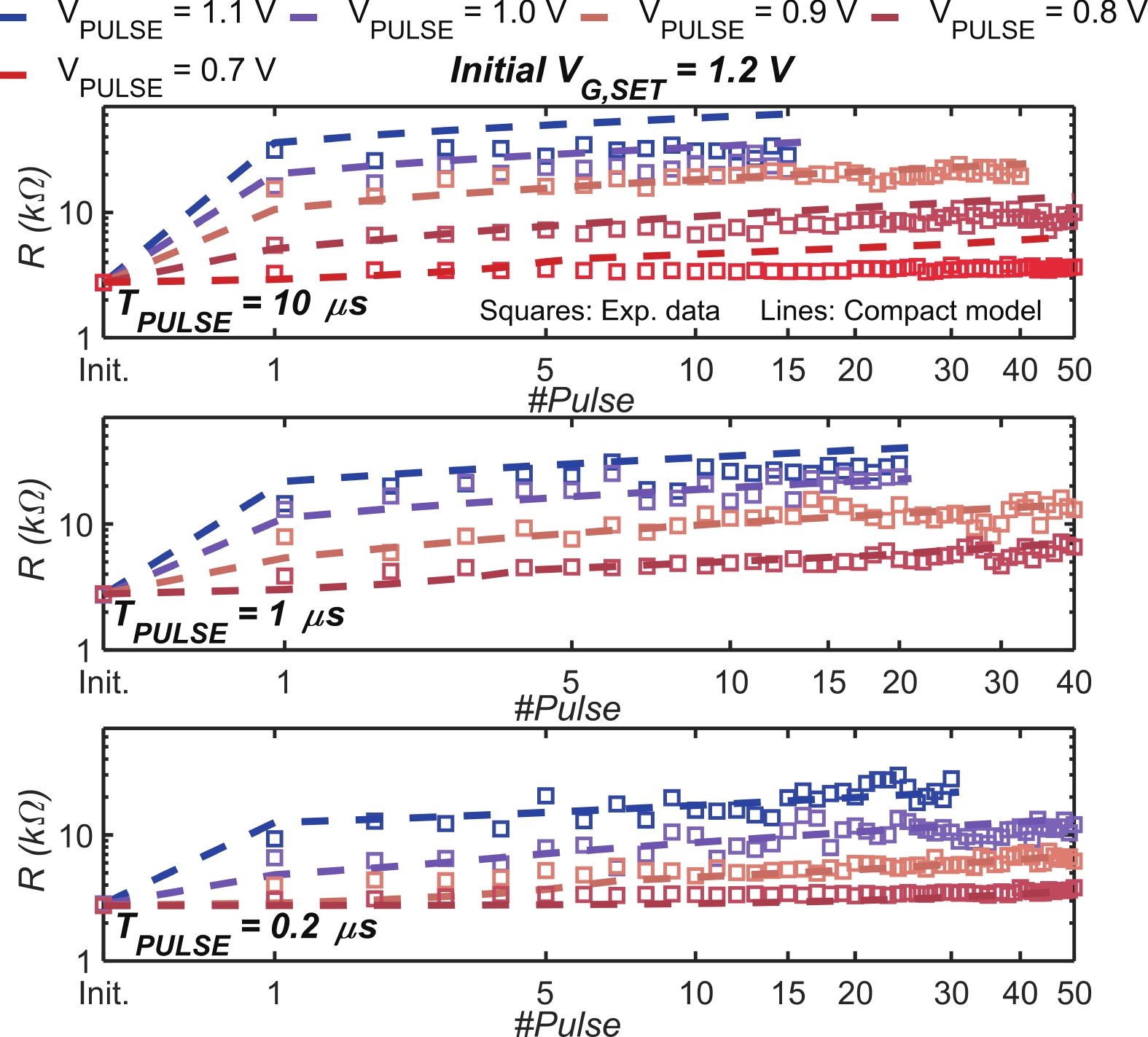

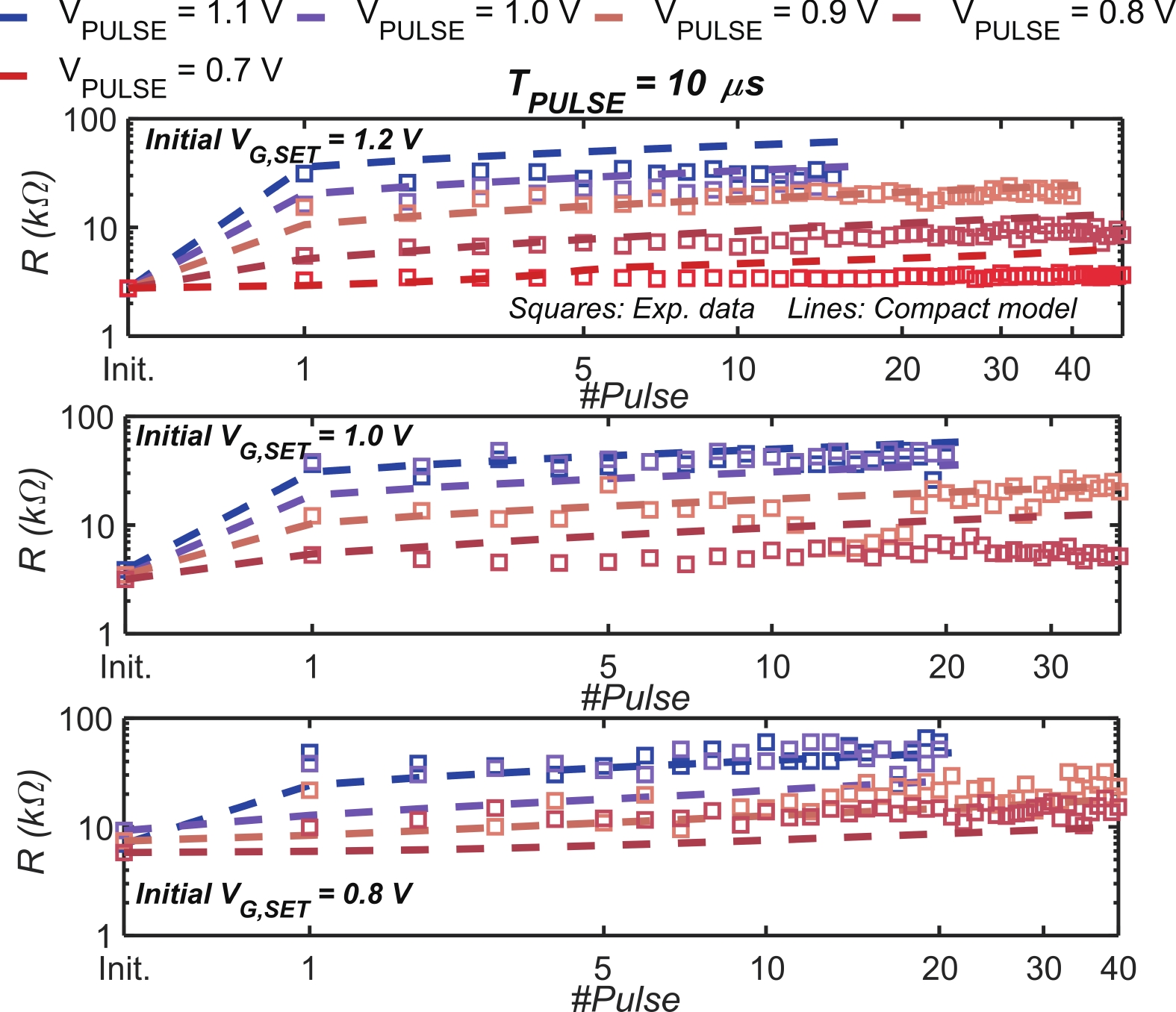

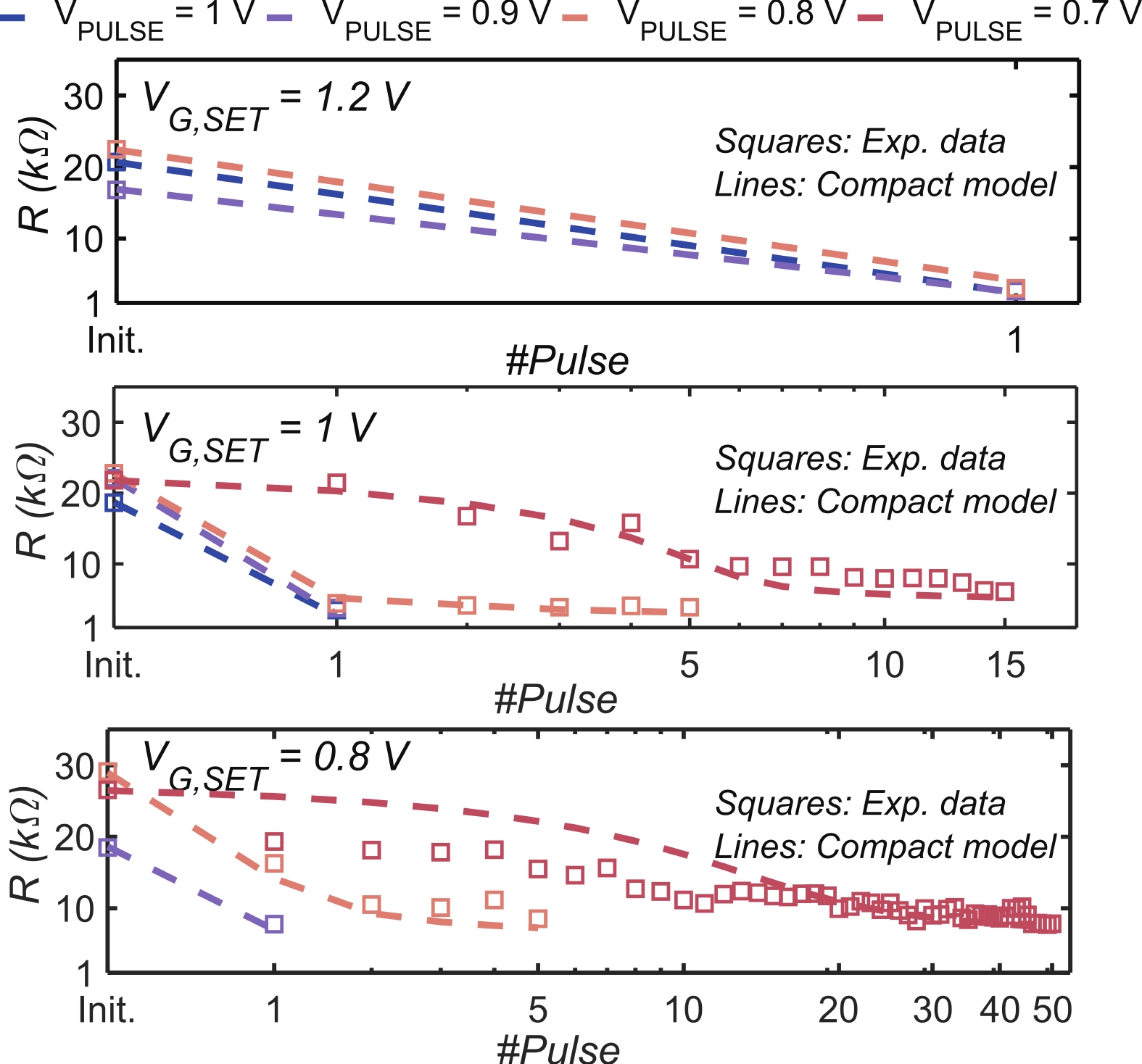

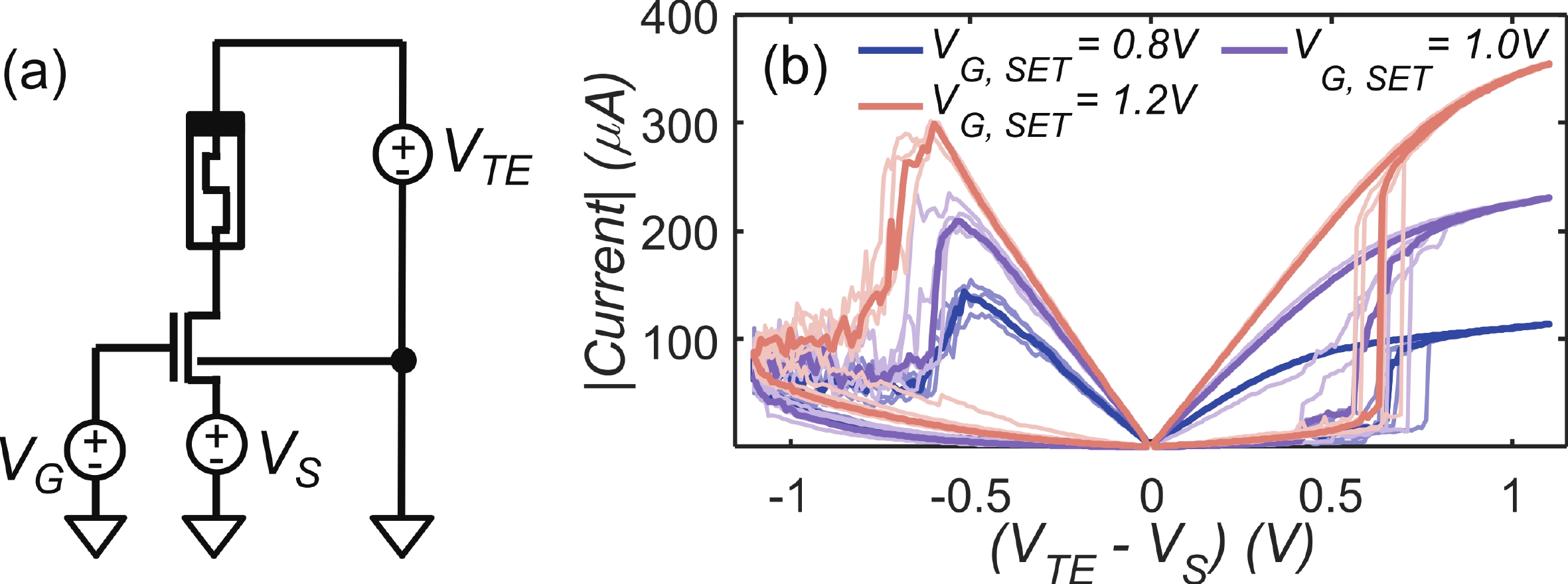

Resistive Random Access Memories (RRAMs) are emerging as a key enabling technology for cost-effective, energy-efficient and secure chips, especially in the framework of edge computing. In particular, their electrically programmable resistance has been widely exploited in several in-memory computing and neuromorphic architectures. By adjusting the applied voltages and compliance currents (IC), RRAM devices can be programmed to multiple resistance states during set and reset procedures, enabling multilevel functionality. While the multilevel behavior of the reset phase is generally well captured by existing compact models, only a few account for the multilevel characteristics of the set operations. Moreover, such models are rarely validated against comprehensive experimental datasets capturing device dynamics across multiple timescales. In this work, we present a physics-based compact model that enhances the UniMORE RRAM framework by incorporating the dynamic lateral evolution of the conductive filament (CF), thereby enabling accurate simulation of set operations at varying IC values. The model is calibrated to experimental data from IHP 130 nm 1T1R RRAM technology and reproduces device behavior across several operating conditions using a single set of parameters. The results highlight the potential of the proposed compact model in design optimization workflows of RRAM-based circuits.-

Keywords:

- RRAM,

- compact model,

- multilevel,

- conductive filament

-

References

[1] Lanza M, Sebastian A, Lu W D, et al. Memristive technologies for data storage, computation, encryption, and radio-frequency communication. Science, 2022, 376(6597): eabj9979 doi: 10.1126/science.abj9979[2] Wong H S P, Lee H Y, Yu S, et al. Metal–oxide RRAM. Proc IEEE, 2012, 100(6): 1951 doi: 10.1109/JPROC.2012.2190369[3] Krestinskaya O, James A P, Chua L O. Neuromemristive circuits for edge computing: A review. IEEE Trans Neural Netw Learn Syst, 2020, 31(1): 4 doi: 10.1109/TNNLS.2019.2899262[4] Wang Z, Song Y, Zhang G, et al. Advances of embedded resistive random access memory in industrial manufacturing and its potential applications. Int J Extreme Manuf, 2024, 6(3): 032006 doi: 10.1088/2631-7990/ad2fea[5] Wang Z, Wu H, Burr G W, et al. Resistive switching materials for information processing. Nat Rev Mater, 2020, 5(3): 173[6] Zahoor F, Azni Zulkifli T Z, Khanday F A. Resistive random access memory (RRAM): An overview of materials, switching mechanism, performance, multilevel cell (mlc) storage, modeling, and applications. Nanoscale Res Lett, 2020, 15(1): 90 doi: 10.1186/s11671-020-03299-9[7] Giordano M, Prabhu K, Koul K, et al. CHIMERA: A 0.92 TOPS, 2.2 TOPS/W edge AI accelerator with 2 MByte on-chip foundry resistive RAM for efficient training and inference. 2021 Symposium on VLSI Circuits, 2021: 1[8] Yu S, Wu Y, Chai Y, et al. Characterization of switching parameters and multilevel capability in HfOx/AlOx bi-layer RRAM devices. Proceedings of 2011 International Symposium on VLSI Technology, Systems and Applications, 2011: 1[9] Milo V, Zambelli C, Olivo P, et al. Multilevel HfO2-based RRAM devices for low-power neuromorphic networks. APL Mater, 2019, 7(8): 081120 doi: 10.1063/1.5108650[10] Zanotti T, Puglisi F M, Pavan P. Reliability and performance analysis of logic-in-memory based binarized neural networks. IEEE Trans Device Mater Reliab, 2021, 21(2): 183 doi: 10.1109/TDMR.2021.3075200[11] Milo V, Pedretti G, Laudato M, et al. Resistive switching synapses for unsupervised learning in feed-forward and recurrent neural networks. 2018 IEEE International Symposium on Circuits and Systems (ISCAS), 2018: 1[12] Panda D, Sahu P P, Tseng T Y. A collective study on modeling and simulation of resistive random access memory. Nanoscale Res Lett, 2018, 13(1): 8 doi: 10.1186/s11671-017-2419-8[13] Aguirre F L, Suñé J, Miranda E. SPICE implementation of the dynamic memdiode model for bipolar resistive switching devices. Micromachines, 2022, 13(2): 330 doi: 10.3390/mi13020330[14] Zanotti T, Pavan P, Puglisi F M. Comprehensive physics-based RRAM compact model including the effect of variability and multi-level random telegraph noise. Microelectron Eng, 2022, 266: 111886 doi: 10.1016/j.mee.2022.111886[15] Li H, Jiang Z, Huang P, et al. Variation-aware, reliability-emphasized design and optimization of RRAM using SPICE model. 2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2015: 1425[16] Bocquet M, Deleruyelle D, Aziza H, et al. Robust compact model for bipolar oxide-based resistive switching memories. IEEE Trans Electron Devices, 2014, 61(3): 674 doi: 10.1109/TED.2013.2296793[17] Hardtdegen A, La Torre C, Cüppers F, et al. Improved switching stability and the effect of an internal series resistor in HfO2/TiOx bilayer ReRAM cells. IEEE Trans Electron Devices, 2018, 65(8): 3229 doi: 10.1109/TED.2018.2849872[18] González-Cordero G, Roldan J B, Jiménez-Molinos F, et al. A new compact model for bipolar RRAMs based on truncated-cone conductive filaments: A Verilog-A approach. Semicond Sci Technol, 2016, 31(11): 115013 doi: 10.1088/0268-1242/31/11/115013[19] Pérez-Bosch Quesada E, Romero-Zaliz R, Pérez E, et al. Toward reliable compact modeling of multilevel 1T-1R RRAM devices for neuromorphic systems. Electronics, 2021, 10(6): 645 doi: 10.3390/electronics10060645[20] Reuben J, Fey D, Wenger C. A modeling methodology for resistive RAM based on Stanford-PKU model with extended multilevel capability. IEEE Trans Nanotechnol, 2019, 18: 647 doi: 10.1109/TNANO.2019.2922838[21] Jiang Z, Wu Y, Yu S, et al. A compact model for metal–oxide resistive random access memory with experiment verification. IEEE Trans Electron Devices, 2016, 63(5): 1884 doi: 10.1109/TED.2016.2545412[22] Zanotti T, Pavan P, Puglisi F M. Self-consistent automated parameter extraction of RRAM physics-based compact model. ESSDERC 2022 - IEEE 52nd European Solid-State Device Research Conference (ESSDERC), 2022: 316[23] Puglisi F M, Larcher L, Padovani A, et al. Bipolar resistive RAM based on HfO2: Physics, compact modeling, and variability control. IEEE J Emerg Sel Top Circuits Syst, 2016, 6(2): 171 doi: 10.1109/JETCAS.2016.2547703[24] Baroni A, Pérez E, Dorai Swamy Reddy K, et al. Enhancing RRAM reliability: Exploring the effects of Al doping on HfO2-based devices. IEEE Trans Device Mater Reliab, 2025, 25(3): 379 doi: 10.1109/TDMR.2025.3581061[25] Patterson G A, Suñé J, Miranda E. Voltage-driven hysteresis model for resistive switching: SPICE modeling and circuit applications. IEEE Trans Comput Aided Des Integr Circuits Syst, 2017, 36(12): 2044 doi: 10.1109/TCAD.2017.2756561[26] McAndrew C C, Coram G J, Gullapalli K K, et al. Best practices for compact modeling in Verilog-A. IEEE J Electron Devices Soc, 2015, 3(5): 383 doi: 10.1109/JEDS.2015.2455342[27] Wang T. Modelling multistability and hysteresis in ESD clamps, memristors and other devices. 2017 IEEE Custom Integrated Circuits Conference (CICC), 2017: 1[28] Liu X, Bengel C, Cüppers F, et al. Effect of transistor transfer characteristics on the programming process in 1T1R configuration. IEEE Trans Electron Devices, 2024, 71(4): 2423 doi: 10.1109/TED.2024.3370536[29] Uhlmann M, Rizzi T, Wen J, et al. LUT-based RRAM model for neural accelerator circuit simulation. Proceedings of the 18th ACM International Symposium on Nanoscale Architectures. Dresden, Germany. ACM, 2024: 1[30] Jiménez-Molinos F, Vinuesa G, García H, et al. Thermal dependence of the current in TiN/Ti/HfO2/W memristors at different intermediate conduction states. Mater Sci Semicond Process, 2024, 179: 108480 doi: 10.1016/j.mssp.2024.108480 -

Proportional views

Tommaso Zanotti received the Ph.D. degree in information and communication technology from the University of Modena and Reggio Emilia, Modena, Italy, in 2022, where he is currently an Assistant Professor of electronics. His research interests include the compact modeling of emerging nonvolatile memory technologies, and the design of energy-efficient computing architectures and hardware security primitives. He was a co-recipient of the Best Paper Award at IEEE European Solid-State Device Research Conference (ESSDERC) 2019, the Best Student Paper Award at the IEEE IIRW 2020, and the Journal of Low Power Electronics and Applications (JLPEA) Travel Award 2021.

Tommaso Zanotti received the Ph.D. degree in information and communication technology from the University of Modena and Reggio Emilia, Modena, Italy, in 2022, where he is currently an Assistant Professor of electronics. His research interests include the compact modeling of emerging nonvolatile memory technologies, and the design of energy-efficient computing architectures and hardware security primitives. He was a co-recipient of the Best Paper Award at IEEE European Solid-State Device Research Conference (ESSDERC) 2019, the Best Student Paper Award at the IEEE IIRW 2020, and the Journal of Low Power Electronics and Applications (JLPEA) Travel Award 2021. Tommaso Rizzi received the M.Sc. degree in Electronics and Telecommunication Engineering from the University of Ferrara, Italy, in 2020, and the Ph.D. degree in Electrical Engineering from BTU Cottbus-Senftenberg, Germany, in 2024. He is currently a Postdoctoral Researcher at IHP – Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany. His research focuses on neuromorphic computing and memristive device technologies.

Tommaso Rizzi received the M.Sc. degree in Electronics and Telecommunication Engineering from the University of Ferrara, Italy, in 2020, and the Ph.D. degree in Electrical Engineering from BTU Cottbus-Senftenberg, Germany, in 2024. He is currently a Postdoctoral Researcher at IHP – Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany. His research focuses on neuromorphic computing and memristive device technologies. Emilio Pérez-Bosch Quesada Emilio Perez-Bosch Quesada is a researcher specializing in the electrical characterization and modeling of HfO2-based resistive random-access memory (RRAM) devices for advanced computing applications. He earned his Bachelor's degree in Telecommunication Engineering from the University of Jaén, Spain, in 2017. In 2019, he completed a double Master's degree in Telecommunication Engineering from the University of Jaén and the Technische Hochschule Mittelhessen (THM) in Germany, where he was awarded the Best Master's Thesis Award. He pursued his PhD at IHP – Leibniz Institute for High Performance Microelectronics in Frankfurt (Oder), Germany, focusing on the electrical characterization and modeling of HfO2-based RRAM devices for neuromorphic computing. After receiving his PhD in July 2024, his research has expanded to evaluating RRAM technology under harsh environmental conditions, with the goal of enabling in-memory computing for space applications and quantum computing.

Emilio Pérez-Bosch Quesada Emilio Perez-Bosch Quesada is a researcher specializing in the electrical characterization and modeling of HfO2-based resistive random-access memory (RRAM) devices for advanced computing applications. He earned his Bachelor's degree in Telecommunication Engineering from the University of Jaén, Spain, in 2017. In 2019, he completed a double Master's degree in Telecommunication Engineering from the University of Jaén and the Technische Hochschule Mittelhessen (THM) in Germany, where he was awarded the Best Master's Thesis Award. He pursued his PhD at IHP – Leibniz Institute for High Performance Microelectronics in Frankfurt (Oder), Germany, focusing on the electrical characterization and modeling of HfO2-based RRAM devices for neuromorphic computing. After receiving his PhD in July 2024, his research has expanded to evaluating RRAM technology under harsh environmental conditions, with the goal of enabling in-memory computing for space applications and quantum computing. Andrea Baroni received his M.Sc. Degree in Electronic Engineering for ICT from the University of Ferrara, Italy, in 2021. He is currently pursuing a Ph.D. degree at BTU Cottbus-Senftenberg, Germany. He is also working as researcher at IHP - Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany. His main research interest includes the reliability analysis and electrical characterization of memristive devices (RRAM), with a focus on emerging memory and neuromorphic application.

Andrea Baroni received his M.Sc. Degree in Electronic Engineering for ICT from the University of Ferrara, Italy, in 2021. He is currently pursuing a Ph.D. degree at BTU Cottbus-Senftenberg, Germany. He is also working as researcher at IHP - Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany. His main research interest includes the reliability analysis and electrical characterization of memristive devices (RRAM), with a focus on emerging memory and neuromorphic application. Keerthi Dorai Swamy Reddy received the M.Sc. degree in Nanoelectronic Systems from TU Dresden, Germany in 2017. She worked in the field of atomic layer deposition of thin films at TU Dresden from 2017 to 2018 and at IMEC, Belgium from 2018 to 2020. From 2020 to 2022, she worked as a Senior Process Engineer at Picosun Oy (Applied Materials). She is currently pursuing a PhD degree and working as a researcher at the IHP GmbH – Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany for developing CMOS-compatible processes for memristive devices applications.

Keerthi Dorai Swamy Reddy received the M.Sc. degree in Nanoelectronic Systems from TU Dresden, Germany in 2017. She worked in the field of atomic layer deposition of thin films at TU Dresden from 2017 to 2018 and at IMEC, Belgium from 2018 to 2020. From 2020 to 2022, she worked as a Senior Process Engineer at Picosun Oy (Applied Materials). She is currently pursuing a PhD degree and working as a researcher at the IHP GmbH – Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany for developing CMOS-compatible processes for memristive devices applications. Eduardo Pérez Eduardo Perez received the M.Sc. and Ph.D. degrees in information and communications technologies from the University of Valladolid, Valladolid, Spain, in 2010 and 2014, respectively. He has been with the IHP–Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany, since 2015, where he has worked in the field of electrical characterization of RRAM devices for their implementation as Non-Volatile Memories and artificial synapses in Neuromorphic Computing applications. In 2022, he received the German Habilitation and the position of “Privat-Dozent” at Brandenburg Technical University (BTU) Cottbus-Senftenberg.

Eduardo Pérez Eduardo Perez received the M.Sc. and Ph.D. degrees in information and communications technologies from the University of Valladolid, Valladolid, Spain, in 2010 and 2014, respectively. He has been with the IHP–Leibniz Institute for High Performance Microelectronics, Frankfurt (Oder), Germany, since 2015, where he has worked in the field of electrical characterization of RRAM devices for their implementation as Non-Volatile Memories and artificial synapses in Neuromorphic Computing applications. In 2022, he received the German Habilitation and the position of “Privat-Dozent” at Brandenburg Technical University (BTU) Cottbus-Senftenberg. Christian Wenger received the Diploma in physics from the University of Konstanz, in 1995 and the Ph.D. degree from the Technical University of Dresden, in 2000. Since 2002, he has been with IHP – Leibniz institute for high performance microelectronics, where he works in the field of device and materials innovations for microelectronics. In 2009, he received the post-doctoral degree at TU Dresden. 2018, he received the professorship “Microelectronics for medical engineering” at Brandenburg Medical School Theodor Fontane. In 2020, he received the professorship “Semiconductor materials” at BTU-Cottbus-Senftenberg and is leading the department “Materials Research” at IHP.

Christian Wenger received the Diploma in physics from the University of Konstanz, in 1995 and the Ph.D. degree from the Technical University of Dresden, in 2000. Since 2002, he has been with IHP – Leibniz institute for high performance microelectronics, where he works in the field of device and materials innovations for microelectronics. In 2009, he received the post-doctoral degree at TU Dresden. 2018, he received the professorship “Microelectronics for medical engineering” at Brandenburg Medical School Theodor Fontane. In 2020, he received the professorship “Semiconductor materials” at BTU-Cottbus-Senftenberg and is leading the department “Materials Research” at IHP. Paolo Pavan received the Ph.D. degree in electrical engineering from the University of Padova, Padua, Italy, in 1994. He is currently a Full Professor of electronics with the University of Modena and Reggio Emilia, Modena, Italy. He is currently Rectors Delegate for Scientific Research. His research interests include the characterization, modeling, and optimization of nonvolatile resistive memories (RRAMs), logic-in-memory and neuromorphic architecture, and the development of safety critical and energy-aware applications for low-power computing and automotive electronics. Mr. Pavan was on the Technical Committee of IEEE IEDM, VLSI-TSA, IEEE IRPS, IEEE ESSDERC (TPC in 2014), and ESREF. He was the Guest Editor of IEEE Transactions On Device and Materials Reliability and Associate Editor for IEEE Journal of Electron Devices Society.

Paolo Pavan received the Ph.D. degree in electrical engineering from the University of Padova, Padua, Italy, in 1994. He is currently a Full Professor of electronics with the University of Modena and Reggio Emilia, Modena, Italy. He is currently Rectors Delegate for Scientific Research. His research interests include the characterization, modeling, and optimization of nonvolatile resistive memories (RRAMs), logic-in-memory and neuromorphic architecture, and the development of safety critical and energy-aware applications for low-power computing and automotive electronics. Mr. Pavan was on the Technical Committee of IEEE IEDM, VLSI-TSA, IEEE IRPS, IEEE ESSDERC (TPC in 2014), and ESREF. He was the Guest Editor of IEEE Transactions On Device and Materials Reliability and Associate Editor for IEEE Journal of Electron Devices Society. Francesco Maria Puglisi received the Ph.D. degree in information and communication technology from the University of Modena and Reggio Emilia, Modena, Italy, in 2015, at which he currently is Associate Professor of electronics. His activity concerns the characterization and compact modeling of novel nonvolatile memories, focusing on noise, reliability, and variability. He is also interested in the design of new circuit paradigms for low-power and brain-inspired computing. He has authored or coauthored more than 140 technical papers. Prof. Puglisi was a co-recipient of the Best Student Paper Award at the IEEE International Conference on IC Design and Technology (ICICDT) 2013, IEEE International Integrated Reliability Workshop (IIRW) 2020, 2021, and 2023, and IEEE International Reliability Physics Symposium (IRPS) 2022, and the Best Paper Award at IEEE European Solid-State Device Research Conference (ESSDERC) 2016 and 2019. He is an Associate Editor of IEEE Transactions on Electron Devices and of Elsevier’s Microelectronic Engineering Journal. He is active in several technical and/or management committees of prestigious international IEEE conferences, including the International Electron Devices Meeting (IEDM), ESSDERC, IRPS, IIRW. He was the Technical Program Co-Chair of ESSDERC 2022 and the General Chair of IIRW 2023.

Francesco Maria Puglisi received the Ph.D. degree in information and communication technology from the University of Modena and Reggio Emilia, Modena, Italy, in 2015, at which he currently is Associate Professor of electronics. His activity concerns the characterization and compact modeling of novel nonvolatile memories, focusing on noise, reliability, and variability. He is also interested in the design of new circuit paradigms for low-power and brain-inspired computing. He has authored or coauthored more than 140 technical papers. Prof. Puglisi was a co-recipient of the Best Student Paper Award at the IEEE International Conference on IC Design and Technology (ICICDT) 2013, IEEE International Integrated Reliability Workshop (IIRW) 2020, 2021, and 2023, and IEEE International Reliability Physics Symposium (IRPS) 2022, and the Best Paper Award at IEEE European Solid-State Device Research Conference (ESSDERC) 2016 and 2019. He is an Associate Editor of IEEE Transactions on Electron Devices and of Elsevier’s Microelectronic Engineering Journal. He is active in several technical and/or management committees of prestigious international IEEE conferences, including the International Electron Devices Meeting (IEDM), ESSDERC, IRPS, IIRW. He was the Technical Program Co-Chair of ESSDERC 2022 and the General Chair of IIRW 2023.

DownLoad:

DownLoad: