| Citation: |

Yingying Chi, Dongmei Li. A 1.8 V 1.1 MS/s 96.1 dB-SFDR successive approximation register analog-to-digital converter with calibration[J]. Journal of Semiconductors, 2013, 34(4): 045007. doi: 10.1088/1674-4926/34/4/045007

****

Y Y Chi, D M Li. A 1.8 V 1.1 MS/s 96.1 dB-SFDR successive approximation register analog-to-digital converter with calibration[J]. J. Semicond., 2013, 34(4): 045007. doi: 10.1088/1674-4926/34/4/045007.

|

A 1.8 V 1.1 MS/s 96.1 dB-SFDR successive approximation register analog-to-digital converter with calibration

DOI: 10.1088/1674-4926/34/4/045007

More Information

-

Abstract

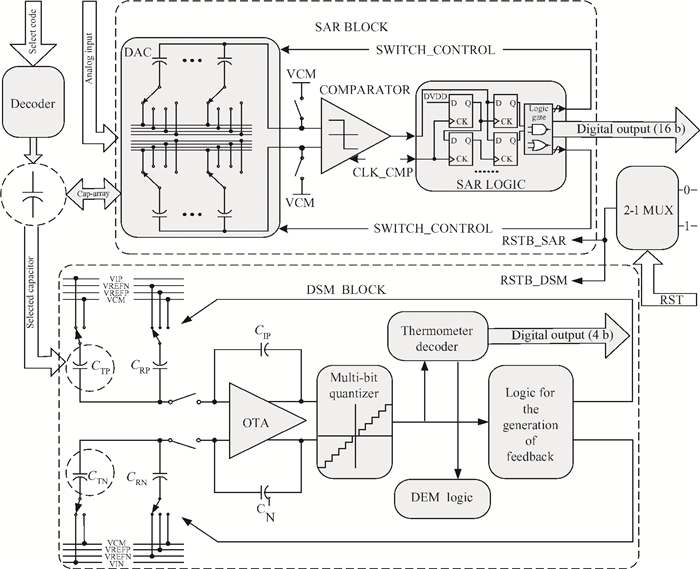

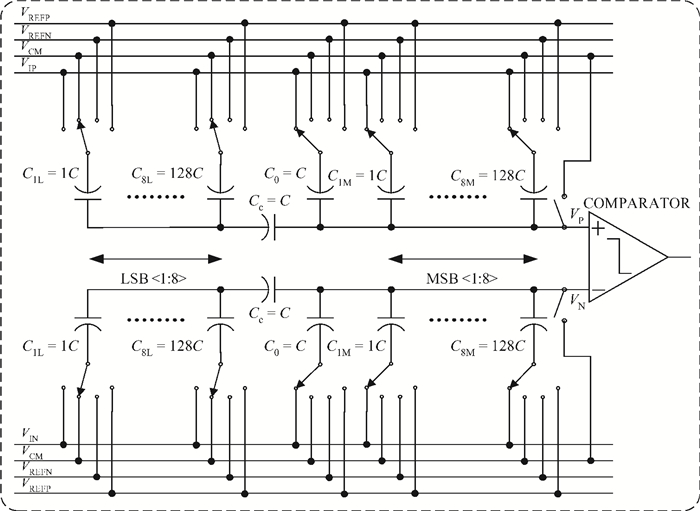

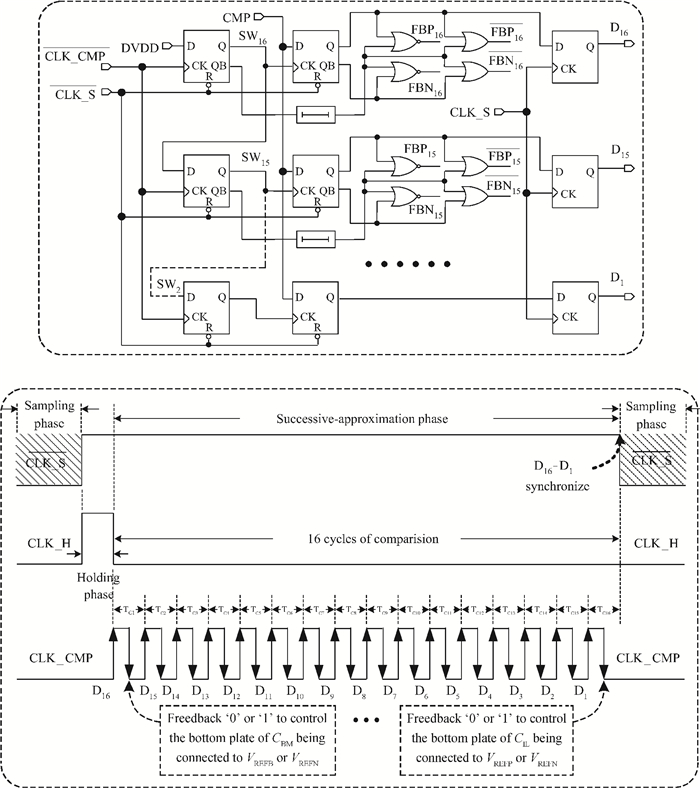

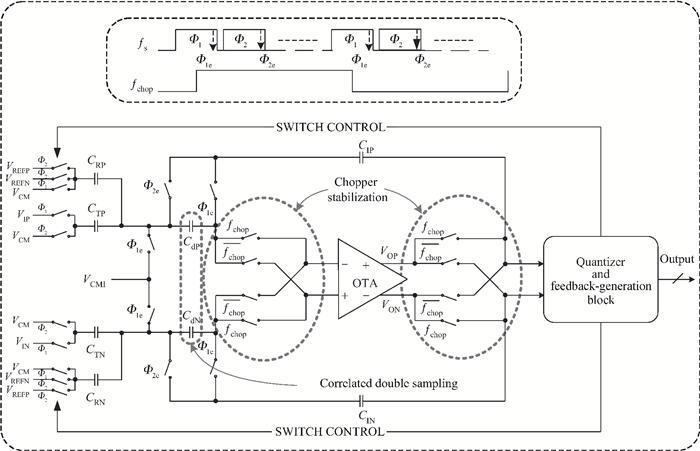

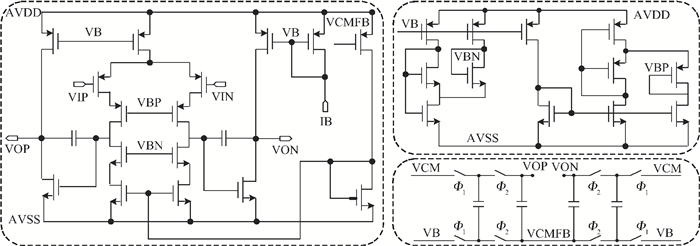

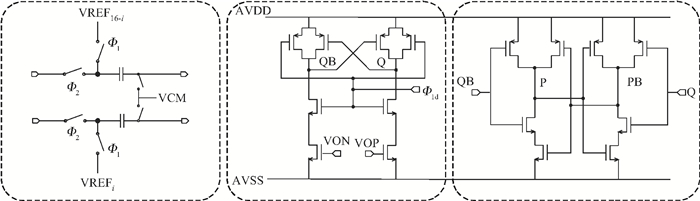

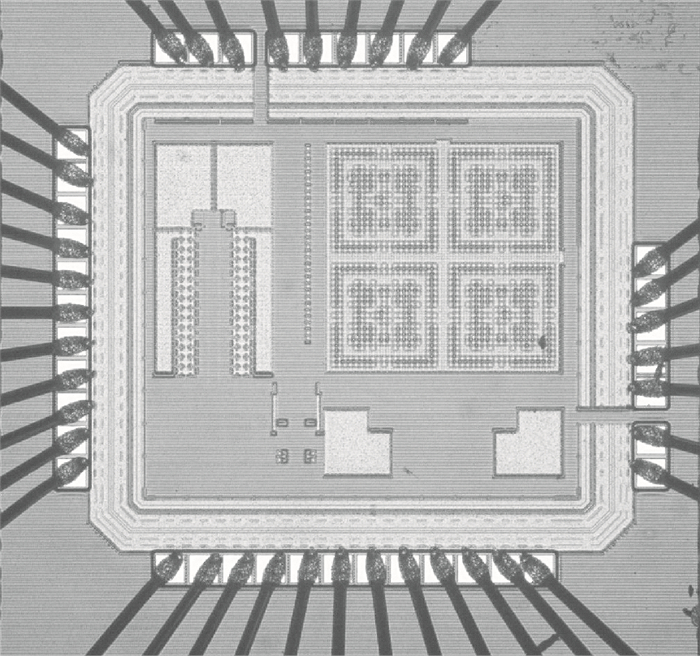

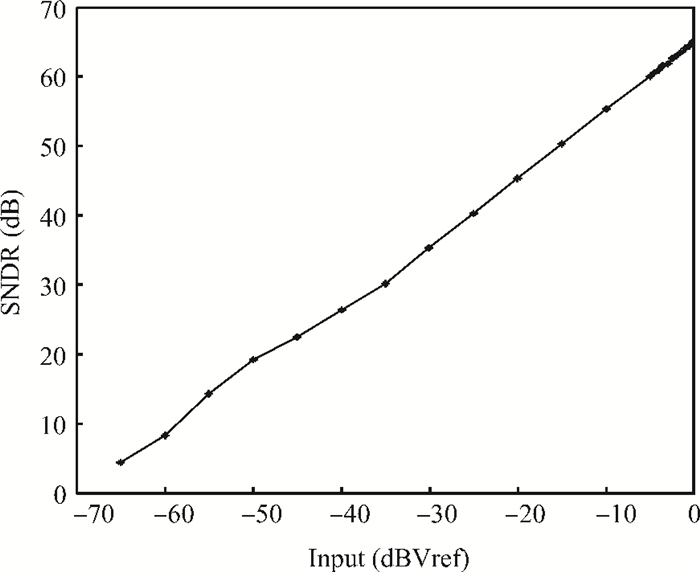

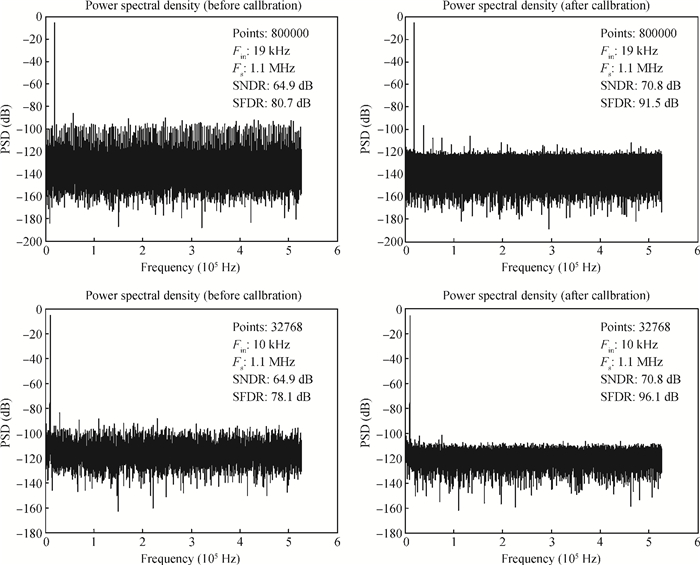

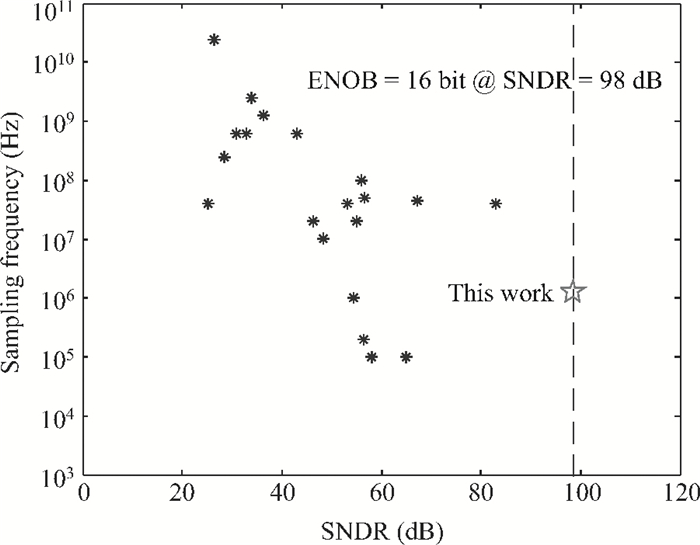

A power efficient 96.1 dB-SFDR successive approximation register (SAR) analog-to-digital converter (ADC) with digital calibration aimed at capacitor mismatch is presented. The prototype is fabricated in a 0.18 μm CMOS. The charge redistribution (CR) design and an extra ΔΣ modulator for capacitance measurement are employed. With a 1.1 MS/s sampling rate, the ADC achieves 70.8 dB SNDR and the power consumption is 2.1 mW.-

Keywords:

- successive approximation register,

- ADC,

- low power,

- calibration

-

References

[1] Sun L, Dai Q, Lee C, et al. Analysis on capacitor mismatch and parasitic capacitors effect of improved segmented-capacitor array in SAR ADC. ⅡTA Third International Symposium on Intelligent Information Technology Application, 2009, 2:280 http://ieeexplore.ieee.org/document/5369251/authors[2] Liu Liyuan, Li Dongmei, Chen Liangdong, et al. A low power 8-bit successive approximation register (SAR) A/D for wireless body sensor node (WBSN). Journal of Semiconductors, 2010, 31(6):065004 doi: 10.1088/1674-4926/31/6/065004[3] Aksin D, Al-Shyoukh M A, Maloberti F. A bootstrapped switch for precise sampling of inputs with signal range beyond supply voltage. IEEE Custom Integrated Circuits Conference, 2005:743 http://dblp.uni-trier.de/db/conf/cicc/cicc2005.html[4] Liu Liyuan, Chen Liangdong, Li Dongmei, et al. A 1.1 mW 87 dB dynamic range ΔΣ modulator for audio applications. Journal of Semiconductors, 2010, 31(5):055003 doi: 10.1088/1674-4926/31/5/055003[5] Schinkel D, Mensink E, Klumperink E, et al. A double-tail latch-type voltage sense amplifier with 18 ps setup+hold time. IEEE International Solid-State Circuits Conference, Digest of Technical Papers, 2007 http://ieeexplore.ieee.org/document/4242391/keywords[6] Baird R T, Fiez T S. Linearity enhancement of multibit ΔΣ A/D and D/A converters using data weighted averaging. IEEE Trans Circuits Syst Ⅱ, 1995, 42(12):753 doi: 10.1109/82.476173 -

Proportional views

DownLoad:

DownLoad: