| Citation: |

Wei Wu, Bo Zhang, Jian Fang, Xiaorong Luo, Zhaoji Li. A high voltage Bi-CMOS compatible buffer super-junction LDMOS with an N-type buried layer[J]. Journal of Semiconductors, 2014, 35(1): 014009. doi: 10.1088/1674-4926/35/1/014009

****

W Wu, B Zhang, J Fang, X R Luo, Z J Li. A high voltage Bi-CMOS compatible buffer super-junction LDMOS with an N-type buried layer[J]. J. Semicond., 2014, 35(1): 014009. doi: 10.1088/1674-4926/35/1/014009.

|

A high voltage Bi-CMOS compatible buffer super-junction LDMOS with an N-type buried layer

DOI: 10.1088/1674-4926/35/1/014009

More Information

-

Abstract

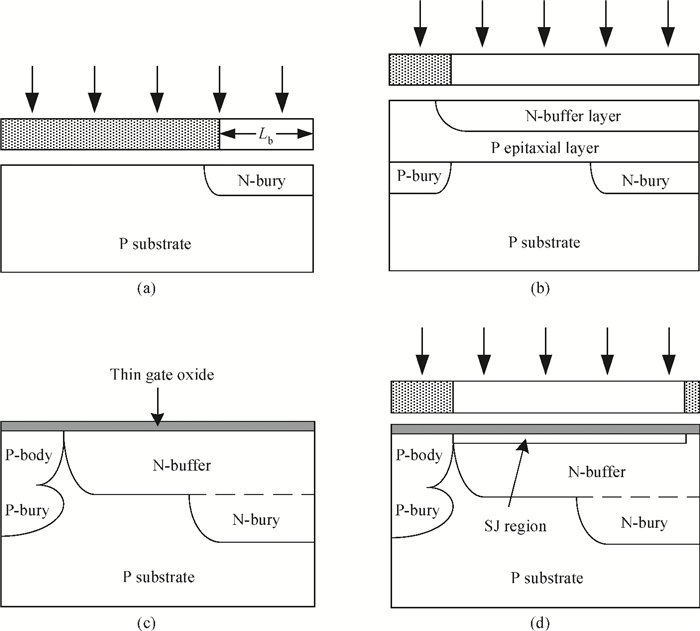

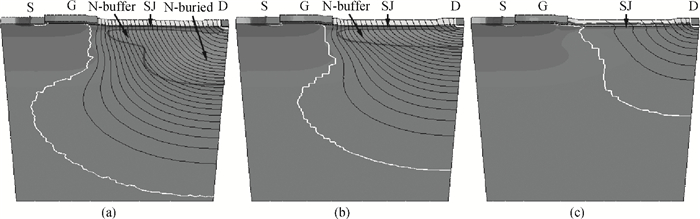

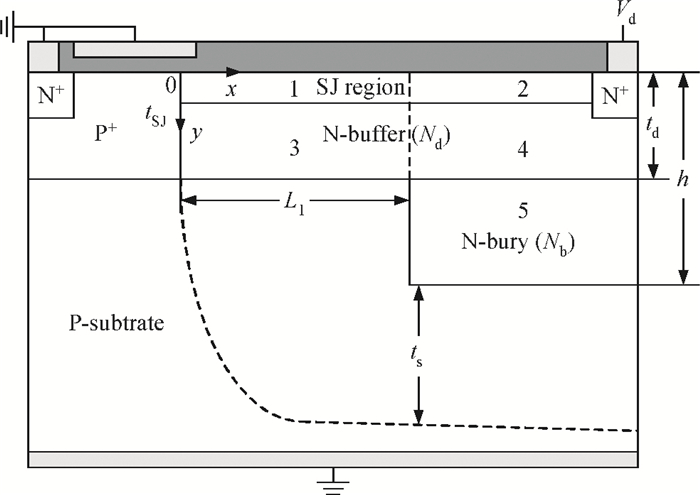

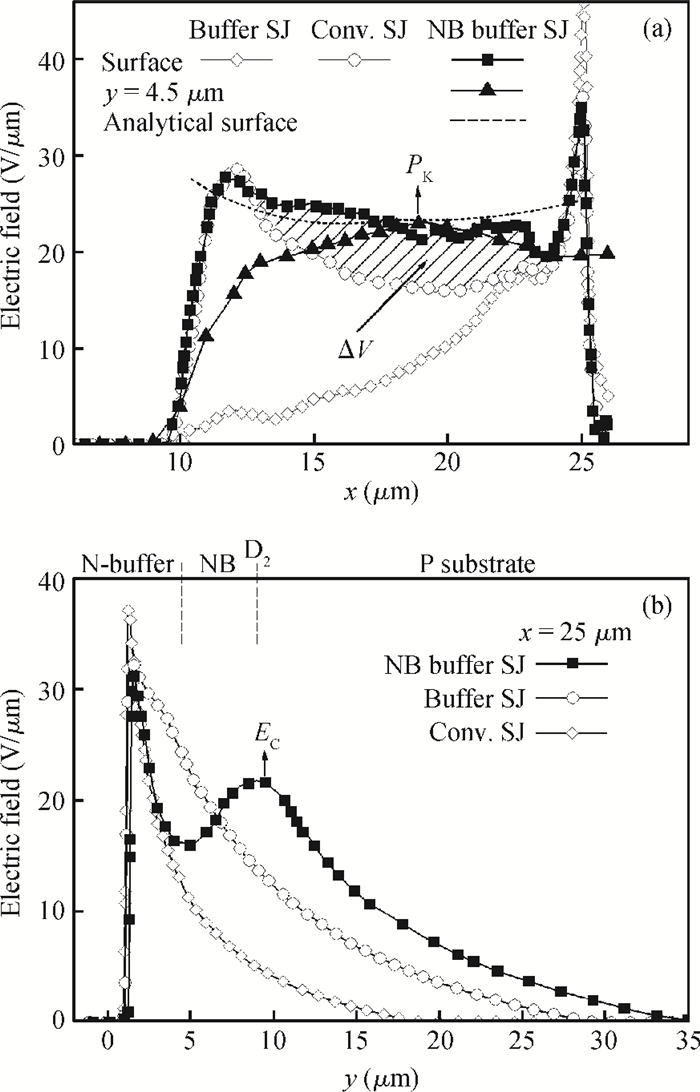

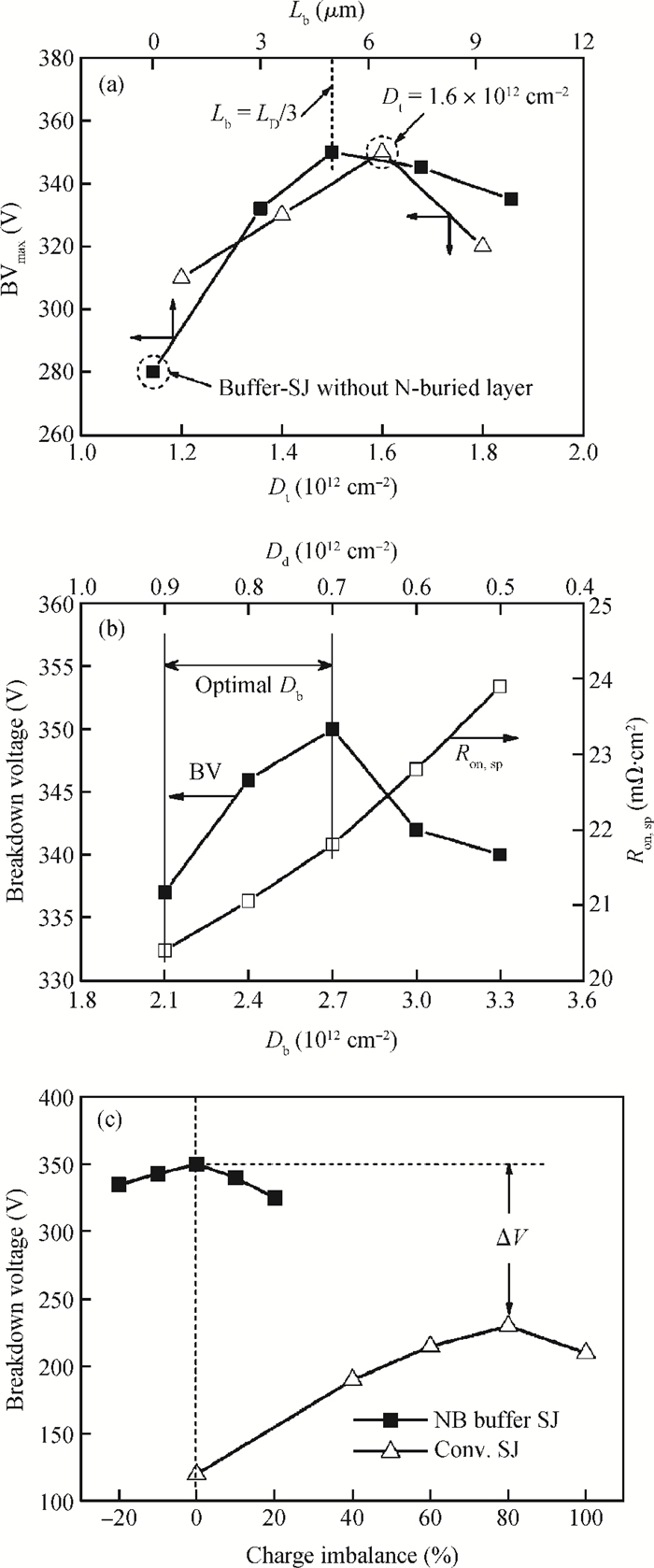

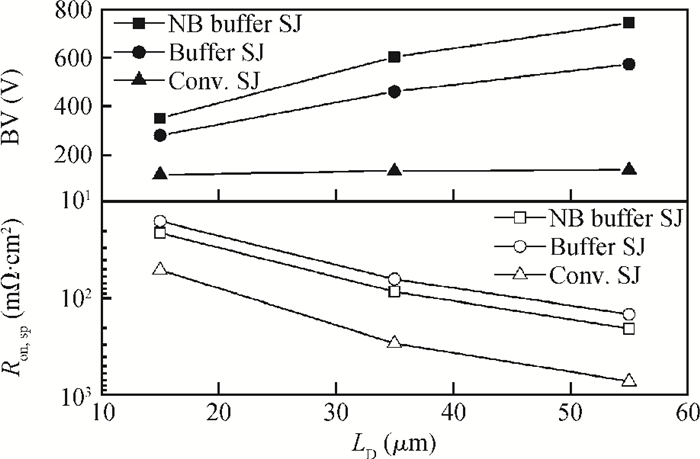

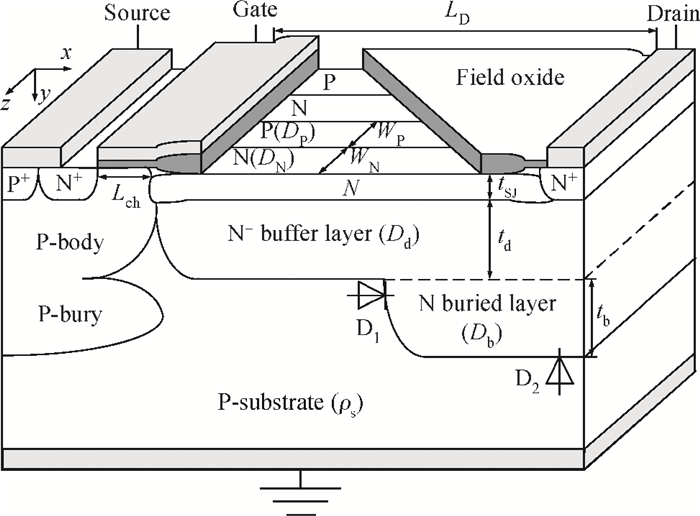

A novel buffer super-junction (SJ) lateral double-diffused MOSFET (LDMOS) with an N-type buried layer (NB) is proposed. An N- buffer layer is implemented under the SJ region and an N-type layer is buried in the P substrate. Firstly, the new electric field peak introduced by the p-n junction of the P substrate and the N-type buried layer modulates the surface electric field distribution. Secondly, the N- buffer layer suppresses the substrate assisted depletion effect. Both of them improve the breakdown voltage (BV). Finally, because of the shallow depth of the SJ region, the NB buffer SJ-LDMOS is compatible with Bi-CMOS technology. Simulation results indicate that the average value of the surface lateral electric field strength of the NB buffer SJ-LDMOS reaches 23 V/μm at 15 μm drift length which results in a BV of 350 V and a specific on-resistance of 21 mΩ · cm2. -

References

[1] Chen X B, Mawby P A, Salama T. Theory of a novel voltage-sustaining layer for power devices. J Microelectron, 1998, 29(12):1005 doi: 10.1016/S0026-2692(98)00065-2[2] Chen X B, Wang X, Sin J K O. A novel high-voltage sustaining structure with buried oppositely doped regions. IEEE Trans Electron Devices, 2000, 47(6):1280 doi: 10.1109/16.842974[3] Udrea F, Popescu A, Miline W I. A new class of lateral power devices for HVIC's based on the 3D RESURF concept. IEEE BTCM, 1998:187 http://ieeexplore.ieee.org/document/741921/?arnumber=741921[4] Udrea F, Popescu A, Miline W I. The 3D RESURF double-gate MOSFET:a revolutionary power device concept. Electron Lett, 1998, 34(8):808 doi: 10.1049/el:19980504[5] Wu W, Zhang B, Fang J, et al. High-voltage super-junction lateral double-diffused metal oxide semiconductor with a partial lightly doped pillar. Chin Phys B, 2013, 22(6):068501 doi: 10.1088/1674-1056/22/6/068501[6] Nassif-Khalil S G, Ander C, Salama T. Super-junction LDMOST on a silicon-on-sapphire substrate. IEEE Trans Electron Devices, 2003, 50(5):1385 doi: 10.1109/TED^2003.813460[7] Zhang B, Wang W, Chen W J, et al. High-voltage LDMOS with charge-balanced surface low on-resistance path layer. IEEE Electron Device Lett, 2009, 30(8):849 doi: 10.1109/LED^2009^2023541[8] Park I Y, Salama T. New superjunction LDMOST with n-buffer layer. IEEE Trans Electron Devices, 2006, 53(8):1909 doi: 10.1109/TED^2006.877007[9] Duan B X, Yang Y T, Zhang B. New superjunction LDMOS with N-type charges' compensation layer. IEEE Electron Device Lett, 2009, 30(3):305 doi: 10.1109/LED^2009^2012396[10] Onishi Y, Wang H, Xu E, et al. SJ-FINFET:a new low voltage lateral superjunction MOSFET. Proc IEEE ISPSD, 2008:111 http://ieeexplore.ieee.org/document/4538910/keywords[11] Rub M, Bar M, Deml G, et al. A 600 V 8.7Ω·mm2 lateral super-junction transistor Proc IEEE ISPSD, 2006:305[12] Chen W J, Zhang B, Li Z J. Optimization of super-junction SOI-LDMOS with a step doping surface-implanted layer. Semicond Sci Technol, 2007, 22(5):464 doi: 10.1088/0268-1242/22/5/002[13] Wang W L, Zhang B, Li Z J. Super junction LDMOS with enhanced dielectric layer electric field for high breakdown voltage. Journal of Semiconductors, 2011, 32(2):262 http://www.jos.ac.cn/bdtxbcn/ch/reader/view_abstract.aspx?file_no=10080905&flag=1[14] Udrea F. State-of-the-art technologies and devices for high-voltage integrated circuits. IET Circuits Devices Syst, 2007, 1(5):357 doi: 10.1049/iet-cds:20070025[15] TCAD Sentaurus Manuals 2010 Version D-2010. 03 -

Proportional views

DownLoad:

DownLoad: