| Citation: |

Xiao Ma, Zhankun Du, Chang Liu, Ke Liu, Yuepeng Yan, Tianchun Ye. A fractional-N frequency synthesizer for wireless sensor network nodes[J]. Journal of Semiconductors, 2014, 35(12): 125003. doi: 10.1088/1674-4926/35/12/125003

****

X Ma, Z K Du, C Liu, K Liu, Y P Yan, T C Ye. A fractional-N frequency synthesizer for wireless sensor network nodes[J]. J. Semicond., 2014, 35(12): 125003. doi: 10.1088/1674-4926/35/12/125003.

|

A fractional-N frequency synthesizer for wireless sensor network nodes

DOI: 10.1088/1674-4926/35/12/125003

More Information

-

Abstract

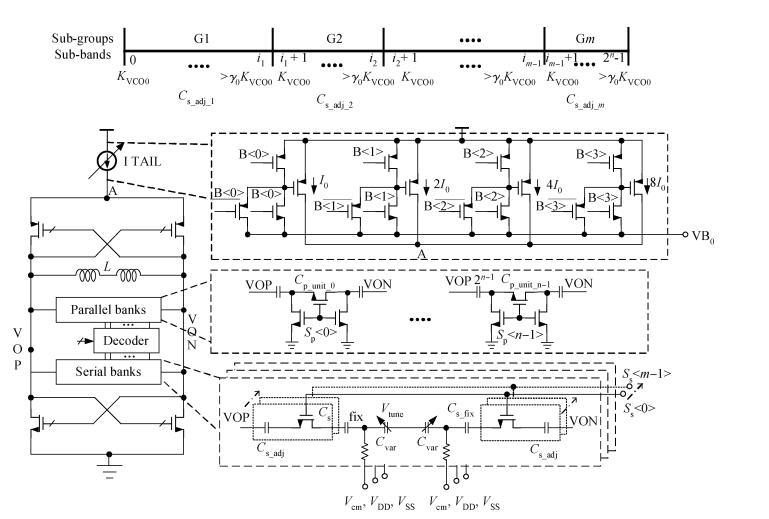

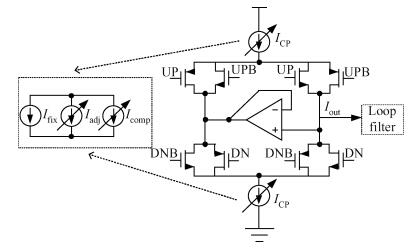

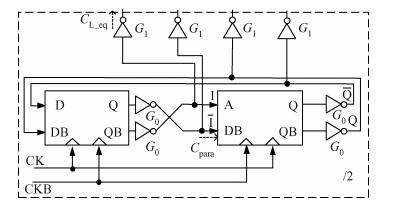

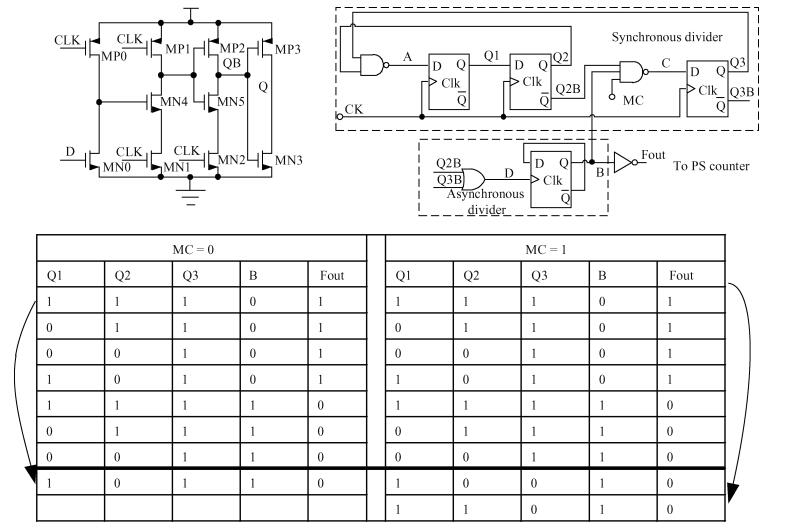

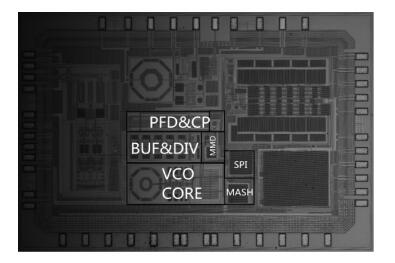

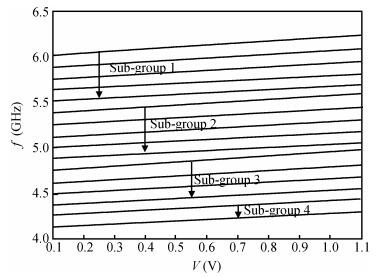

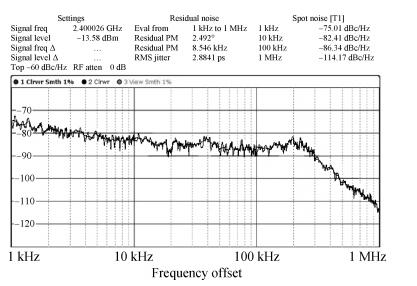

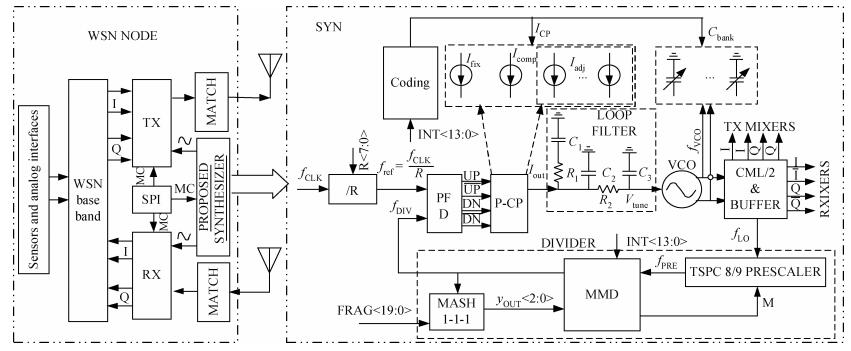

This paper presents a fractional-N frequency synthesizer for wireless sensor network (WSN) nodes. The proposed frequency synthesizer adopts a phase locked loop (PLL) based structure, which employs an LC voltage-controlled oscillator (VCO) with small VCO gain (KVCO) and frequency step (fstep) variations, a charge pump (CP) with current changing in proportion with the division ratio and a 20-bit Δ Σ modulator, etc. To realize constant KVCO and fstep, a novel capacitor sub-bands grouping method is proposed. The VCO sub-groups' sizes are arranged according to the maximal allowed KVCO variation of the system. Besides, a current mode logic divide-by-2 circuit with inside-loop buffers ensures the synthesizer generates I/Q quadrature signals robustly. This synthesizer is implemented in a 0.13 μm CMOS process. Measurement results show that the frequency synthesizer has a frequency span from 2.07 to 3.11 GHz and the typical phase noise is -86.34 dBc/Hz at 100 kHz offset and -114.17 dBc/Hz at 1 MHz offset with a loop bandwidth of about 200 kHz, which meet the WSN nodes' requirements.-

Keywords:

- WSN,

- frequency synthesizer,

- KVCO variation,

- divide-by-2

-

References

[1] Drago S, Leenaerts D M W, Nauta B, et al. A 200μA duty-cycled PLL for wireless sensor nodes in 65 nm CMOS. IEEE J Solid-State Circuits, 2010, 45(7):1305 doi: 10.1109/JSSC.2010.2049458[2] Wu T, Hanumolu P K, Mayaram K, et al. Method for a constant loop bandwidth in LC-VCO PLL frequency synthesizers. IEEE J Solid-State Circuits, 2009, 44(2):427 doi: 10.1109/JSSC.2008.2010792[3] Shin J, Shin H. A 1.9-3.8 GHz Δ Σ fractional-N PLL frequency synthesizer with fast auto-calibration of loop bandwidth and VCO frequency. IEEE J Solid-State Circuits, 2012, 47(3):665 doi: 10.1109/JSSC.2011.2179733[4] Rao A, Mansour M, Singh G, et al. A 4-6.4 GHz LC PLL with adaptive bandwidth control for a forwarded clock link. IEEE J Solid-State Circuits, 2008, 43(9):2099 doi: 10.1109/JSSC.2008.2001870[5] Craninckx J, Steyaert M S J. A fully integrated CMOS DCS-1800 frequency synthesizer. IEEE J Solid-State Circuits, 1998, 33(12):2054 doi: 10.1109/4.735547[6] Moon Y J, Roh Y S, Jeong C Y, et al. A 4.39-5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO-gain variati on. IEEE Microw Wireless Compon Lett, 2009, 19(8):524 doi: 10.1109/LMWC.2009.2024846[7] Collins D, Keady A, Szczepkowski G, et al. A 90 nm, low power VCO with reduced KVCO and sub-band spacing variation. New Circuits and Systems Conference (NEWCAS), 2011:141[8] Chen P W, Lin T Y, Ke L W, et al. A 0.13μm CMOS quad-band GSM/GPRS/EDGE RF transceiver using a low-noise fractional-N frequency synthesizer and direct-conversion architecture. IEEE J Solid-State Circuits, 2009, 44(5):1454 doi: 10.1109/JSSC.2009.2015797[9] Hauspie D, Park E C, Craninckx J. Wideband VCO with simultaneous switching of frequency band, active core, and varactor size. IEEE J Solid-State Circuits, 2007, 42(7):1472 doi: 10.1109/JSSC.2007.899105[10] Banerjee D. PLL performance, simulation, and design. 4th ed. Dog Ear Publishing, LCC, 2006[11] Hegazi E, Abidi A A. Varactor characteristics, oscillator tuning curves, and AM-FM conversion. IEEE J Solid-State Circuits, 2003, 38(6):1033 doi: 10.1109/JSSC.2003.811968[12] Ding Y, Kenneth K O. A 21-GHz 8-modulus prescaler and a 20-GHz phase-locked loop fabricated in 130-nm CMOS. IEEE J Solid-State Circuits, 2007, 42(6):1240 doi: 10.1109/JSSC.2007.897140[13] Yang C Y, Dehng G K, Hsu J M, et al. New dynamic flip-flops for high-speed dual-modulus prescaler. IEEE J Solid-State Circuits, 1998, 33(10):1568 doi: 10.1109/4.720406[14] Lam C, Razavi B. A 2.6-GHz/5.2-GHz frequency synthesizer in 0.4-μm CMOS technology. IEEE J Solid-State Circuits, 2000, 35(5):117[15] De Muer B, Steyaert M S J. A CMOS monolithic Δ Σ-controlled fractional-N frequency synthesizer for DCS-1800. IEEE J Solid-State Circuits, 2002, 37(7):835 doi: 10.1109/JSSC.2002.1015680[16] Swaminathan A, Wang K J, Galton I. A wide-bandwidth 2.4 GHz ISM band fractional-N PLL with adaptive phase noise cancellation. IEEE J Solid-State Circuits, 2007, 42(12):2639 doi: 10.1109/JSSC.2007.908763[17] Low Wenfeng, Feng Peng, Wang Haiyong, et al. Low power fast settling multi-standard current reusing CMOS fractional-N frequency synthesizer. Journal of Semiconductors, 2012, 33(4):045004 doi: 10.1088/1674-4926/33/4/045004[18] Ti C L, Liu Y H, Lin T H. A 2.4-GHz fractional-N PLL with a PFD/CP linearization and an improved CP circuit. IEEE International Symposium on Circuits and systems, 2008:1728 -

Proportional views

DownLoad:

DownLoad: