| Citation: |

Siyang Han, Baoyong Chi, Xinwang Zhang, Zhihua Wang. A power scalable PLL frequency synthesizer for high-speed Δ-Σ ADC[J]. Journal of Semiconductors, 2014, 35(8): 085002. doi: 10.1088/1674-4926/35/8/085002

****

S Y Han, B Y Chi, X W Zhang, Z H Wang. A power scalable PLL frequency synthesizer for high-speed Δ-Σ ADC[J]. J. Semicond., 2014, 35(8): 085002. doi: 10.1088/1674-4926/35/8/085002.

|

A power scalable PLL frequency synthesizer for high-speed Δ-Σ ADC

DOI: 10.1088/1674-4926/35/8/085002

More Information

-

Abstract

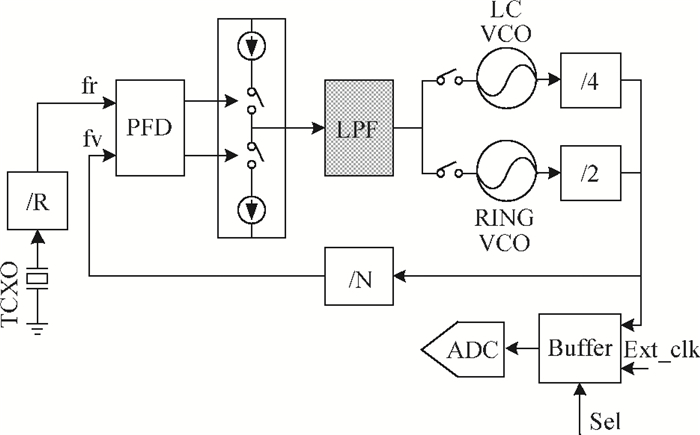

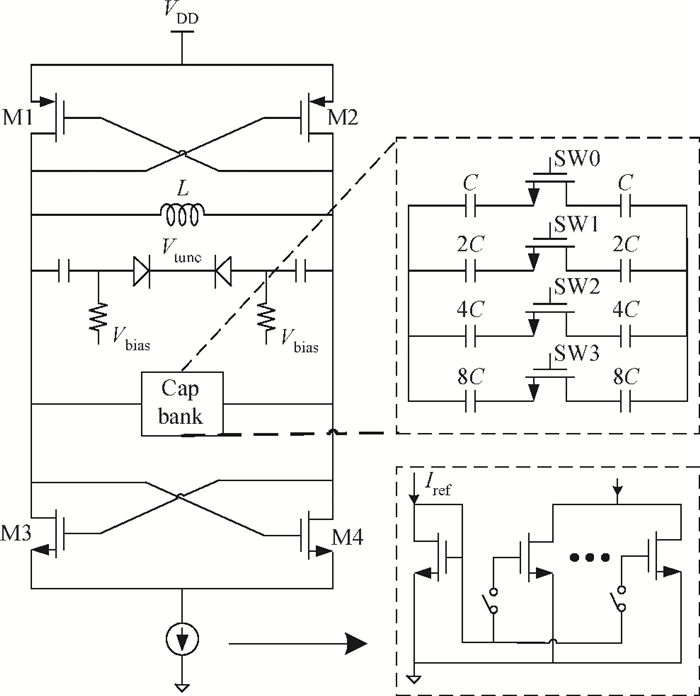

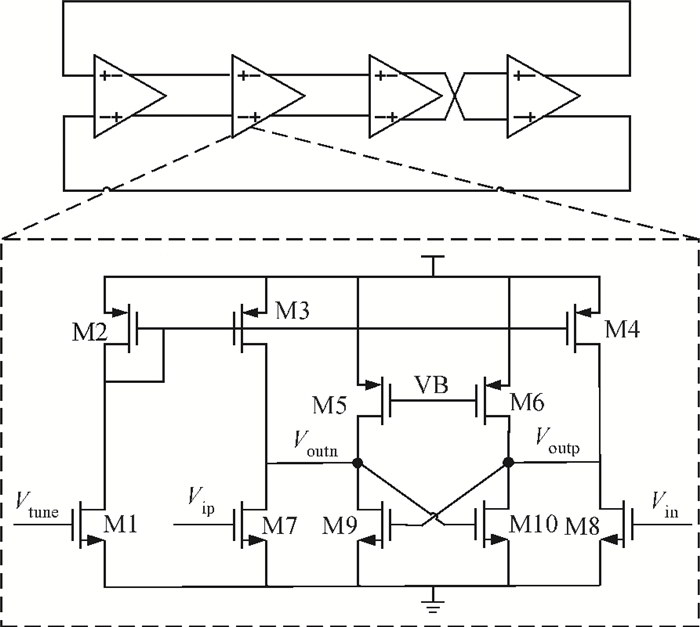

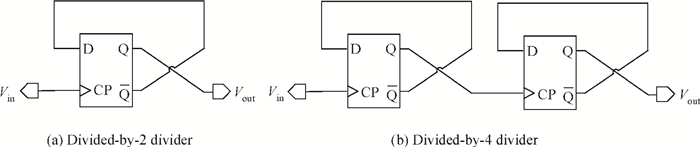

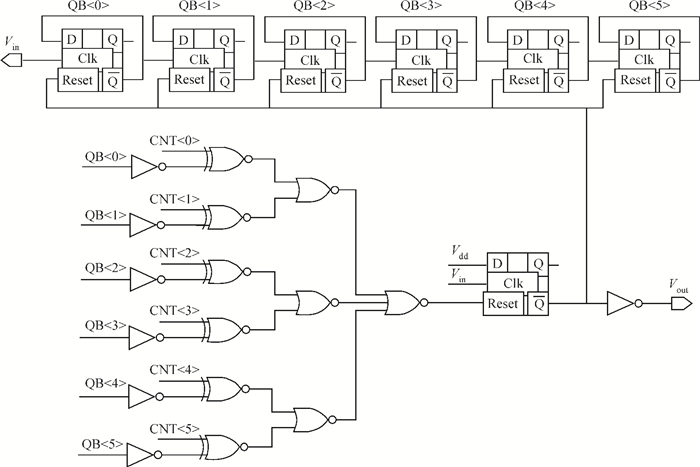

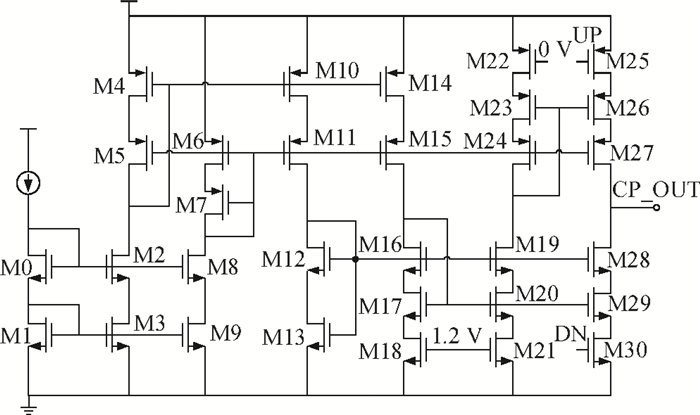

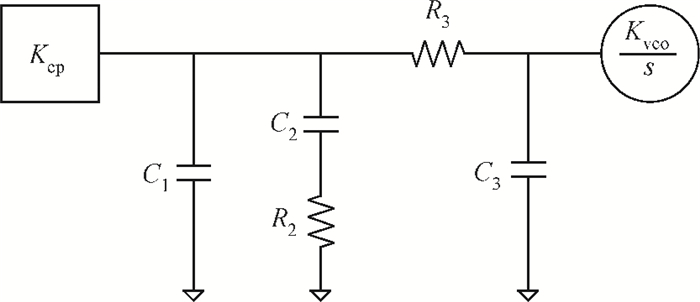

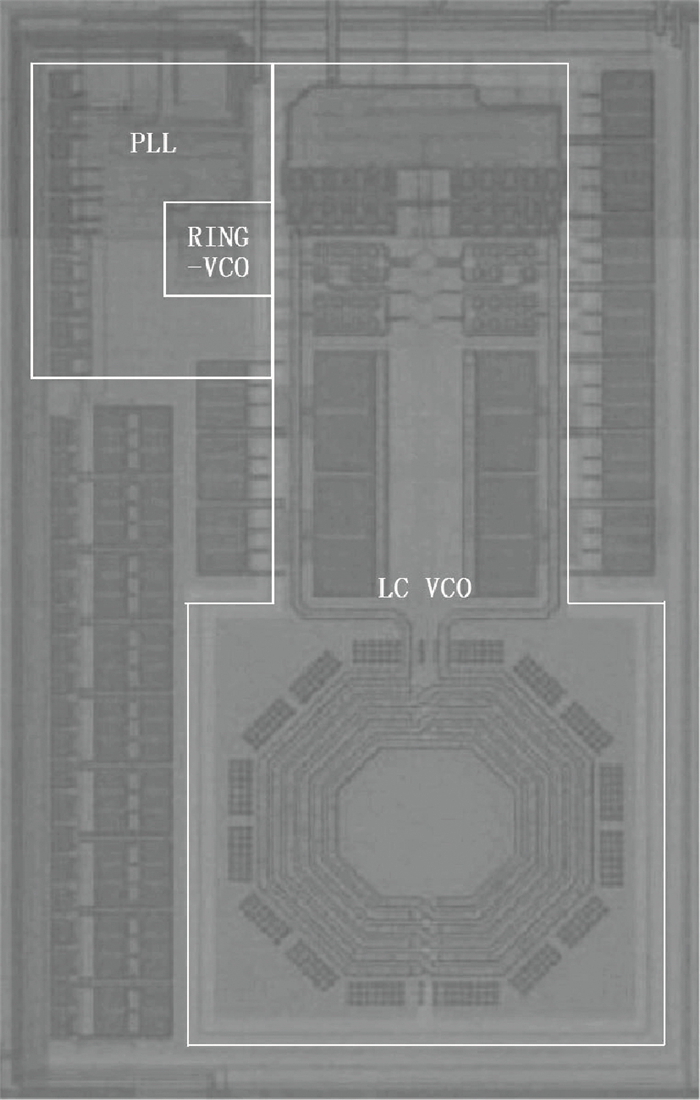

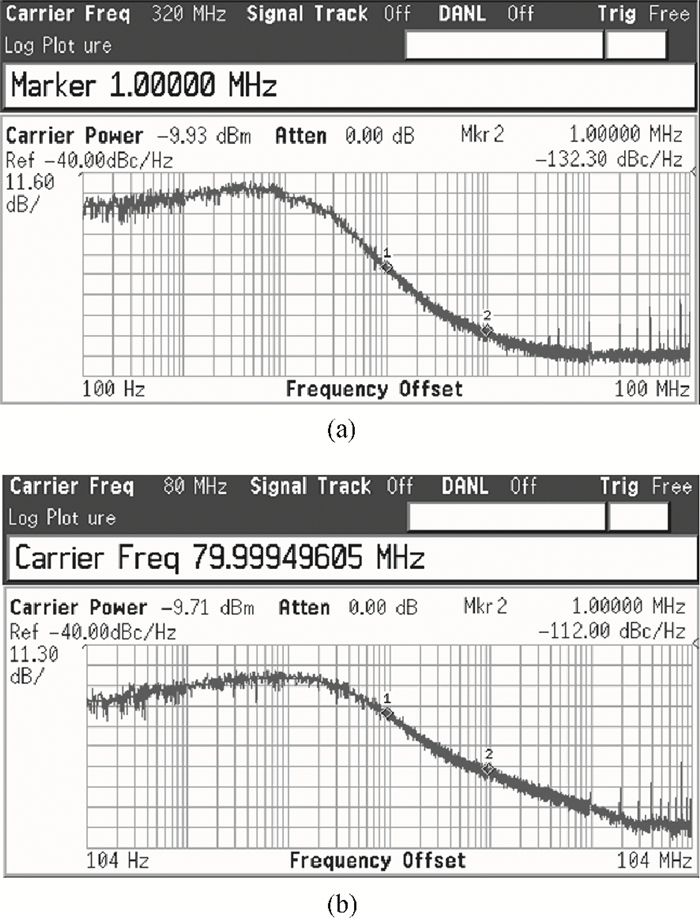

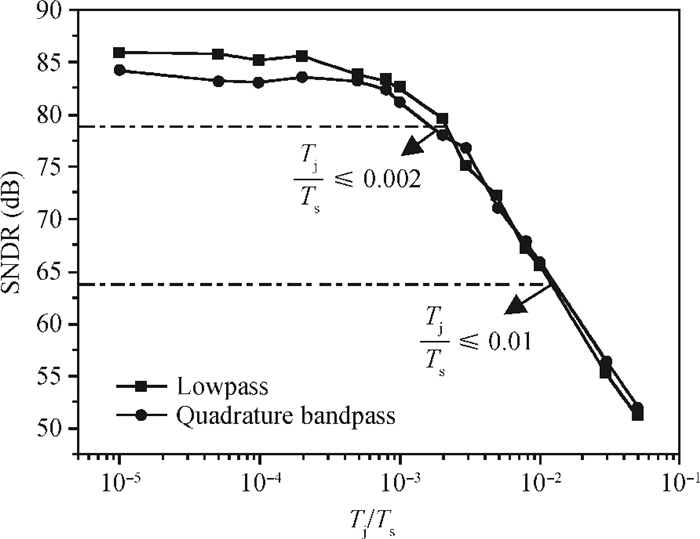

A 35-130 MHz/300-360 MHz phase-locked loop frequency synthesizer for Δ-Σ analog-to-digital converter (ADC) in 65 nm CMOS is presented. The frequency synthesizer can work in low phase-noise mode (300-360 MHz) or in low-power mode (35-130 MHz) to satisfy the ADC's requirements. To switch between these two modes, a high frequency GHz LC VCO followed by a divided-by-four frequency divider and a low frequency ring VCO followed by a divided-by-two frequency divider are integrated on-chip. The measured results show that the frequency synthesizer achieves a phase-noise of -132 dBc/Hz at 1 MHz offset and an integrated RMS jitter of 1.12 ps with 1.74 mW power consumption from a 1.2 V power supply in low phase-noise mode. In low-power mode, the frequency synthesizer achieves a phase-noise of -112 dBc/Hz at 1 MHz offset and an integrated RMS jitter of 7.23 ps with 0.92 mW power consumption from a 1.2 V power supply. -

References

[1] Walden R H. Analog-to-digital converter survey and analysis. IEEE J Sel Areas Commun, 1999, 17(4):539 doi: 10.1109/49.761034[2] Gao X, Klumperink E A M, Bohsali M, et al. A 2.2 GHz 7.6 mW sub-sampling PLL with -126 dBc/Hz in-band phase noise and 0.15 psrms jitter in 0.18μm CMOS. IEEE ISSCC Dig Tech Papers, 2009:392 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=4977473[3] Liang C F, Hsiao K J. An injection-locked ring PLL with self-a ligned injection window. IEEE ISSCC Dig Tech Papers, 2011:90 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5746232[4] Akihide S, Yamaji T, Itakura T. A 570 fsrms integrated-jitter ring-VCO-based 1.21 GHz PLL with hybrid loop. IEEE ISSCC Dig Tech Papers, 2011:98 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=5746236[5] Yan Y, Yan T, Mo T, et al. A 62MHz-316MHz phase-locked loop based on ring oscillator for ADC clock generator in 0.18μm CMOS. IEEE Third International Conference ICMTMA, 2011, 1:6 http://ieeexplore.ieee.org/document/5720687/[6] Liu J, Jeon S, Jang T K, et al. A 0.8 V, sub-mW, varactor-tuning ring-oscillator-based clock generator in 32nm CMOS. IEEE Asian Solid State Circuits Conference (A-SSCC), 2011:337 http://ieeexplore.ieee.org/document/6123582/[7] Lee H J, Kern A M, Hyvonen S. A scalable sub-1.2 mW 300 MHz-to-1.5GHz host-clock PLL for system-on-chip in 32 nm CMOS. IEEE International Solid-State Circuits Conference ISSCC, 2011:96 http://www.mendeley.com/research/scalable-sub12mw-300mhzto15ghz-hostclock-pll-systemonchip-32nm-cmos/[8] Kral A, Behbahani F, Abidi A A. RF-CMOS oscillators with switched tuning. Proc IEEE Custom Integr Circuits Conf, 1998:555 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=695039[9] Kobayashi Y, Amakawa S, Ishihara N, et al. A low-phase-noise injection-locked differential ring-VCO with half-integral subharmonic locking in 0.18μm CMOS. Proceedings of ESSCIRC, 2009:440 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5325965[10] Lee J, Wang H. Study of subharmonically injection-locked PLLs. IEEE J Solid-State Circuits, 2009, 44(5):1539 doi: 10.1109/JSSC.2009.2016701[11] Hajimiri A, Lee T H. Design issues in CMOS differential LC oscillators. IEEE J Solid-State Circuits, 1999, 34(5):717 doi: 10.1109/4.760384[12] Lesson D B. A simple model of feedback oscillator noise spectrum. Proc IEEE, 1966, 54(2):329 doi: 10.1109/PROC.1966.4682[13] Gao X, Klumperink E A M, Bohsali M, et al. A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by N. IEEE J Solid-State Circuits, 2009, 44(12):3253 doi: 10.1109/JSSC.2009.2032723 -

Proportional views

DownLoad:

DownLoad: