| Citation: |

Chen Liu, Yuming Zhang, Yimen Zhang, Hongliang Lü, Bin Lu. Temperature dependent interfacial and electrical characteristics during atomic layer deposition and annealing of HfO2 films in p-GaAs metal-oxide-semiconductor capacitors[J]. Journal of Semiconductors, 2015, 36(12): 124003. doi: 10.1088/1674-4926/36/12/124003

****

C Liu, Y M Zhang, Y M Zhang, H Lü, B Lu. Temperature dependent interfacial and electrical characteristics during atomic layer deposition and annealing of HfO2 films in p-GaAs metal-oxide-semiconductor capacitors[J]. J. Semicond., 2015, 36(12): 124003. doi: 10.1088/1674-4926/36/12/124003.

|

Temperature dependent interfacial and electrical characteristics during atomic layer deposition and annealing of HfO2 films in p-GaAs metal-oxide-semiconductor capacitors

DOI: 10.1088/1674-4926/36/12/124003

More Information

-

Abstract

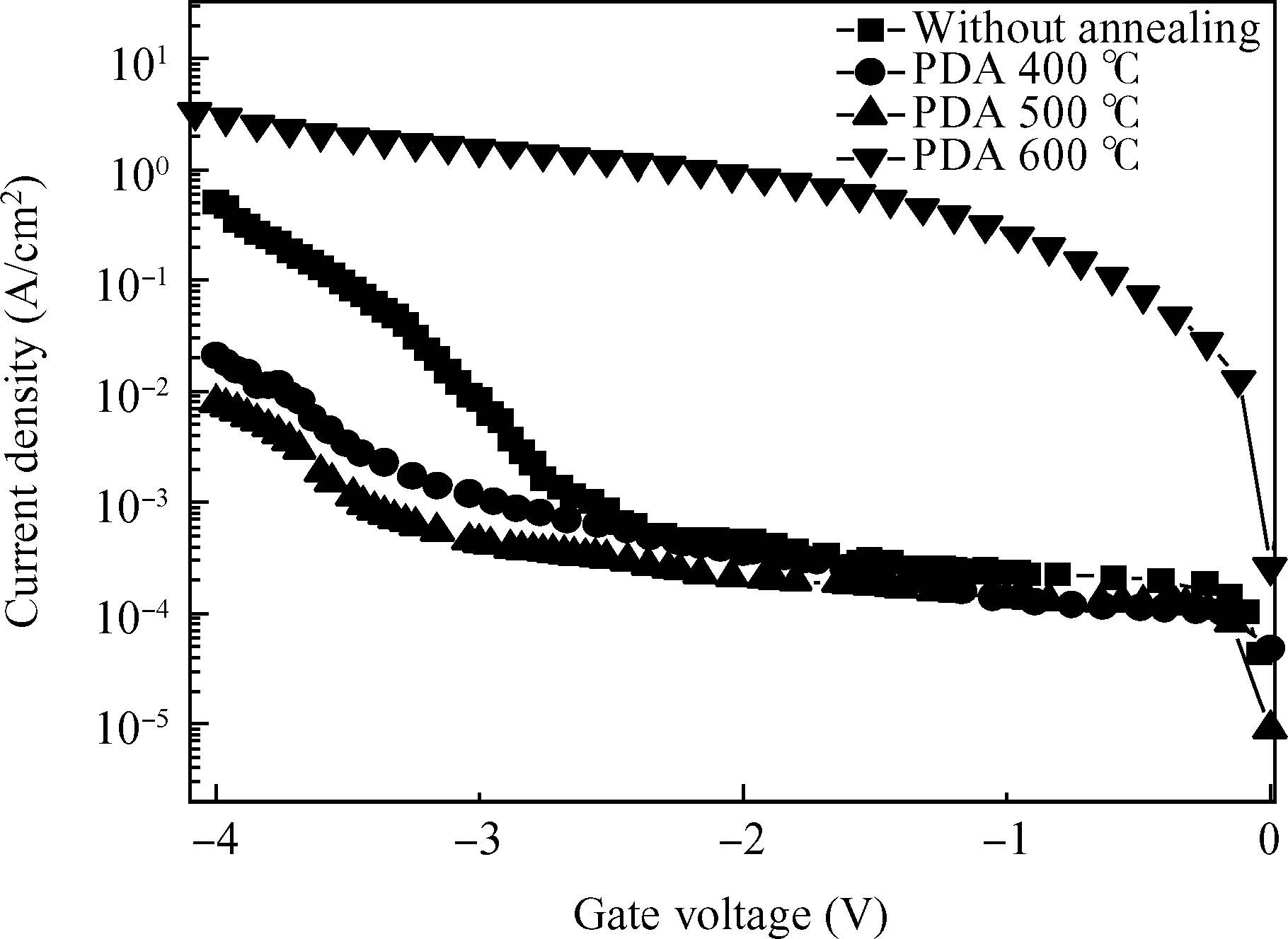

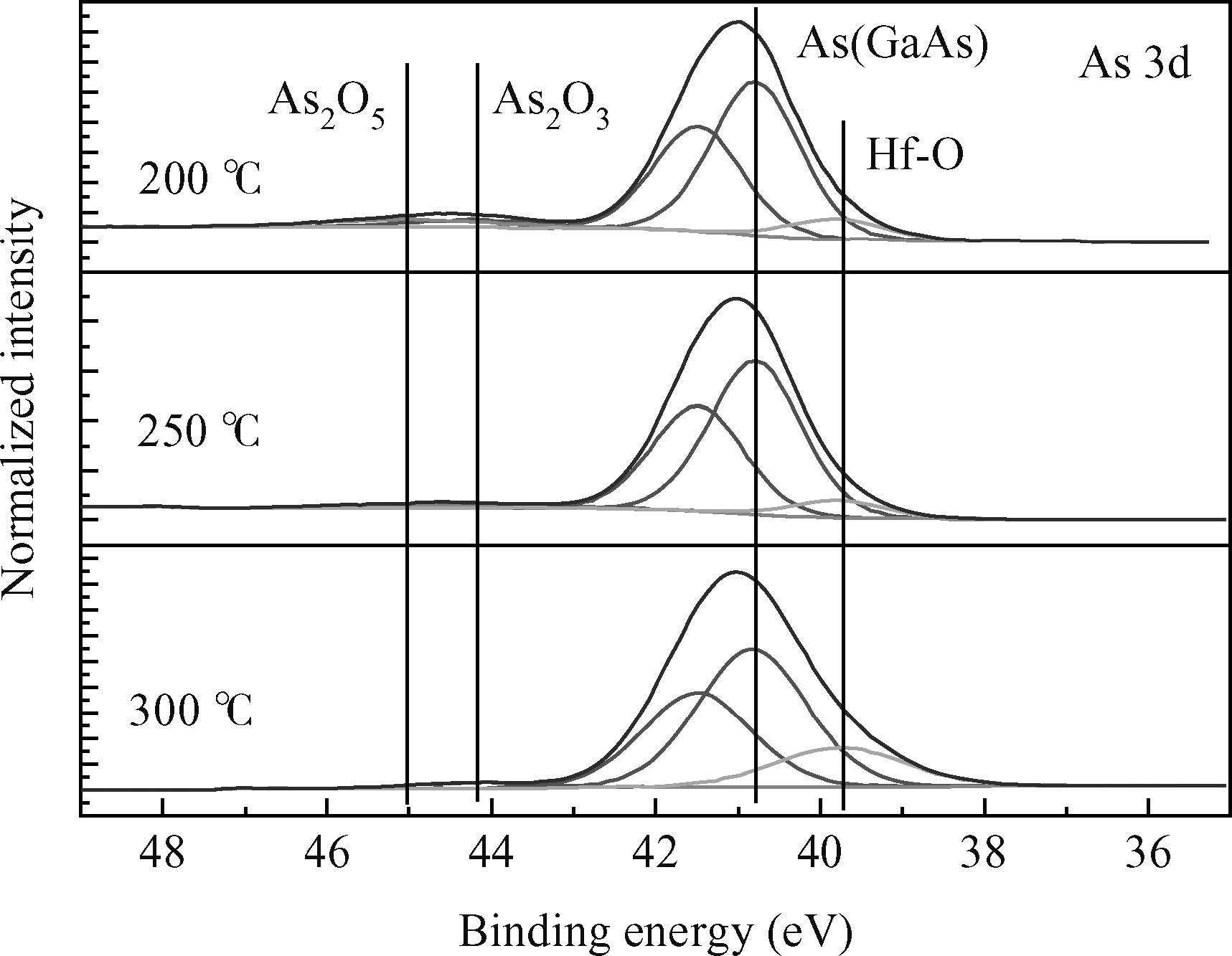

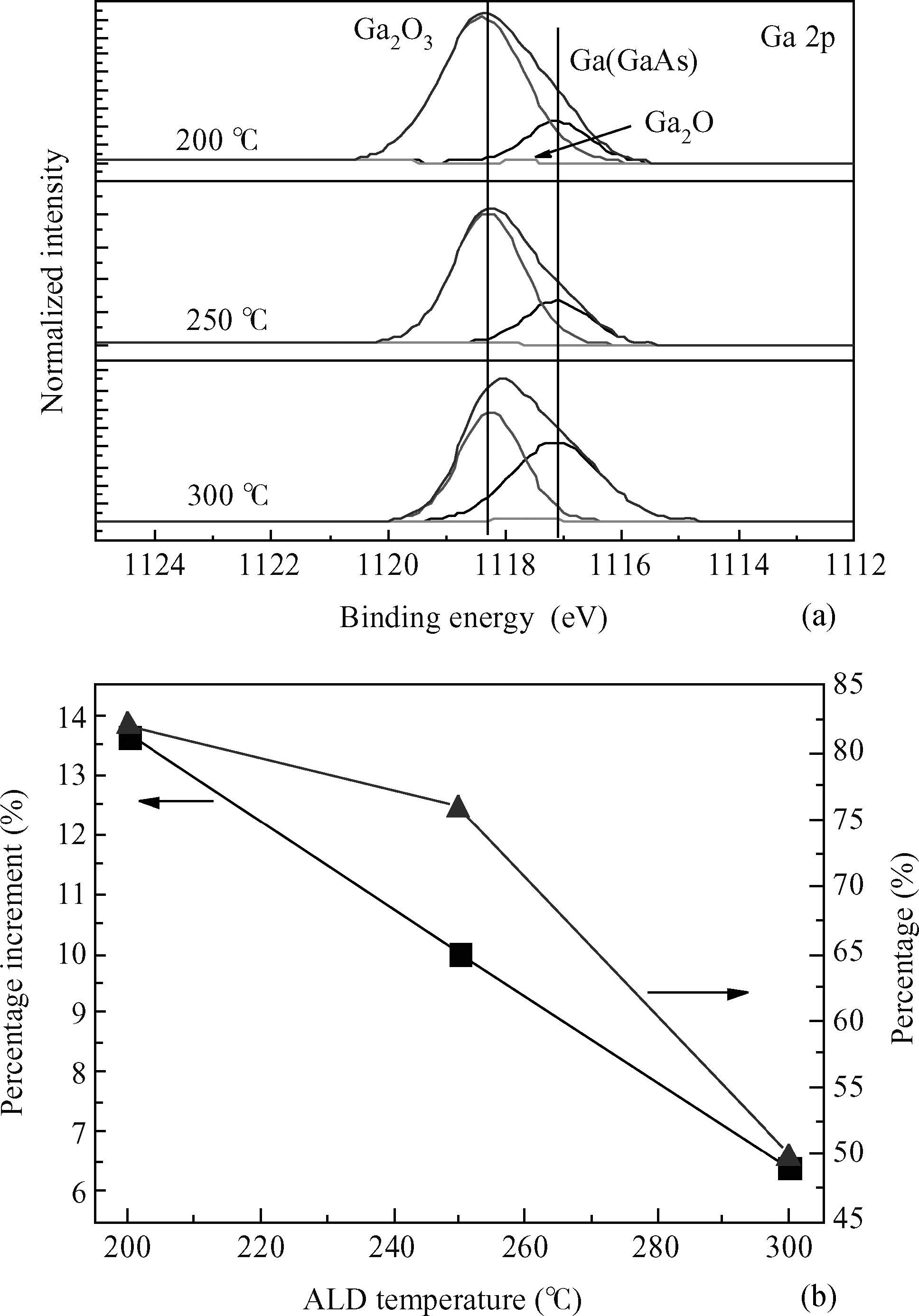

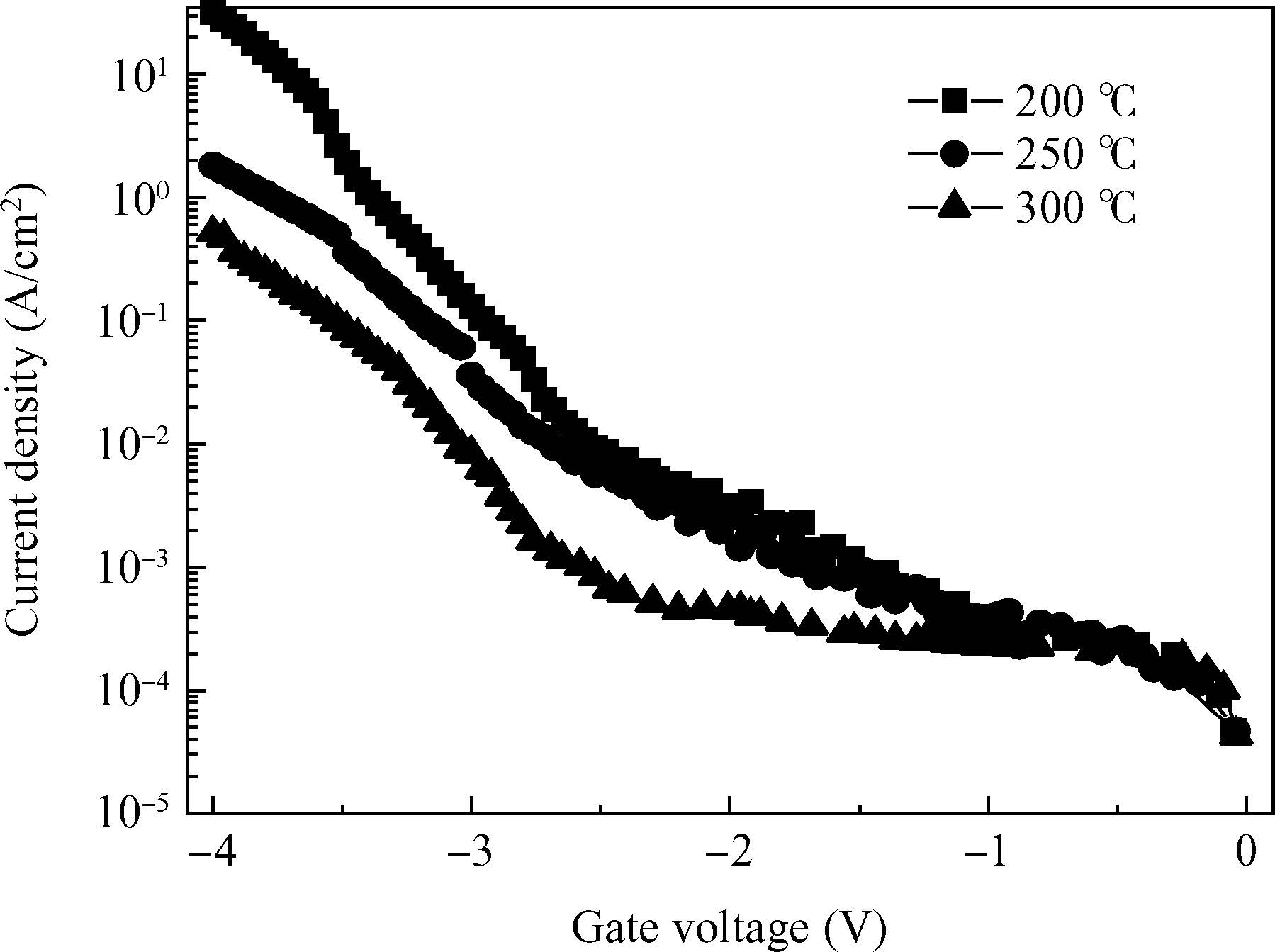

We have investigated the temperature dependent interfacial and electrical characteristics of p-GaAs metal-oxide-semiconductor capacitors during atomic layer deposition(ALD) and annealing of HfO2 using the tetrakis(ethylmethyl) amino hafnium precursor. The leakage current decreases with the increase of the ALD temperature and the lowest current is obtained at 300℃ as a result of the Frenkel-Poole conduction induced leakage current being greatly weakened by the reduction of interfacial oxides at the higher temperature. Post deposition annealing(PDA) at 500℃ after ALD at 300℃ leads to the lowest leakage current compared with other annealing temperatures. A pronounced reduction in As oxides during PDA at 500℃ has been observed using X-ray photoelectron spectroscopy at the interface resulting in a proportional increase in Ga2O3. The increment of Ga2O3 after PDA depends on the amount of residual As oxides after ALD. Thus, the ALD temperature plays an important role in determining the high-k/GaAs interface condition. Meanwhile, an optimum PDA temperature is essential for obtaining good dielectric properties. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] -

Proportional views

DownLoad:

DownLoad: