| Citation: |

Hui Hong, Shiliang Li, Tao Zhou. Design of a low power 10 bit 300 ksps multi-channel SAR ADC for wireless sensor network applications[J]. Journal of Semiconductors, 2015, 36(4): 045009. doi: 10.1088/1674-4926/36/4/045009

****

H Hong, S L Li, T Zhou. Design of a low power 10 bit 300 ksps multi-channel SAR ADC for wireless sensor network applications[J]. J. Semicond., 2015, 36(4): 045009. doi: 10.1088/1674-4926/36/4/045009.

|

Design of a low power 10 bit 300 ksps multi-channel SAR ADC for wireless sensor network applications

DOI: 10.1088/1674-4926/36/4/045009

More Information

-

Abstract

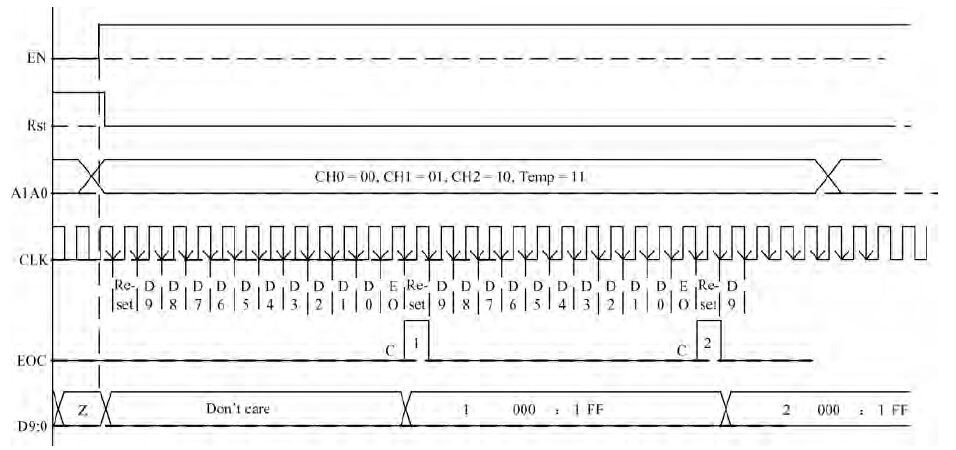

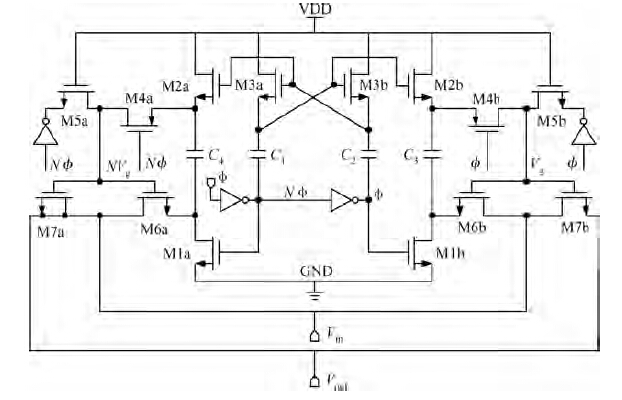

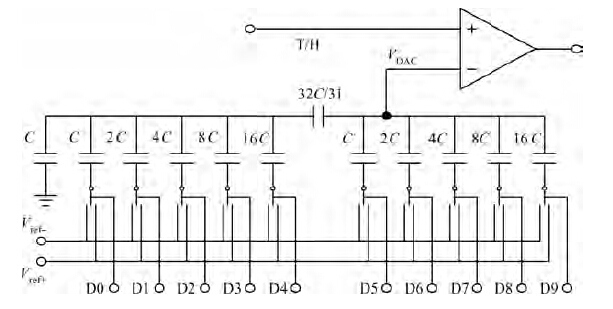

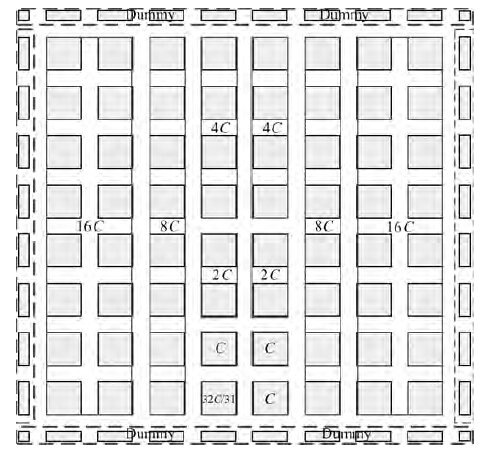

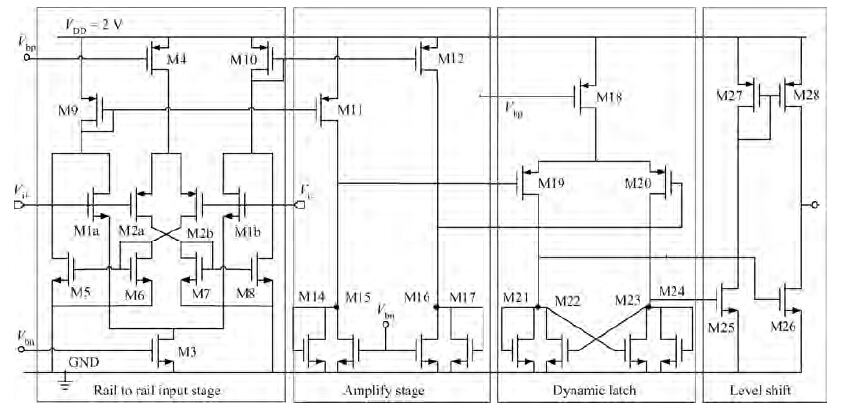

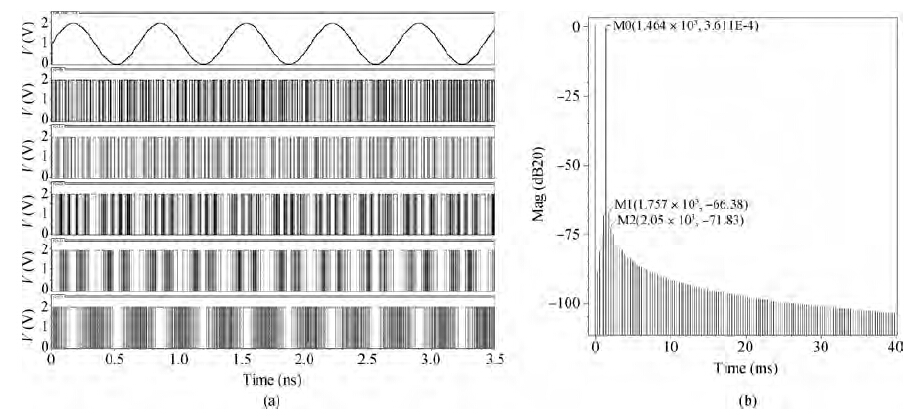

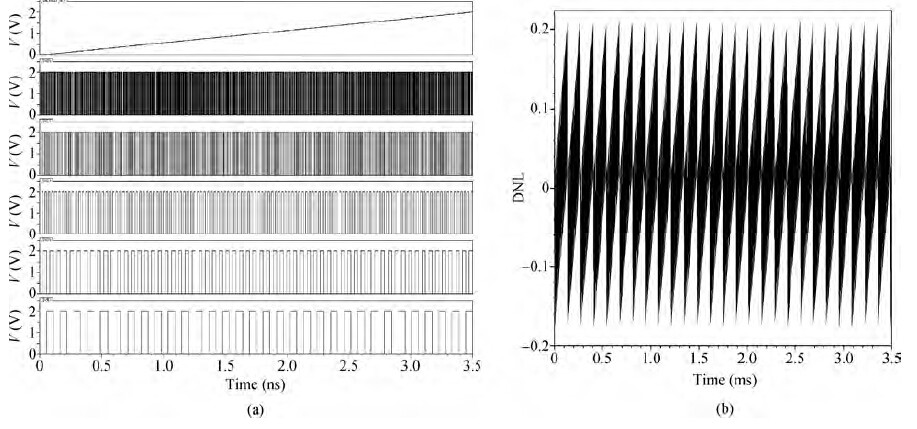

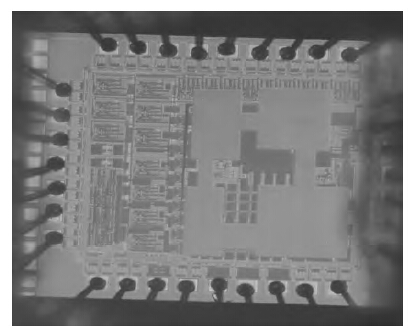

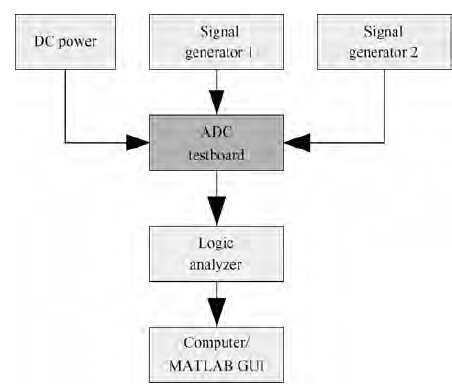

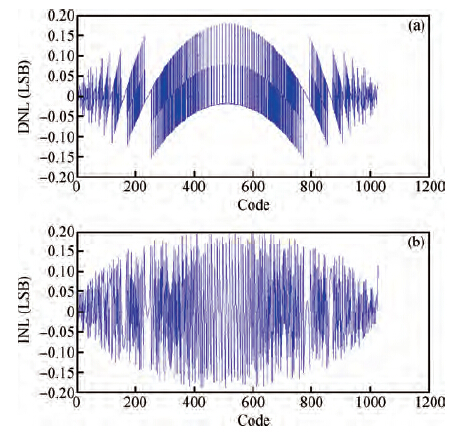

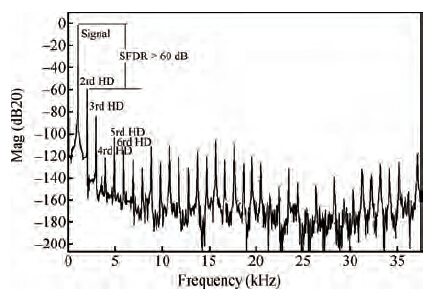

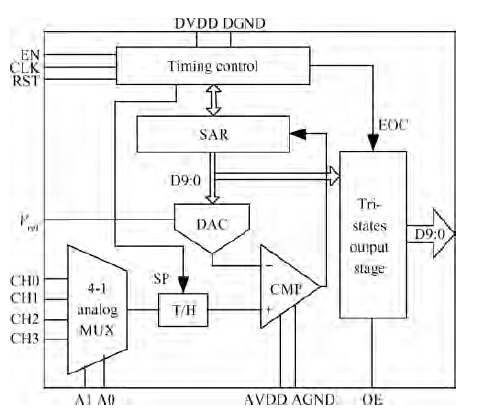

This paper presents a low power 10 bit 300 ksps successive approximation register analog-to-digital converter (SAR ADC) which is applied in wireless sensor network (WSN) applications. A single ended energy-saving split capacitor DAC array and a latch comparator with a rail to rail input stage are utilized to implement the ADC, which can reduce power dissipation while expanding the full scale input range and improve the signal-to-noise ratio (SNR). For power optimization the supply voltage of the SAR ADC is designed to be as low as 2 V. Four analog input channels are designed which make the ADC more suitable for WSN applications. The prototype circuit is fabricated using 3.3 V, 0.35 μm 2P4M CMOS technology and occupies an active chip area of 1.23 mm2. The test results show that the power dissipation is only 200 μW at a 2 V power supply and a sampling rate of 166 kSps. The calculated SNR is 58.25 dB, the ENOB is 9.38 bit and the FOM is 4.95 pJ/conversion-step.-

Keywords:

- low power,

- multi-channels,

- SAR ADC,

- WSN,

- split capacitor array

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] -

Proportional views

DownLoad:

DownLoad: