| Citation: |

Jiangzheng Cai, Suming Zhang, Jia Yuan, Xinchao Shang, Liming Chen, Yong Hei. A 320 mV, 6 kb subthreshold 10T SRAM employing voltage lowering techniques[J]. Journal of Semiconductors, 2015, 36(6): 065007. doi: 10.1088/1674-4926/36/6/065007

****

J Z Cai, S M Zhang, J Yuan, X C Shang, L M Chen, Y Hei. A 320 mV, 6 kb subthreshold 10T SRAM employing voltage lowering techniques[J]. J. Semicond., 2015, 36(6): 065007. doi: 10.1088/1674-4926/36/6/065007.

|

A 320 mV, 6 kb subthreshold 10T SRAM employing voltage lowering techniques

DOI: 10.1088/1674-4926/36/6/065007

More Information

-

Abstract

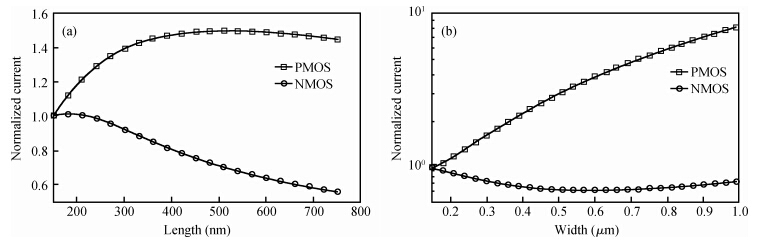

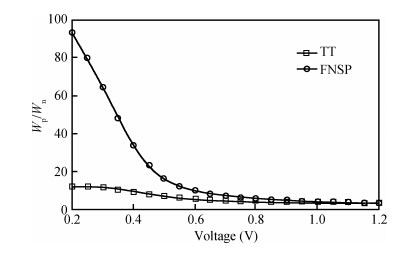

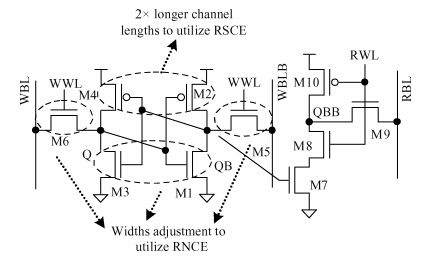

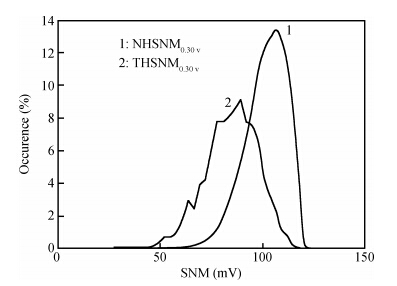

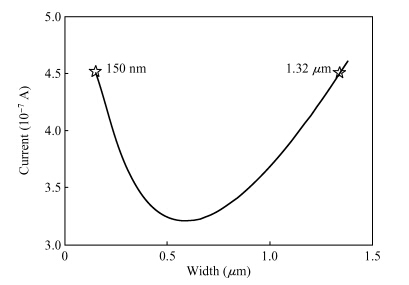

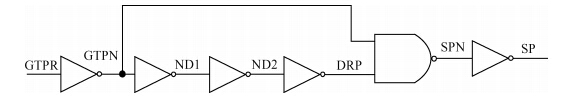

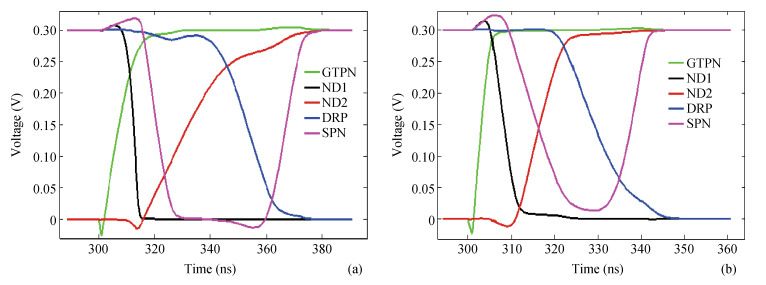

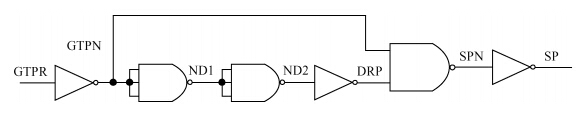

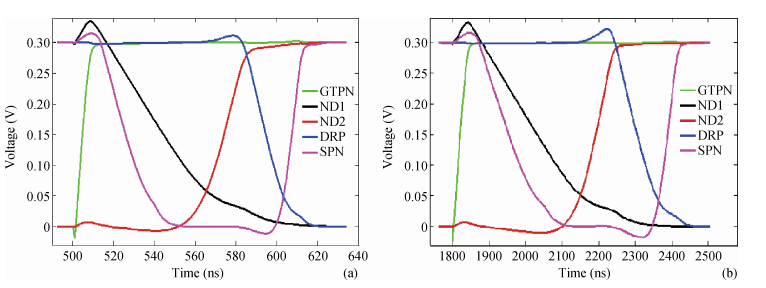

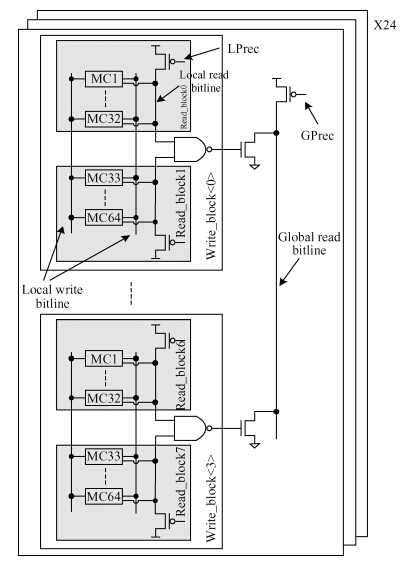

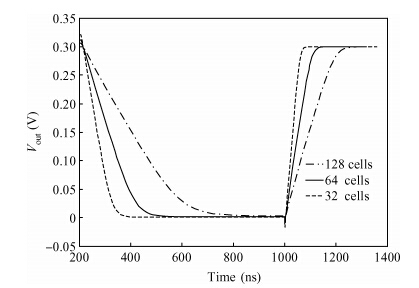

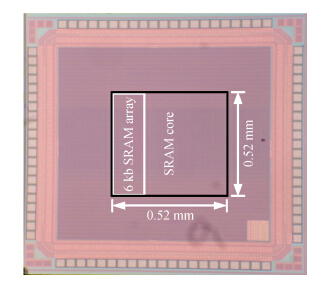

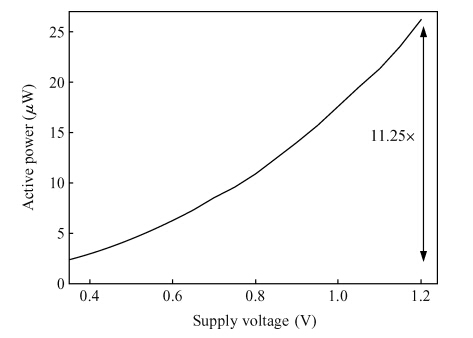

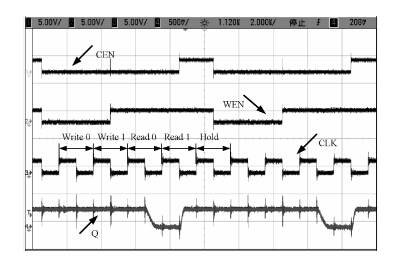

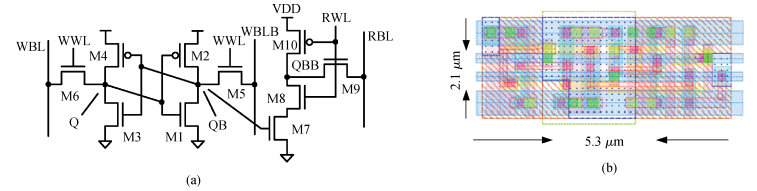

This paper presents a 6 kb SRAM that uses a novel 10T cell to achieve a minimum operating voltage of 320 mV in a 130 nm CMOS process. A number of low power circuit techniques are included to enable the proposed SRAM to operate in the subthreshold region. The reverse short channel effect and the reverse narrow channel effect are utilized to improve the performance of the SRAM. A novel subthreshold pulse generation circuit produces an ideal pulse to make read operation stable. A floating write bit-line effectively reduces the standby leakage consumption. Finally, a short read bit-line makes the read operation fast and energy-saving. Measurements indicate that these techniques are effective, the SRAM can operate at 800 kHz and consume 1.94 μW at its lowest voltage (320 mV). -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] -

Proportional views

DownLoad:

DownLoad: