| Citation: |

Min Chen, Yuntao Liu, Zhichao Li, Jingbo Xiao, Jie Chen. A low jitter supply regulated charge pump PLL with self-calibration[J]. Journal of Semiconductors, 2016, 37(1): 015006. doi: 10.1088/1674-4926/37/1/015006

****

M Chen, Y T Liu, Z C Li, J B Xiao, J Chen. A low jitter supply regulated charge pump PLL with self-calibration[J]. J. Semicond., 2016, 37(1): 015006. doi: 10.1088/1674-4926/37/1/015006.

|

A low jitter supply regulated charge pump PLL with self-calibration

DOI: 10.1088/1674-4926/37/1/015006

More Information

-

Abstract

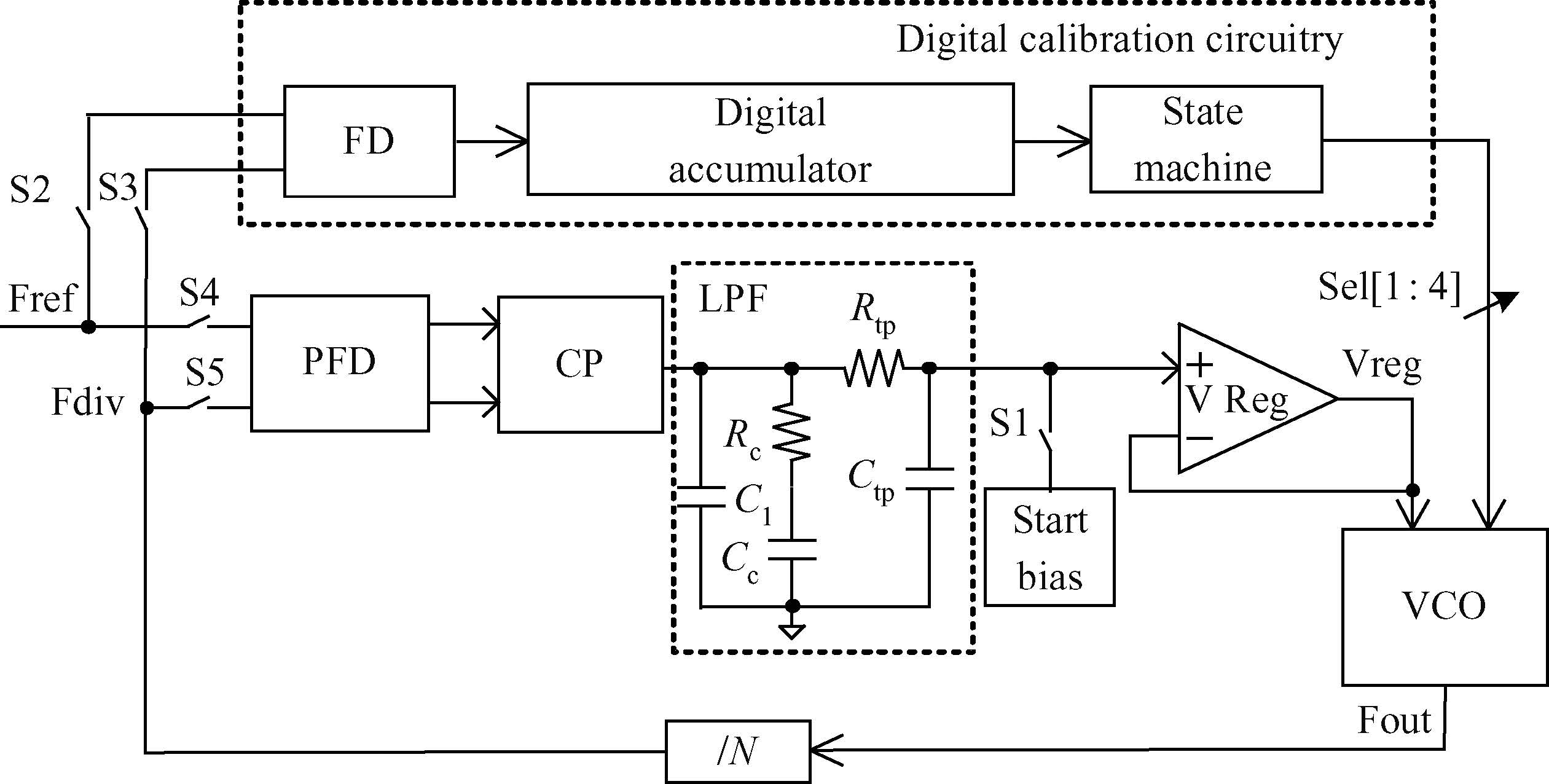

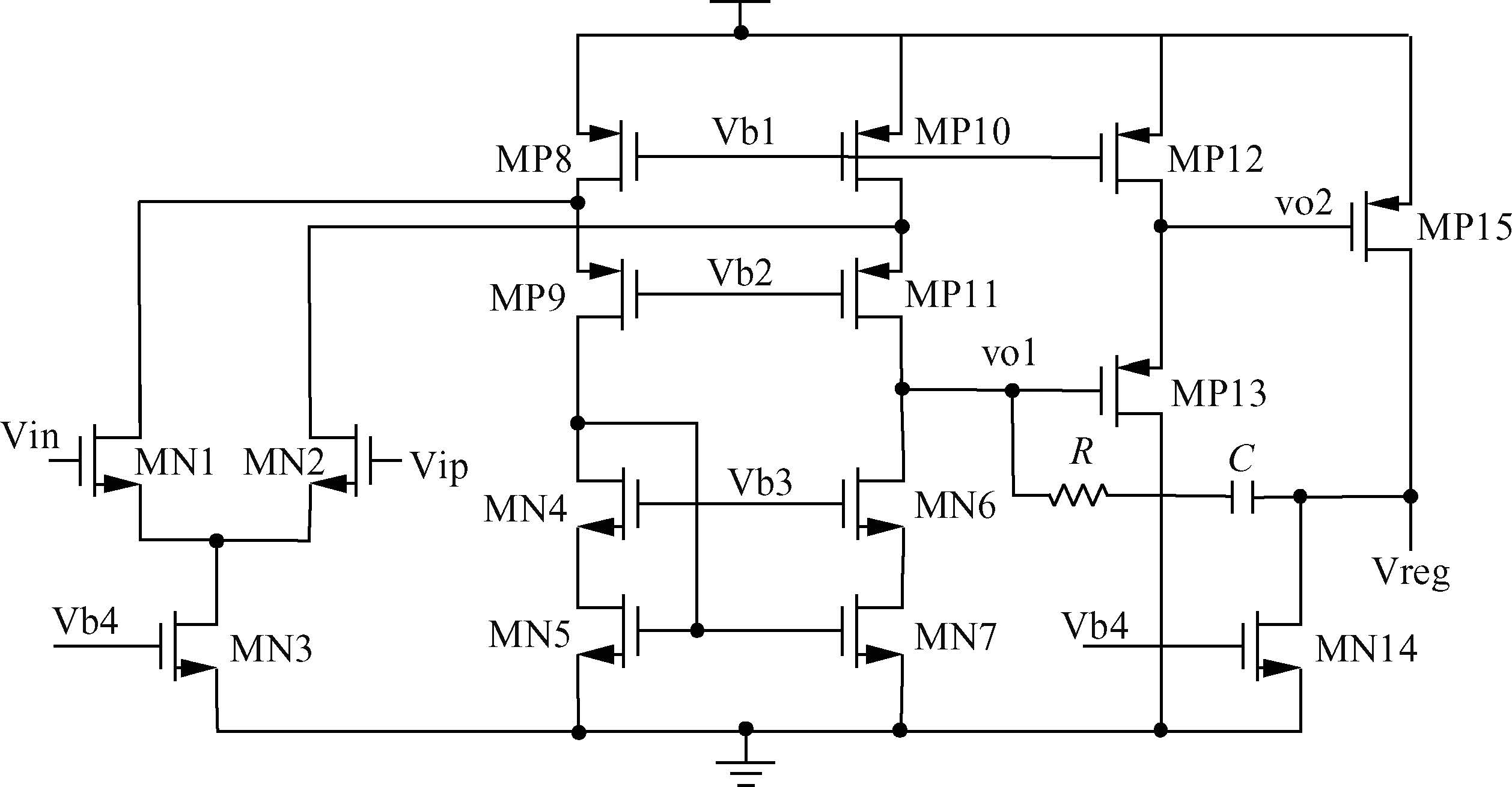

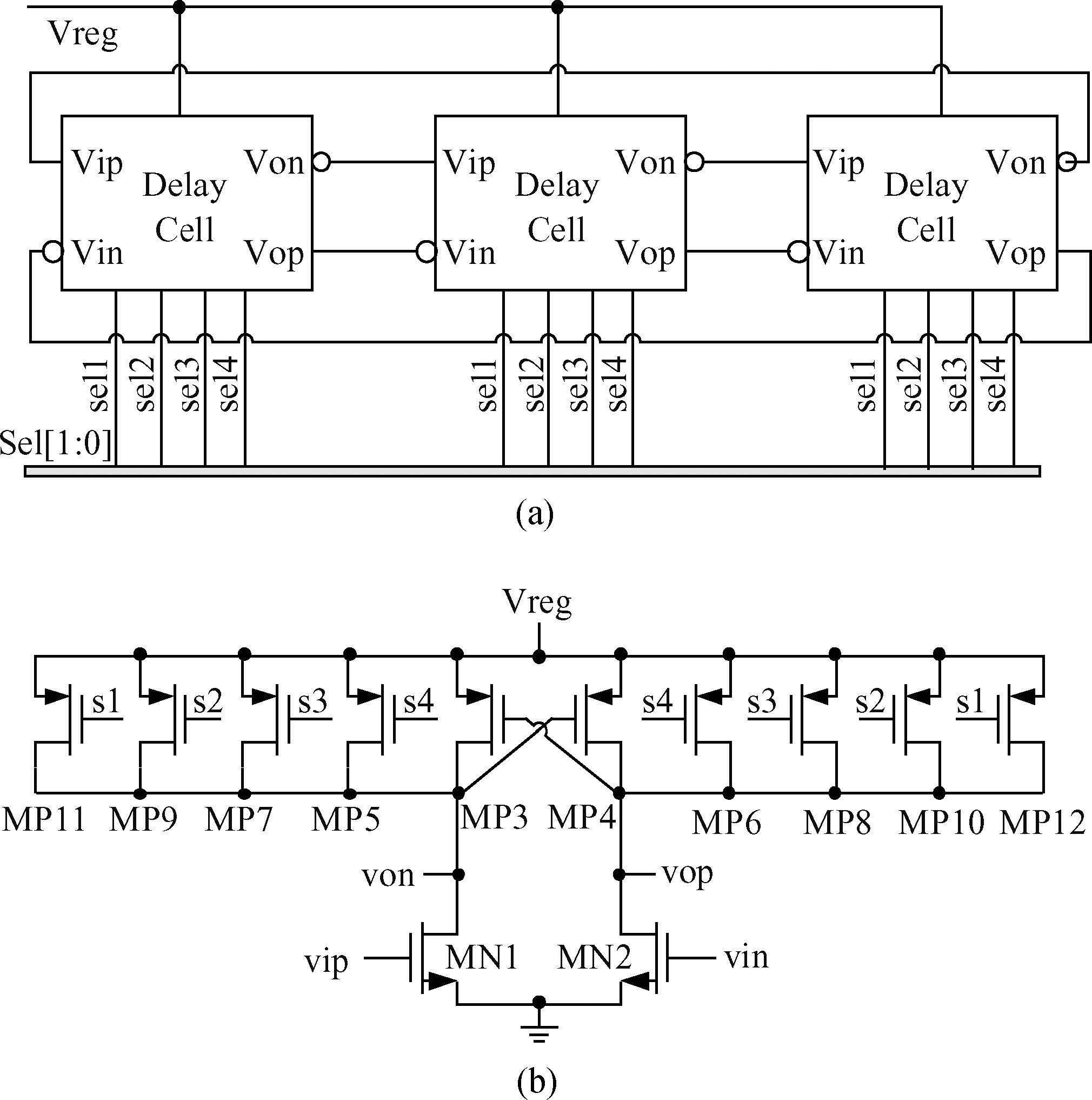

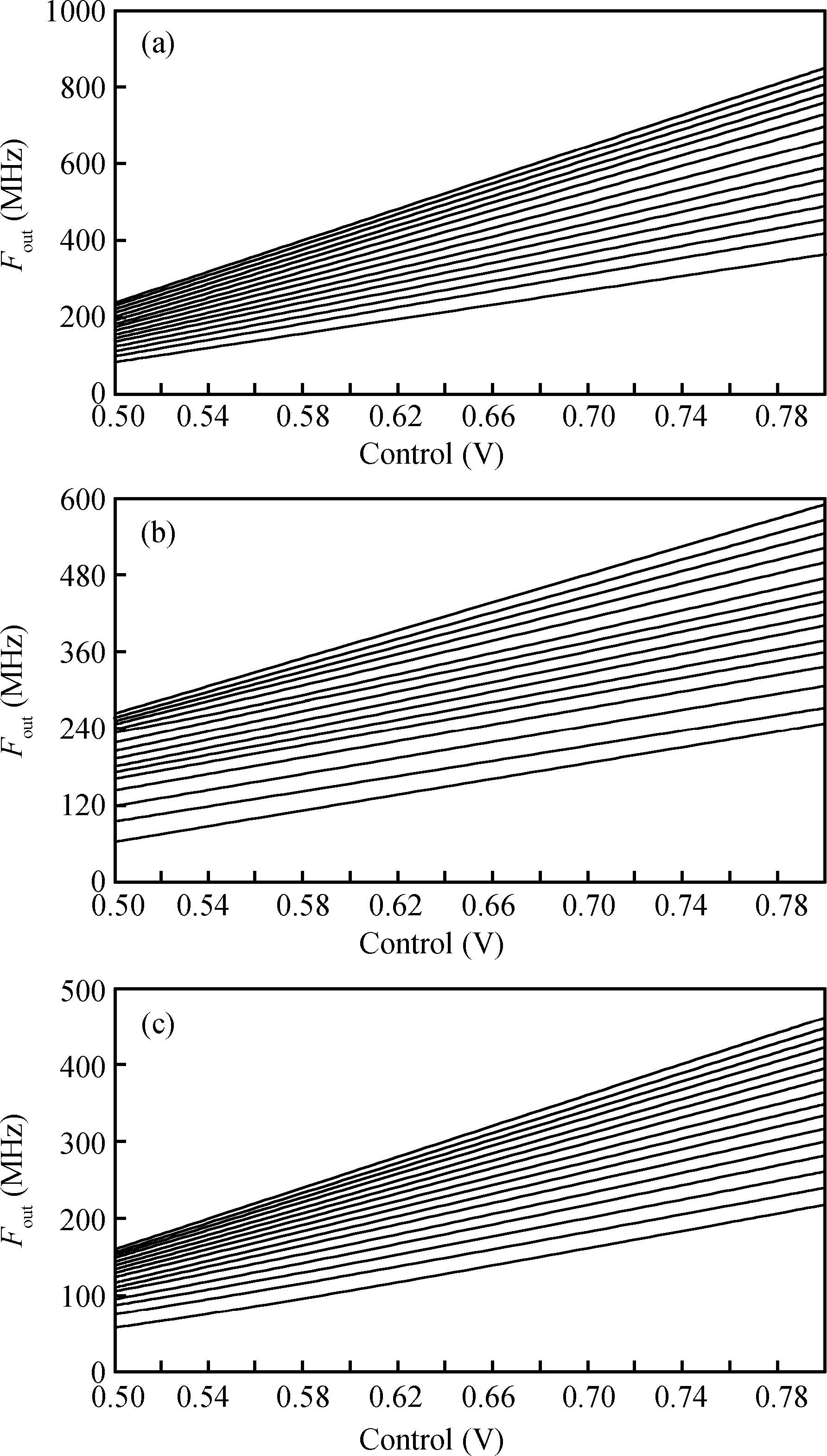

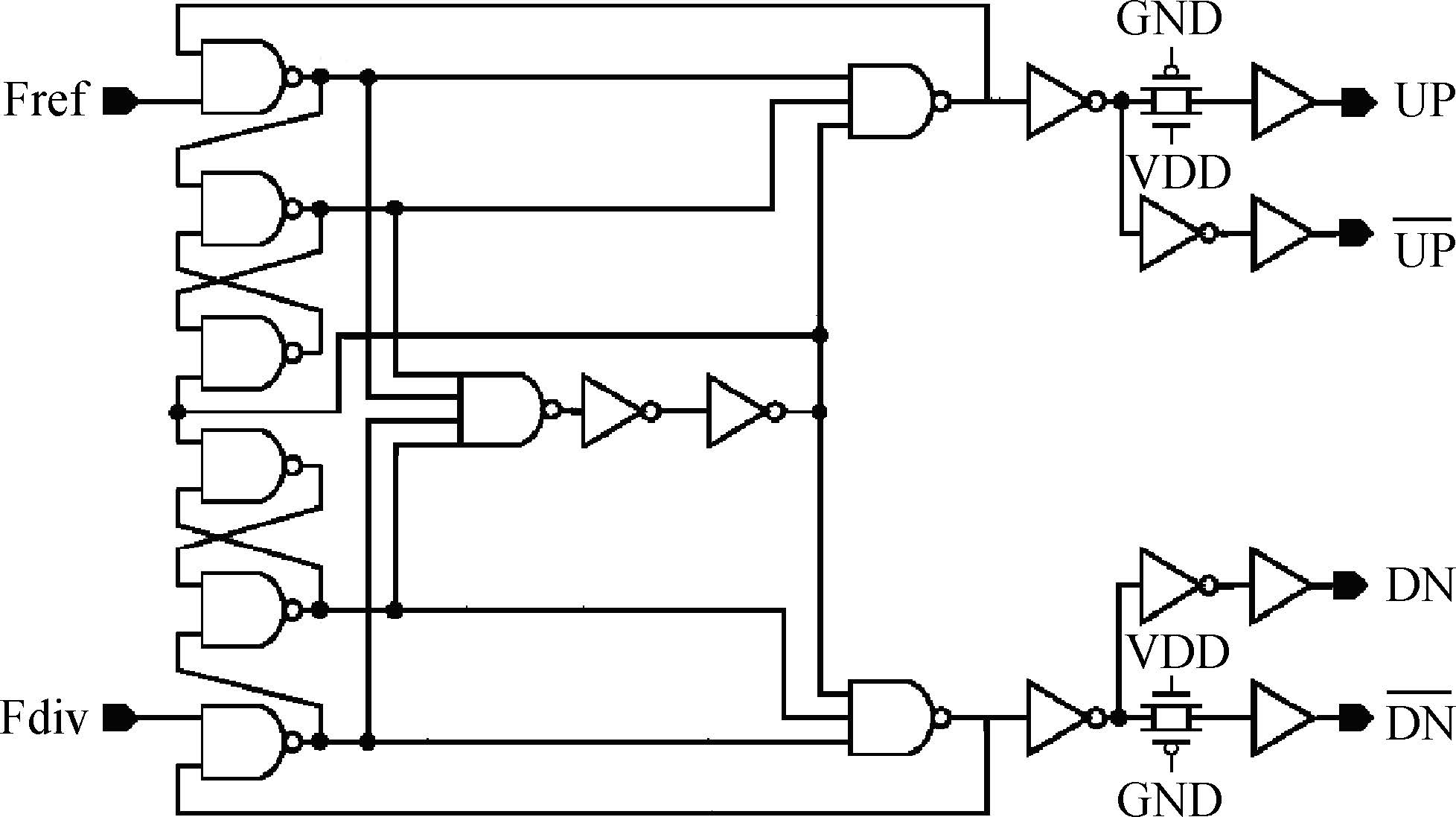

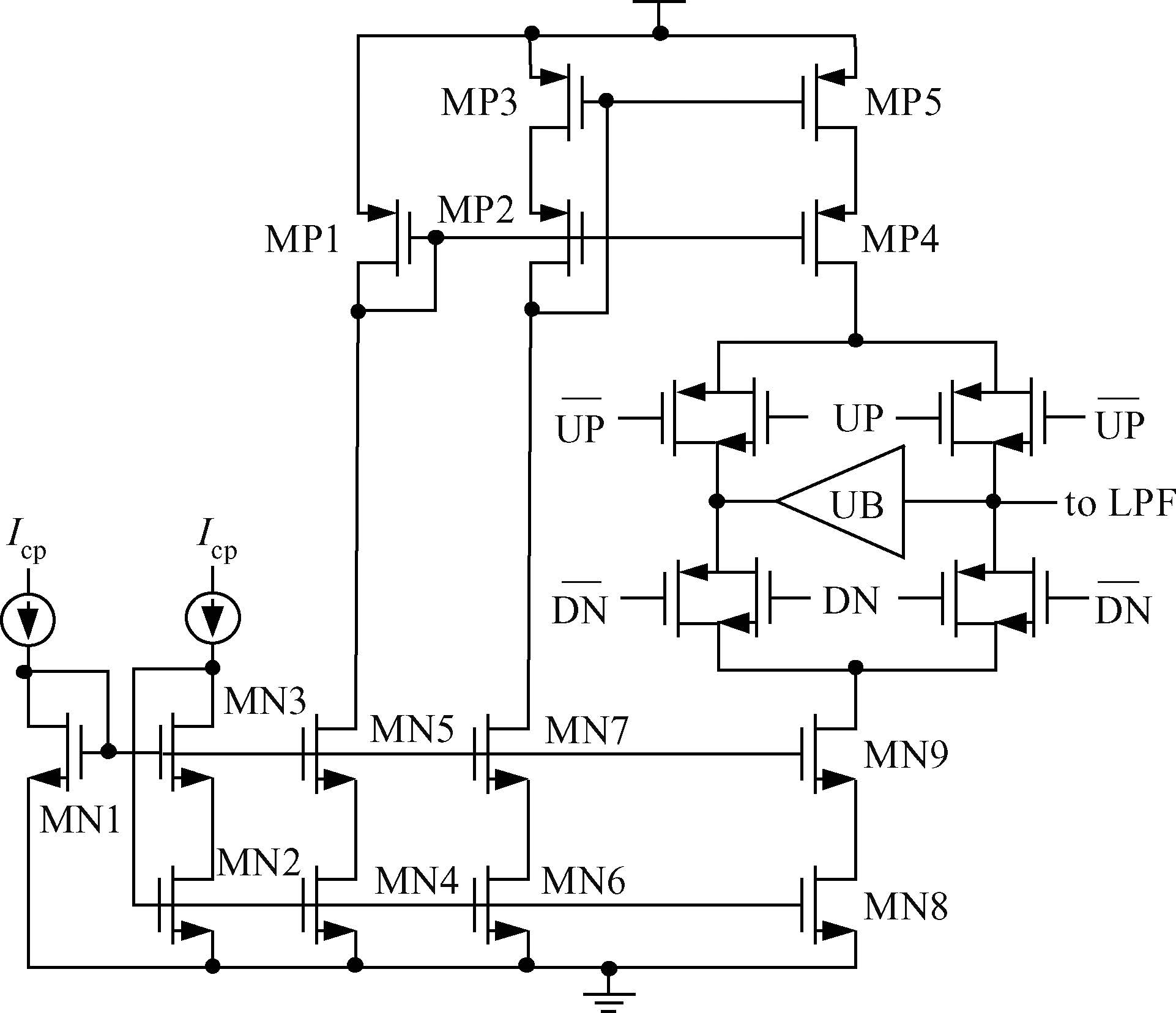

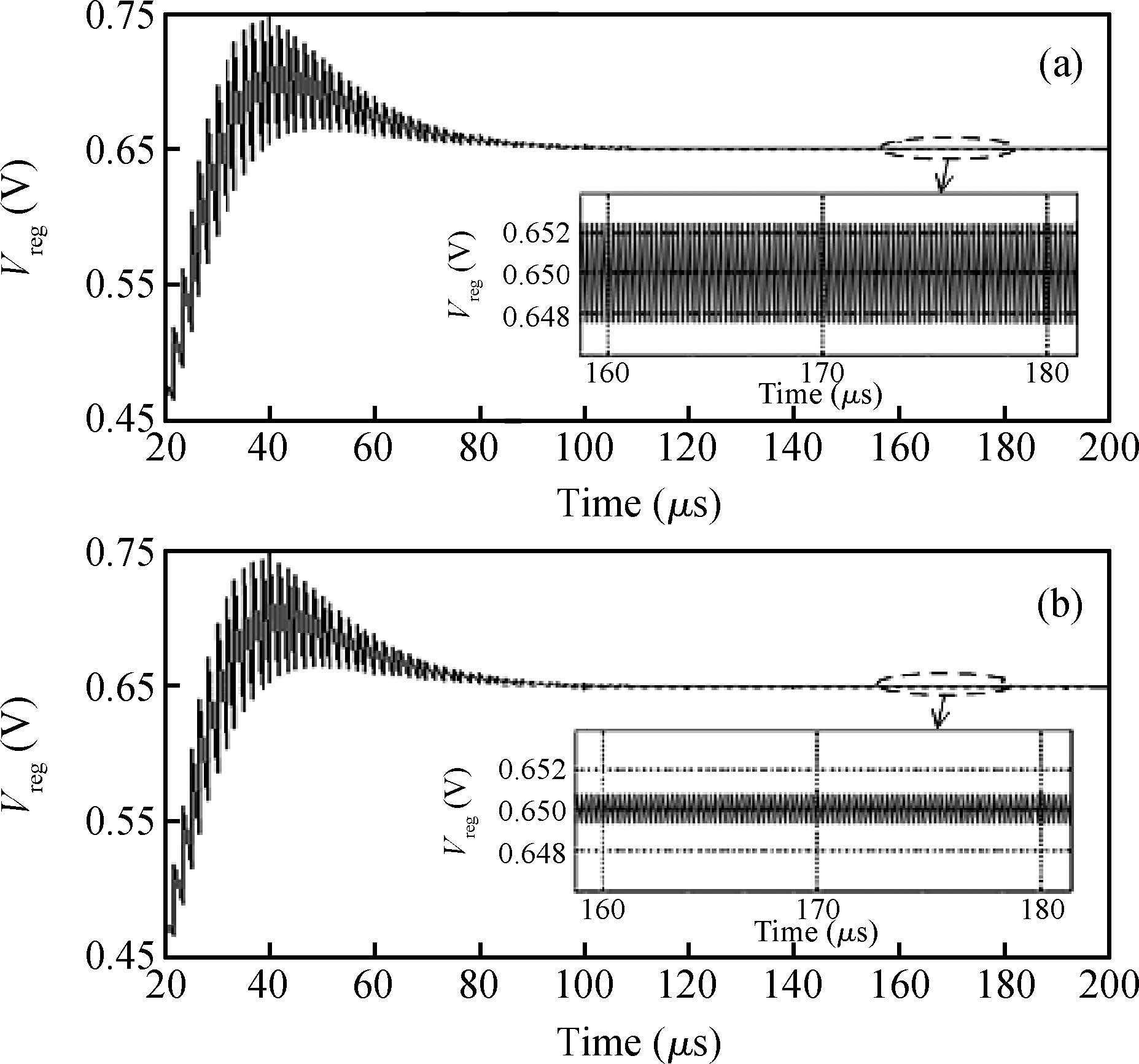

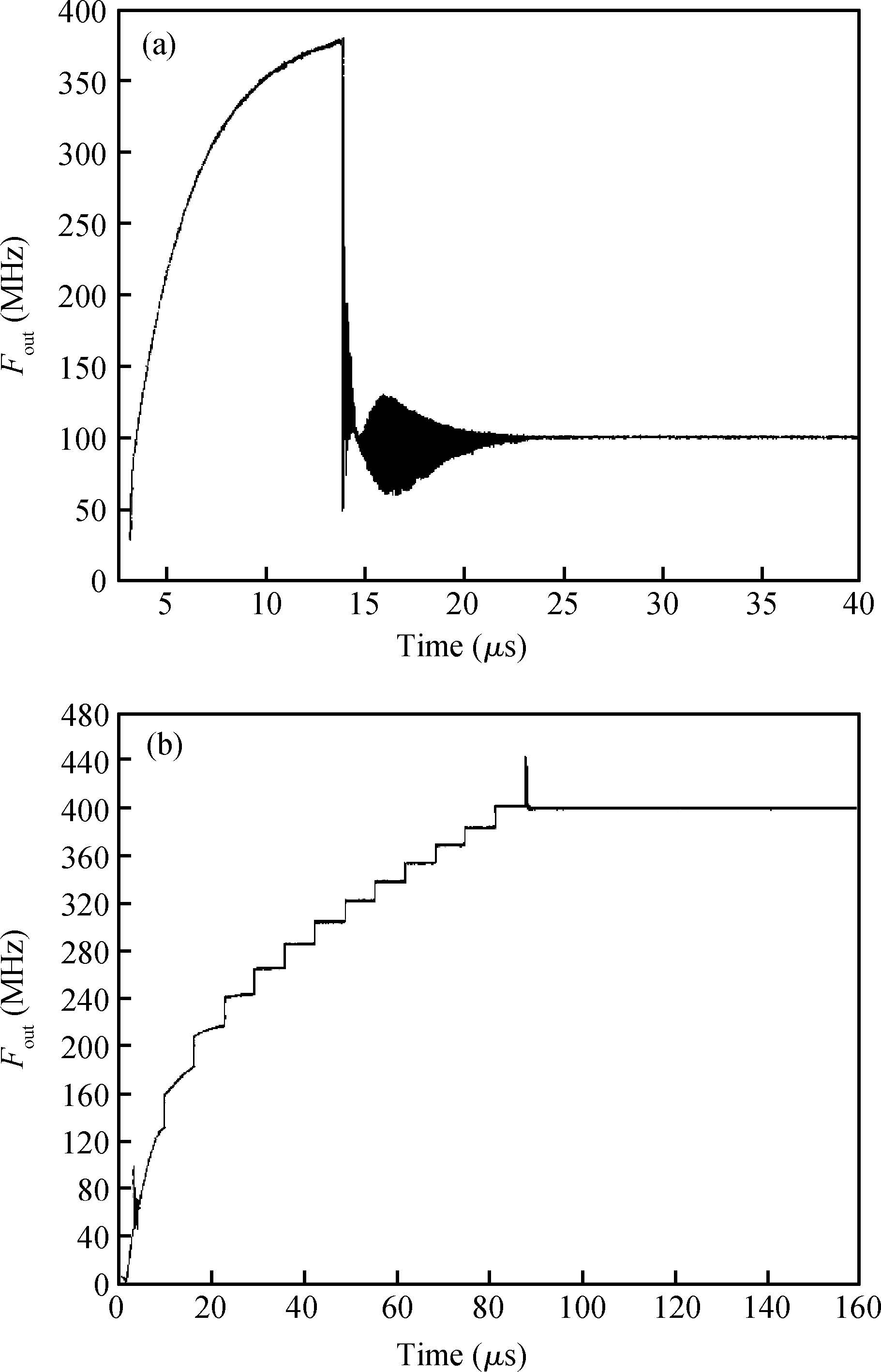

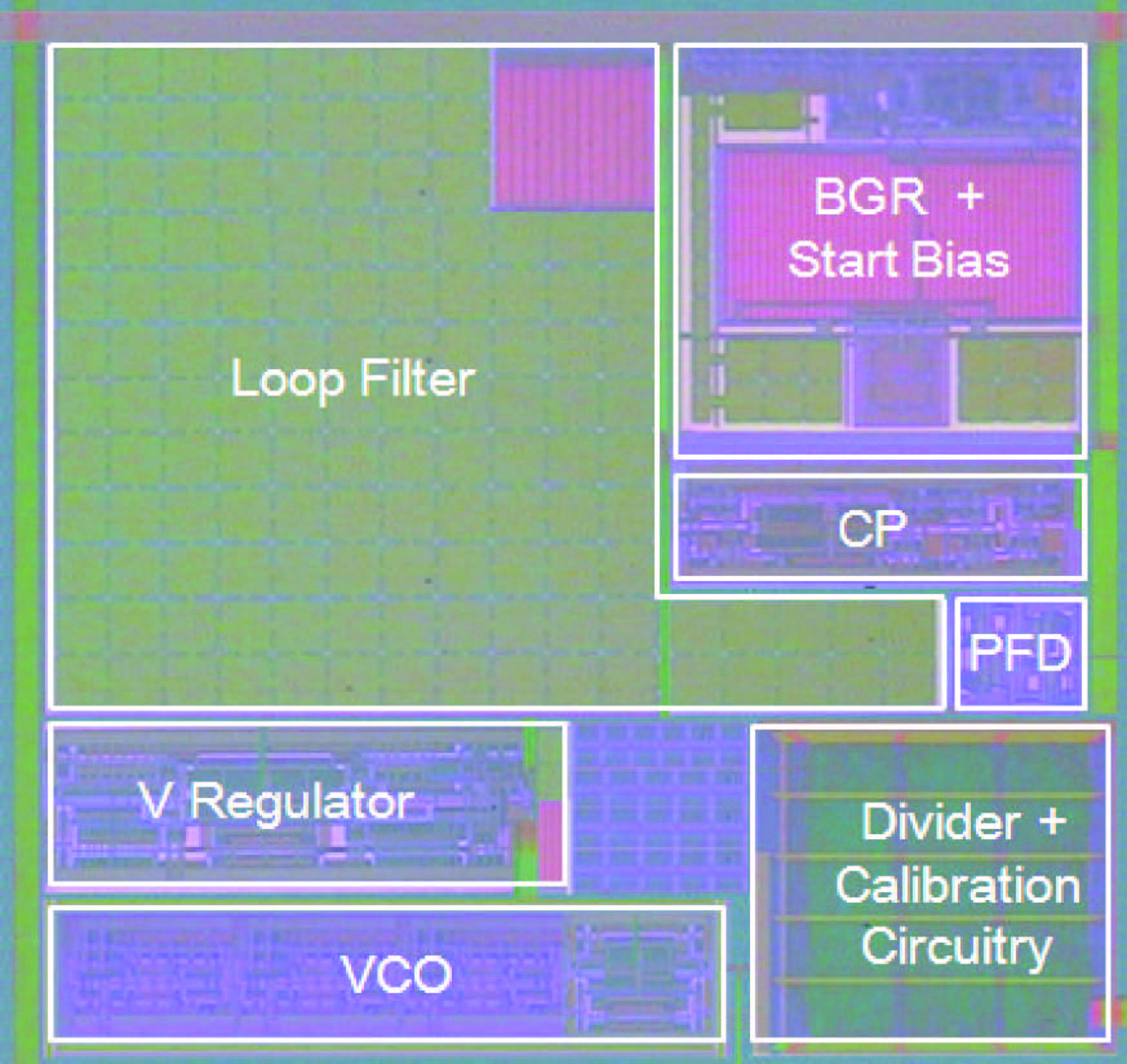

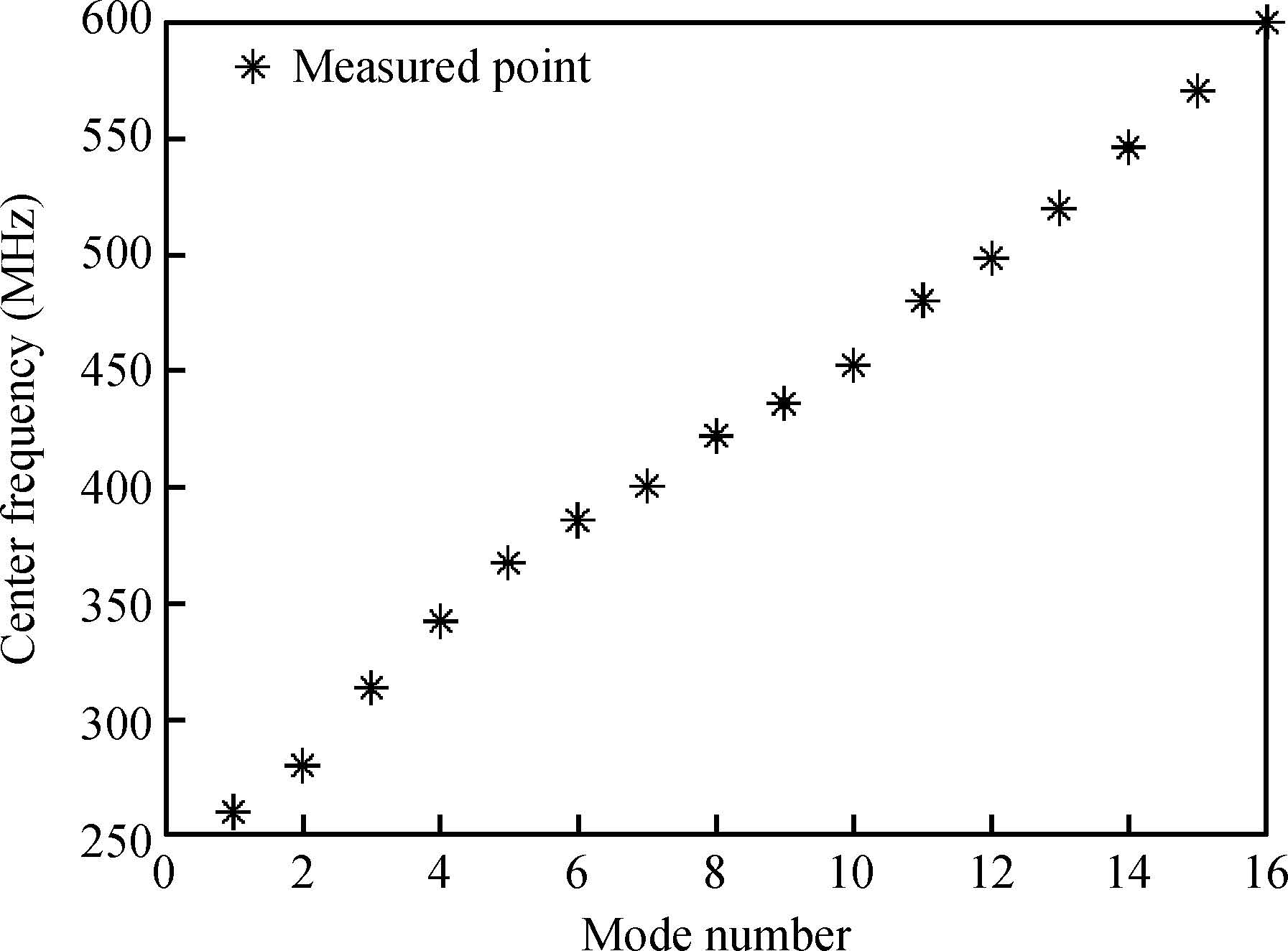

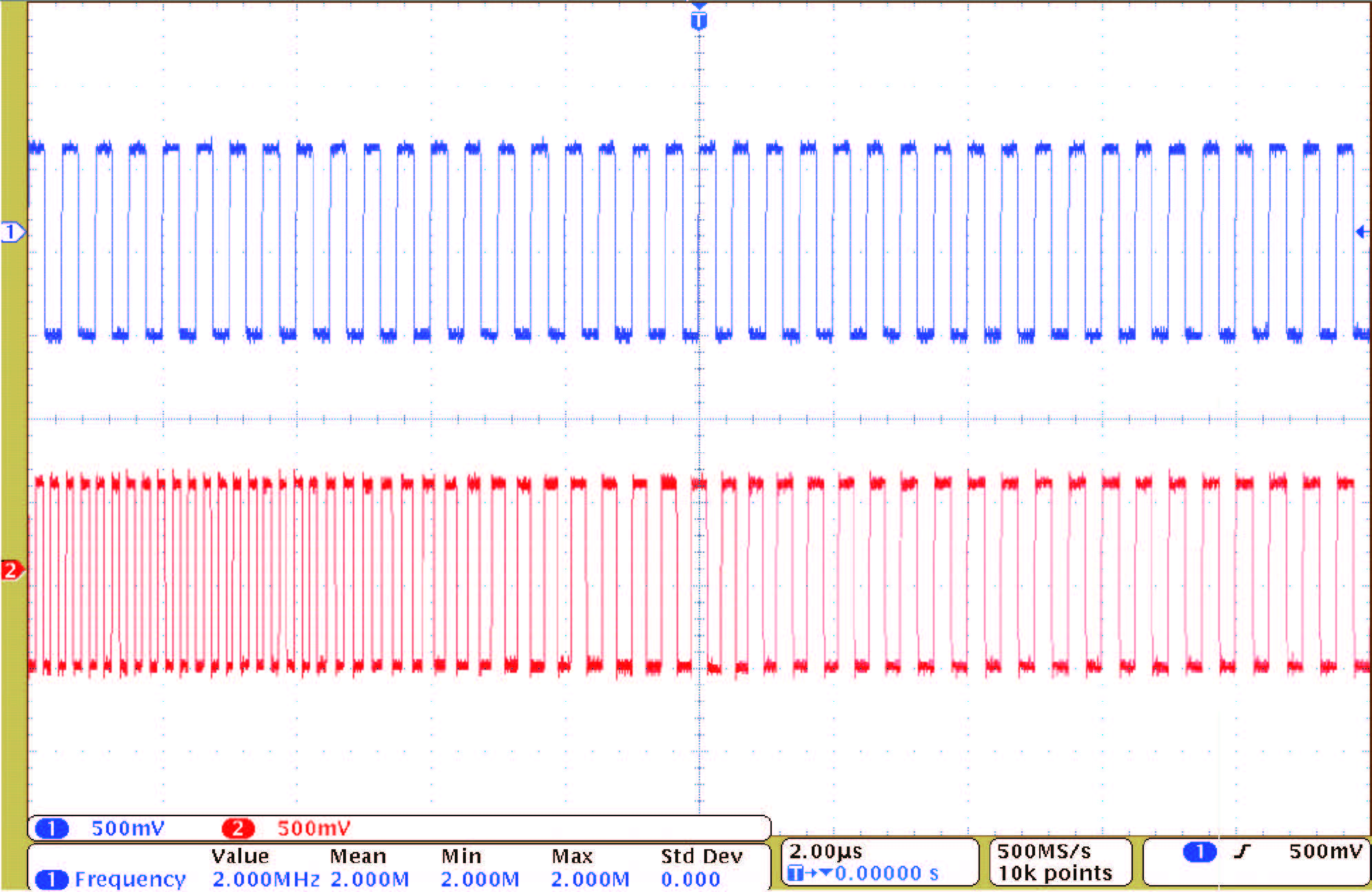

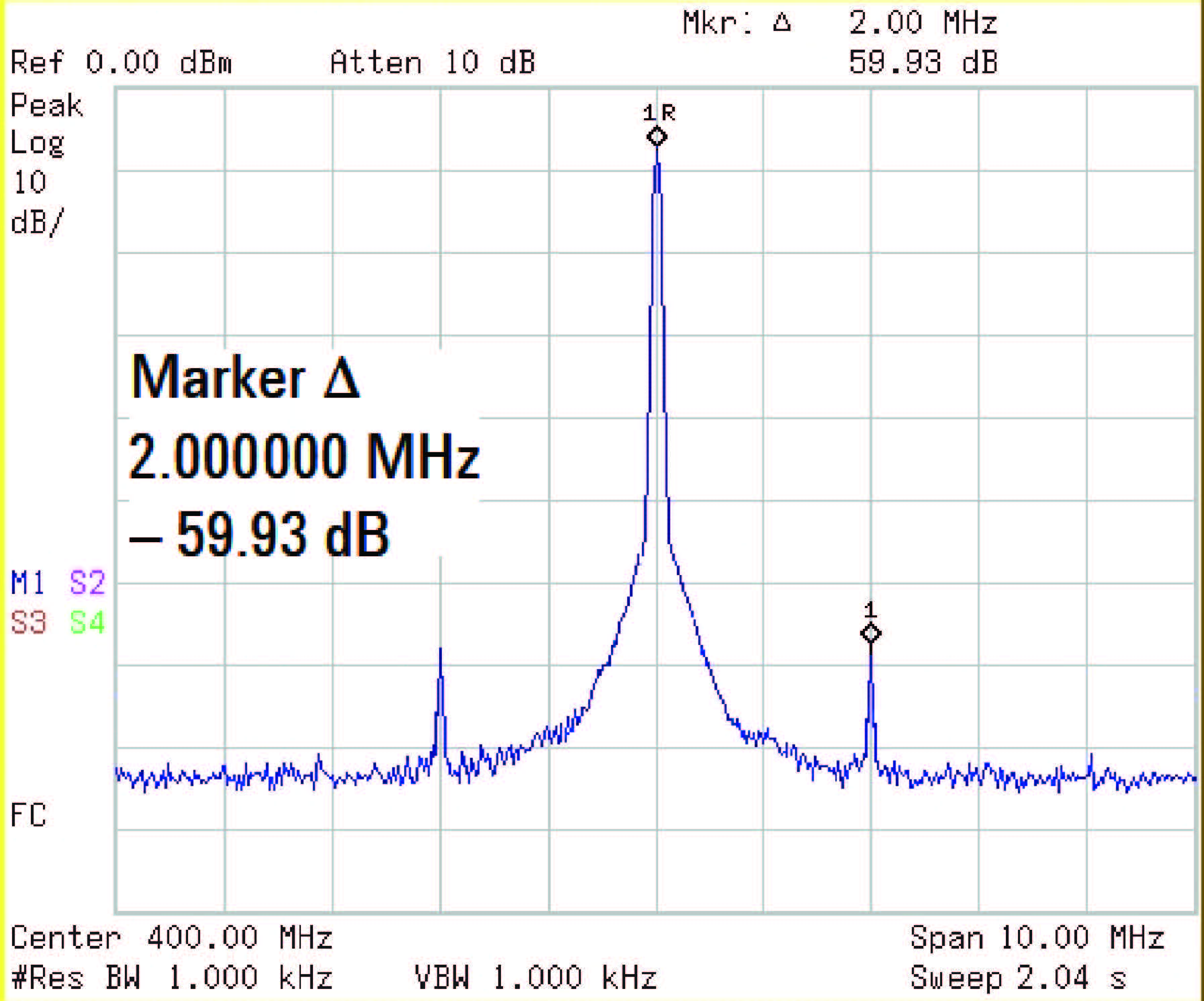

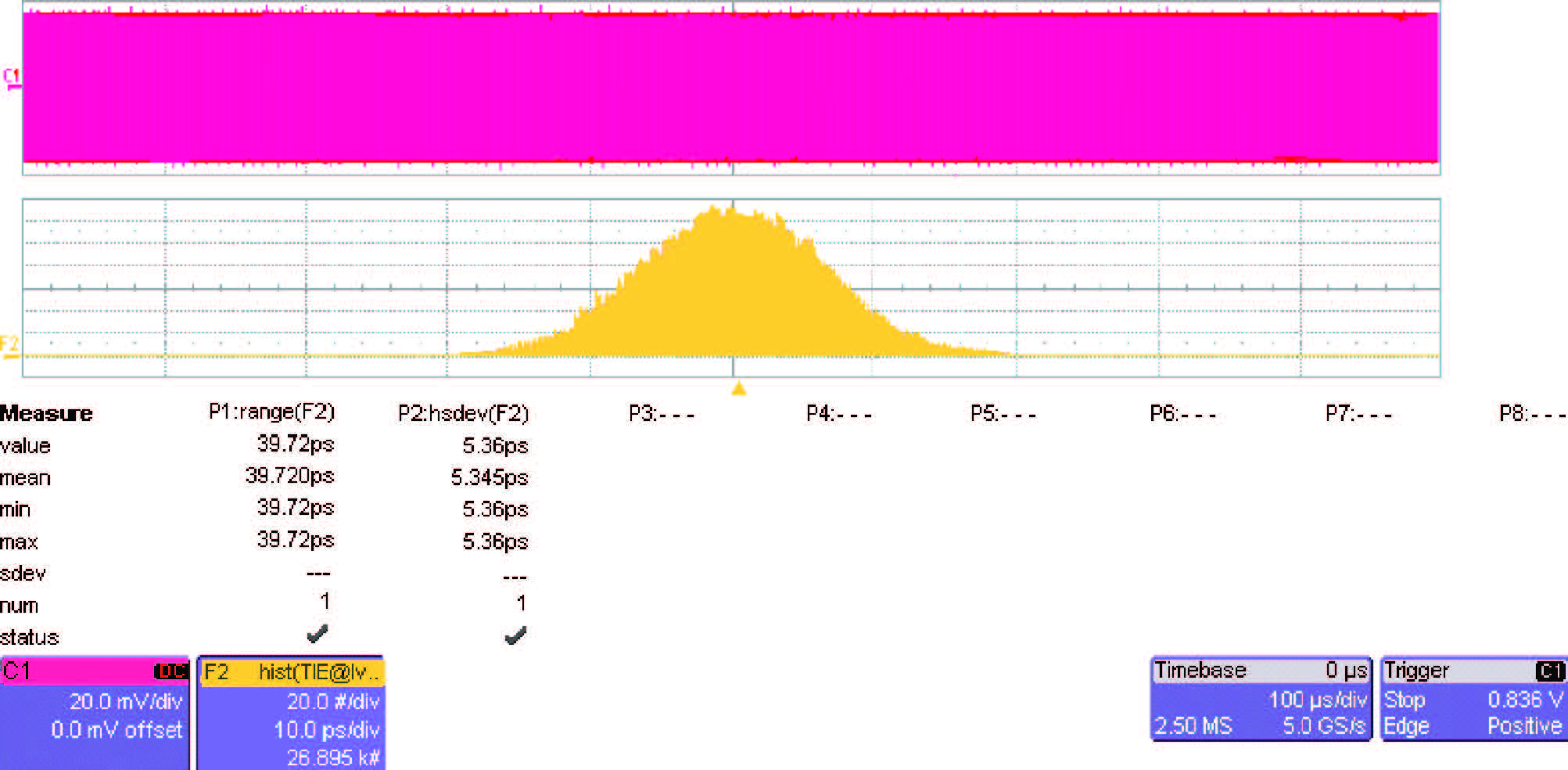

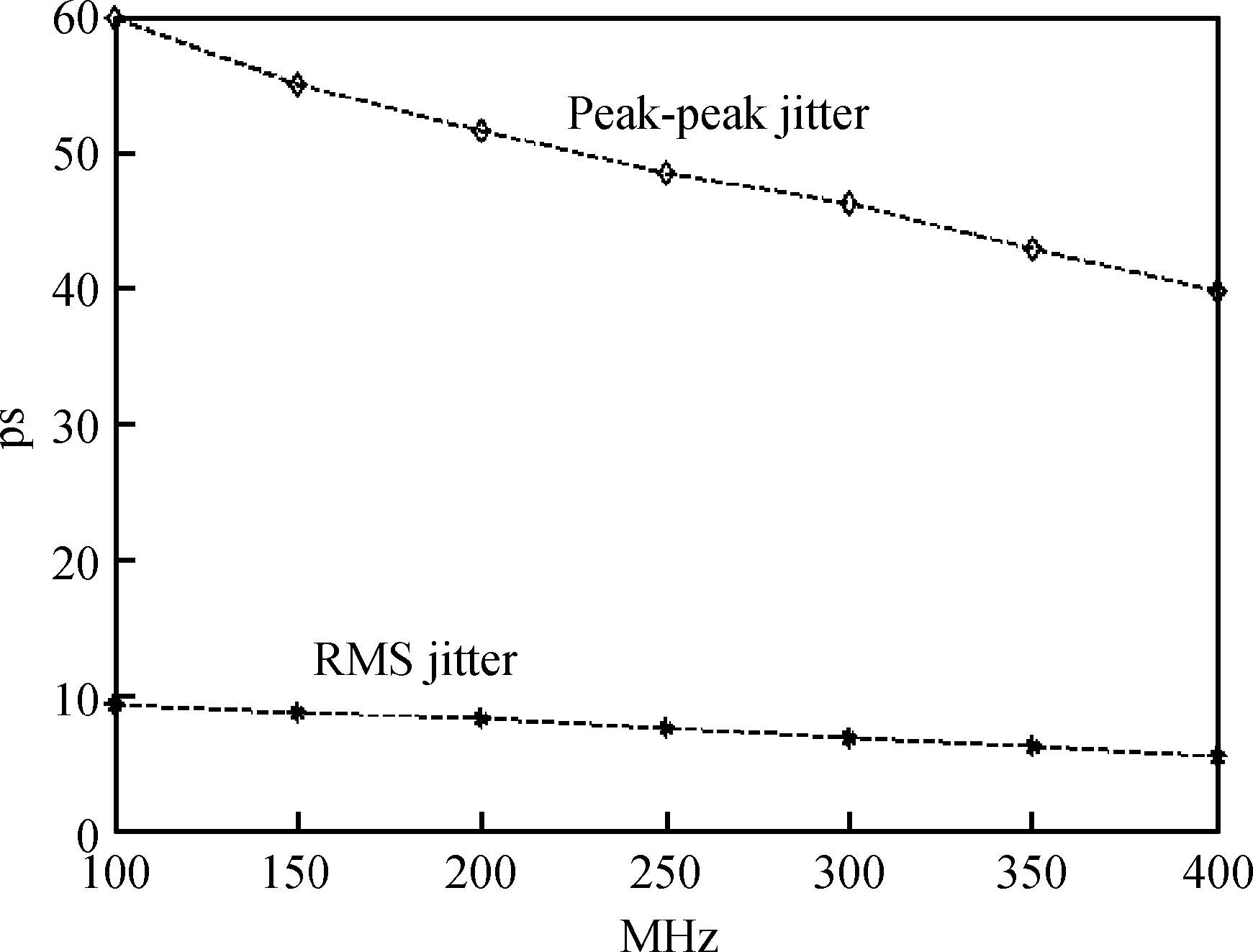

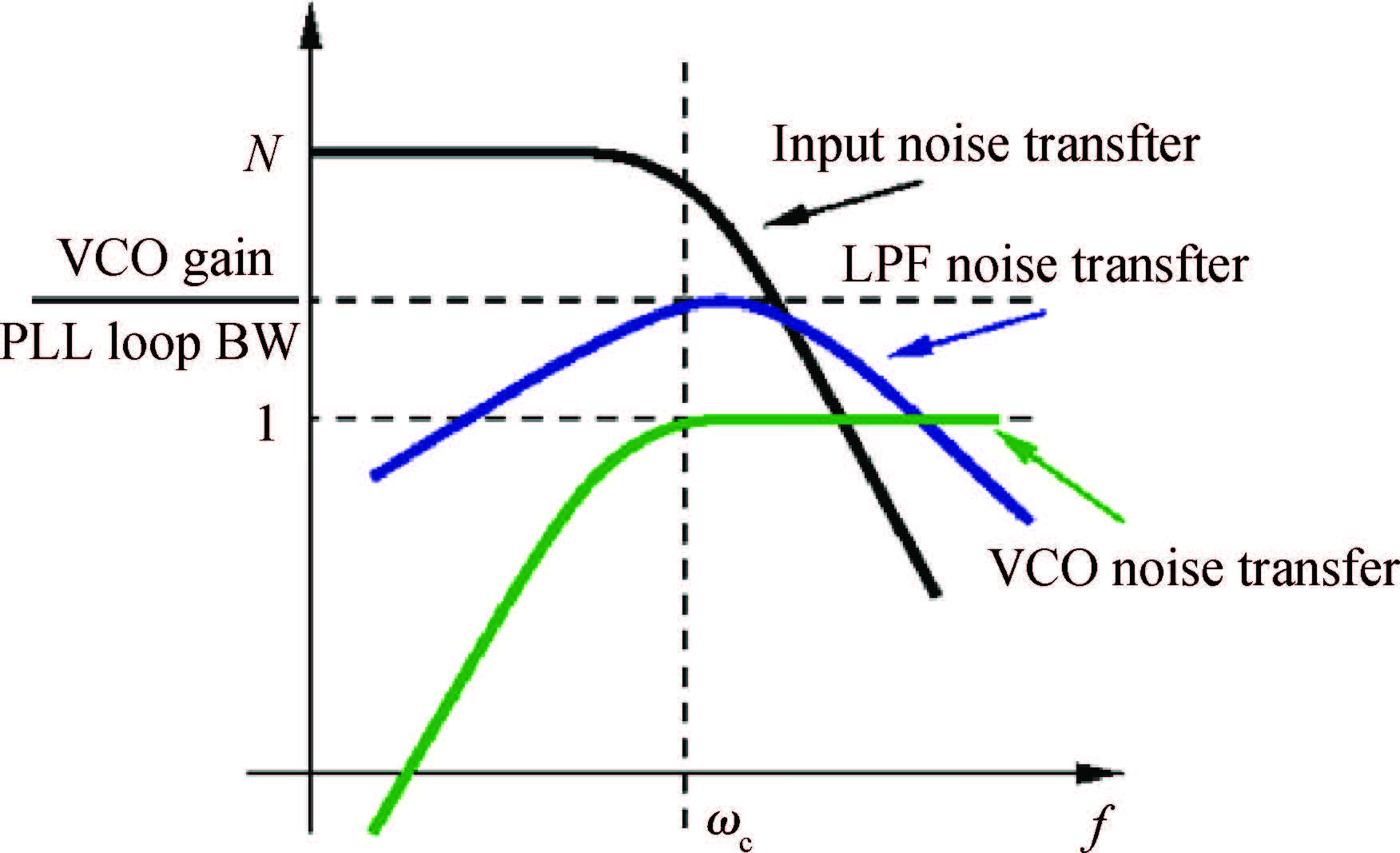

This paper describes a ring oscillator based low jitter charge pump PLL with supply regulation and digital calibration. In order to combat power supply noise, a low drop output voltage regulator is implemented. The VCO gain is tunable by using the 4 bit control self-calibration technique. So that the optimal VCO gain is automatically selected and the process/temperature variation is compensated. Fabricated in the 0.13 μ m CMOS process, the PLL achieves a frequency range of 100-400 MHz and occupies a 190×200 μ m2 area. The measured RMS jitter is 5.36 ps at a 400 MHz operating frequency.-

Keywords:

- phase-locked loop,

- supply regulation,

- self-calibration,

- low jitter

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] -

Proportional views

DownLoad:

DownLoad: