| Citation: |

Zhenhai Chen, Zongguang Yu, Jinghe Wei, Dejin Zhou, Xiaobo Su, Jiaxuan Zou. A 4 Gbps current-mode transmitter for 12-bit 250 MSPS ADC[J]. Journal of Semiconductors, 2017, 38(8): 085008. doi: 10.1088/1674-4926/38/8/085008

****

Z H Chen, Z G Yu, J H Wei, D J Zhou, X B Su, J X Zou. A 4 Gbps current-mode transmitter for 12-bit 250 MSPS ADC[J]. J. Semicond., 2017, 38(8): 085008. doi: 10.1088/1674-4926/38/8/085008.

|

A 4 Gbps current-mode transmitter for 12-bit 250 MSPS ADC

DOI: 10.1088/1674-4926/38/8/085008

More Information

-

Abstract

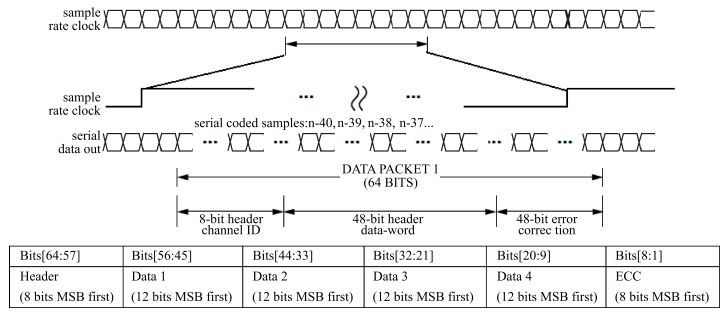

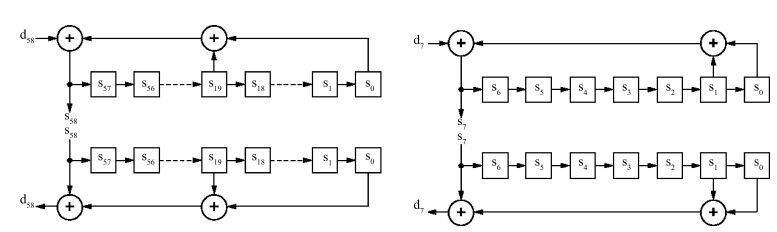

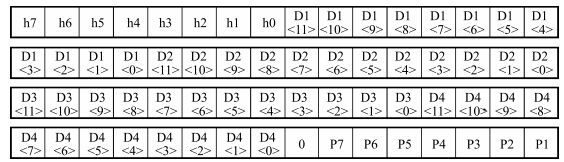

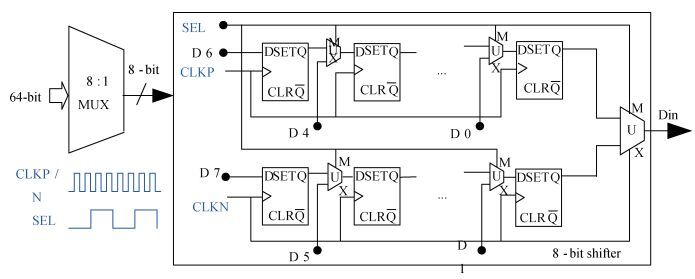

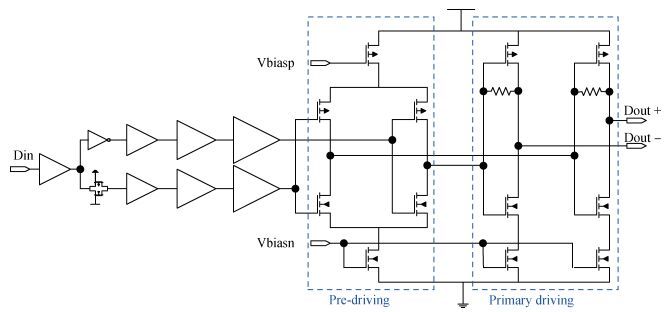

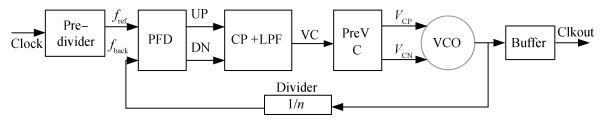

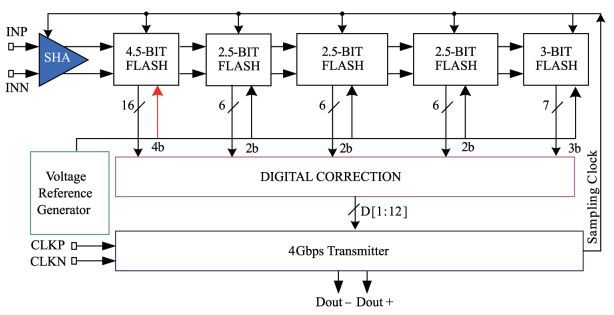

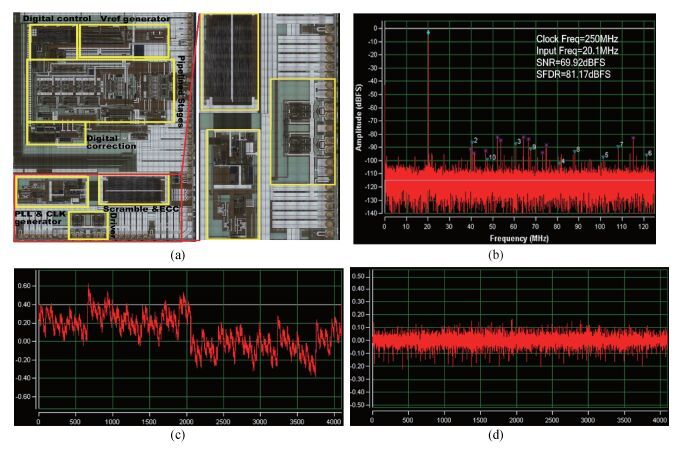

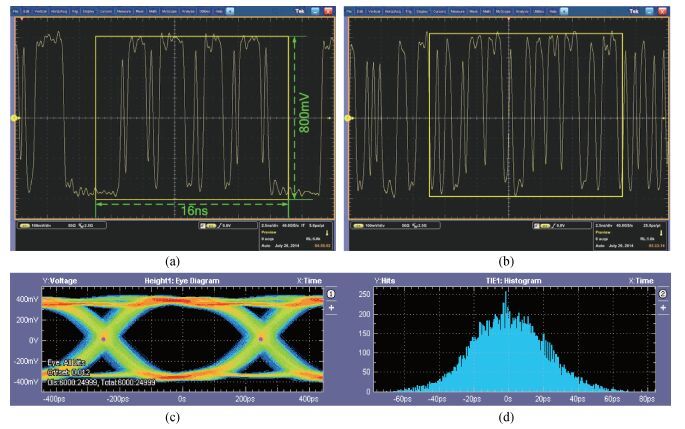

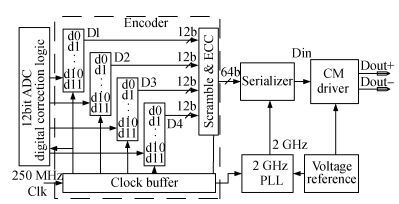

A 4 Gbps transmitter for a 12-bit 250 MSPS pipelined ADCs is presented. A low power current mode (CM) output driver with reverse scaling technique is proposed. A high speed, low power combined serializer is implemented to convert 12 bit parallel data into a seria1 data stream. The whole transmitter is used in a 12-bit 250 MSPS pipelined ADC for the digital output buffer and fabricated in 180 nm 1. 8 V 1P5M CMOS technology. Test results show that the transmitter provides an eye height greater than 800 mV for data rates of both 2 Gbps and 4 Gbps, the 12-bit 250 MSPS ADC achieves the SNR of 69.92 dBFS and SFDR of 81.17 dB with 20.1 MHz input at full sampling speed. The ADC with the 4 Gbps transmitter consumes the power consumption of 395 mW, where the power consumption of transmitter is 75 mW. The ADC occupies an area of 2.5×3.2 mm2, where the active area of the transmitter block is 0.5×1.2 mm2.-

Keywords:

- interface,

- pipelined ADC,

- transmitter,

- current mode

-

References

[1] Fukuda K, Yamashita H, Ono G, et al. A 123 mW 125 Gbps complete transceiver in 65 nm CMOS process. IEEE J Solid-State Circuits, 2010, 45(12):2838 doi: 10.1109/JSSC.2010.2075410[2] Liu Y, Hsieh P H, Kim S, et al. A 0.1 pJ/b 5-to-10Gb/s chargerecycling stacked low-power I/O for on-chip signaling in 45 nm CMOS SOI. IEEE J Solid-State Circuits, 2013, 48(12):2905[3] Lv J, Ju H, Yuan L, et al. A high speed lowjitter LVDs output driver for serial links. Springer Analog Integrated Circuit and Signal Processing, 2011, 68(3):387 doi: 10.1007/s10470-011-9658-x[4] Han S, Lee S, Choi M, et al. A coefficient-error-robust FFE TX with 230% eye-variation improvement without calibration in 65 nm CMOS technology. Proc ISSCC, 2014:50[5] Kim B, Liu Y, Dickson O, et al. A 10-Gb/s compact low-power serial I/O with DFE-ⅡR equalization in 65-nm CMOS. IEEE J Solid-State Circuits, 2009, 44(12):3526 doi: 10.1109/JSSC.2009.2031015[6] Schrader J, Klumperrink E A M, Visschers J, et al. Pulse width modulation preemphasis applied in a wireline transmitter, achieving 33 dB loss compensation at 5 Gbps in 0.13 m CMOS. IEEE J Solid-State Circuits, 2009, 41(4):990[7] Zhang M K, Hu Q S. A 6.25 Gb/s equalizer in 0.18 m CMOS technology for high-speed SerDes. J Semicond, 2013, 34(12):125010 doi: 10.1088/1674-4926/34/12/125010[8] Ln J S, Ju H, Ye M, et al. A 5 Gb/s low power current-mode transmitter with pre-emphasis for serial links. J Semicond, 2013, 34(7):075002 doi: 10.1088/1674-4926/34/7/075002[9] Bei P, Guang Z H, Hao L, et al. A 48-mW, 12-bit, 150-MS/s pipelined ADC with digital calibration in 65 nm CMOS. IEEE Custom Integrated Circuits, San Jose, CA, USA, 2011:1 http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6055421[10] Xuan W, Chang Y Y, Xiao X Z, et al. A 12-bit, 270 MS/s pipelined ADC with SHA-eliminating front end. IEEE Int Circ Syst, Seoul, Korea, 2012:798[11] Liechti T, Tajalli A, Akgun O C, et al. A 1.8 V 12-bit 230-MS/s pipeline ADC in 0.18 m CMOS technology. IEEE Int Circ Syst, Macao, China, 2008:21 http://infoscience.epfl.ch/record/131146/files/08_APCCAS_MADC.pdf[12] Wang R, Chio U F, Sin S W, et al. A 12-bit 110-MS/s 4-stage single-opamp pipelined SAR ADC with ratio-based GEC technique. Proc ESSCIRC, Bordeaux, France, 2012:265[13] Shin S K, Rudell J C, Daily D C, et al. A 12-bit, 20 MS/s zerocrossing based pipelined ADC with early sub-ADC decision and output residue background calibration. IEEE J Solid-State Circuits, 2014, 49(6):1366 doi: 10.1109/JSSC.2014.2322853 -

Proportional views

DownLoad:

DownLoad: