| Citation: |

G. Prasad Acharya, M. Asha Rani. Berger code based concurrent online self-testing of embedded processors[J]. Journal of Semiconductors, 2018, 39(11): 115001. doi: 10.1088/1674-4926/39/11/115001

****

G P Acharya, M A Rani, Berger code based concurrent online self-testing of embedded processors[J]. J. Semicond., 2018, 39(11): 115001. doi: 10.1088/1674-4926/39/11/115001.

|

Berger code based concurrent online self-testing of embedded processors

DOI: 10.1088/1674-4926/39/11/115001

More Information

-

Abstract

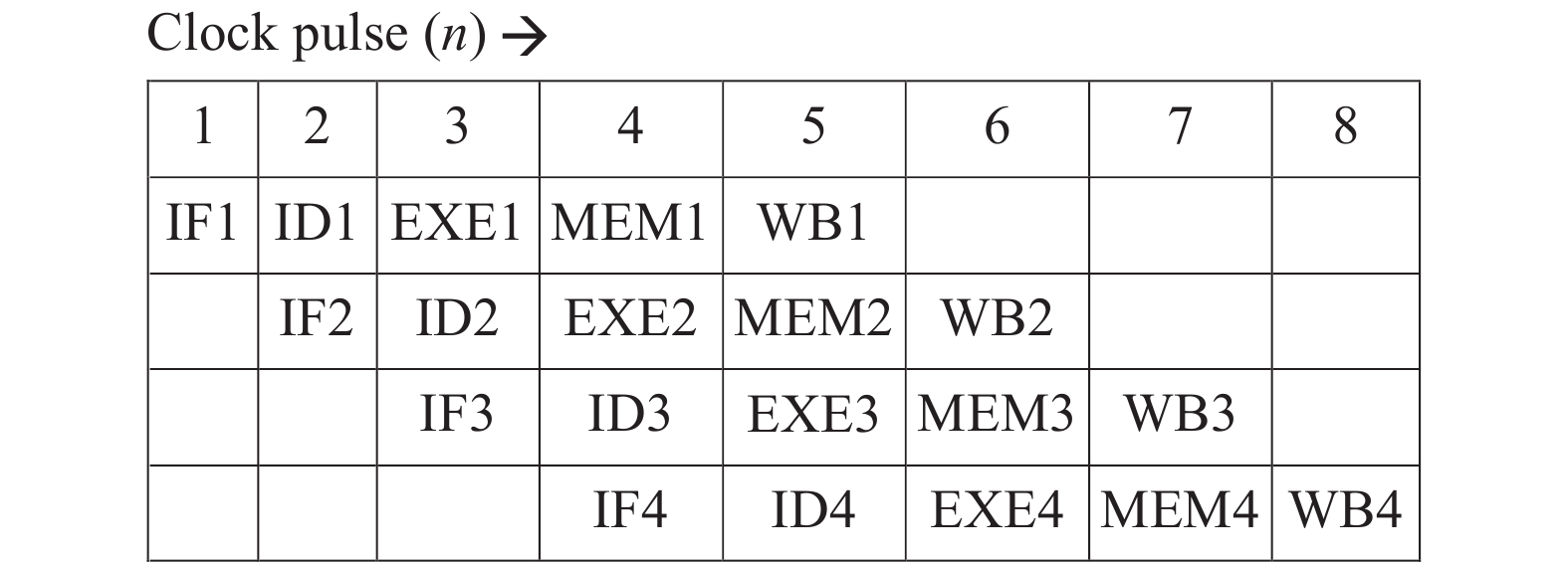

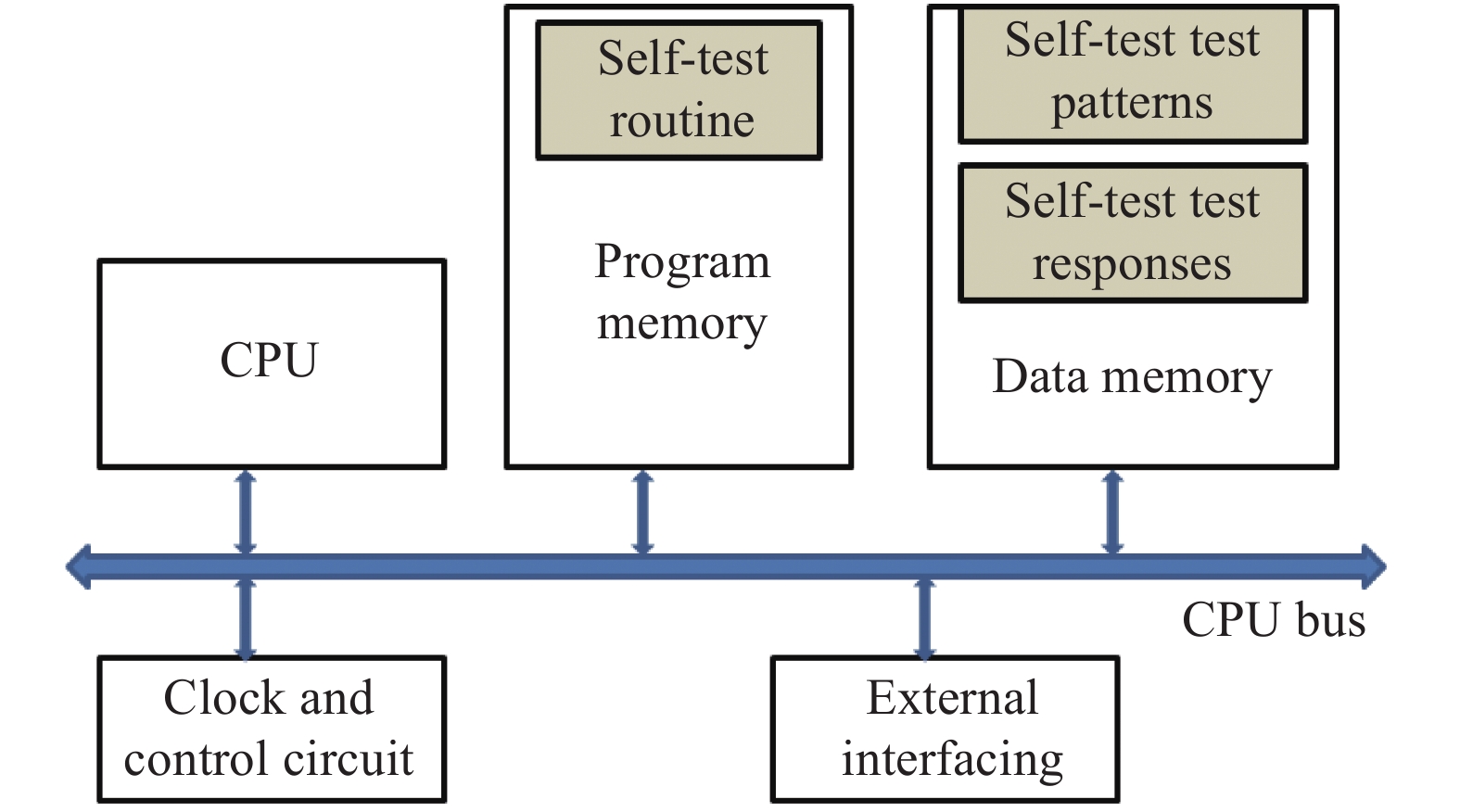

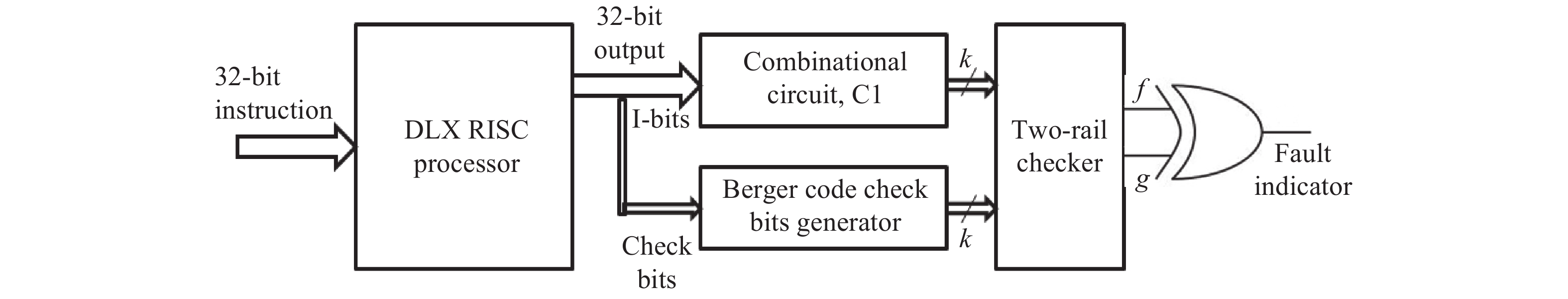

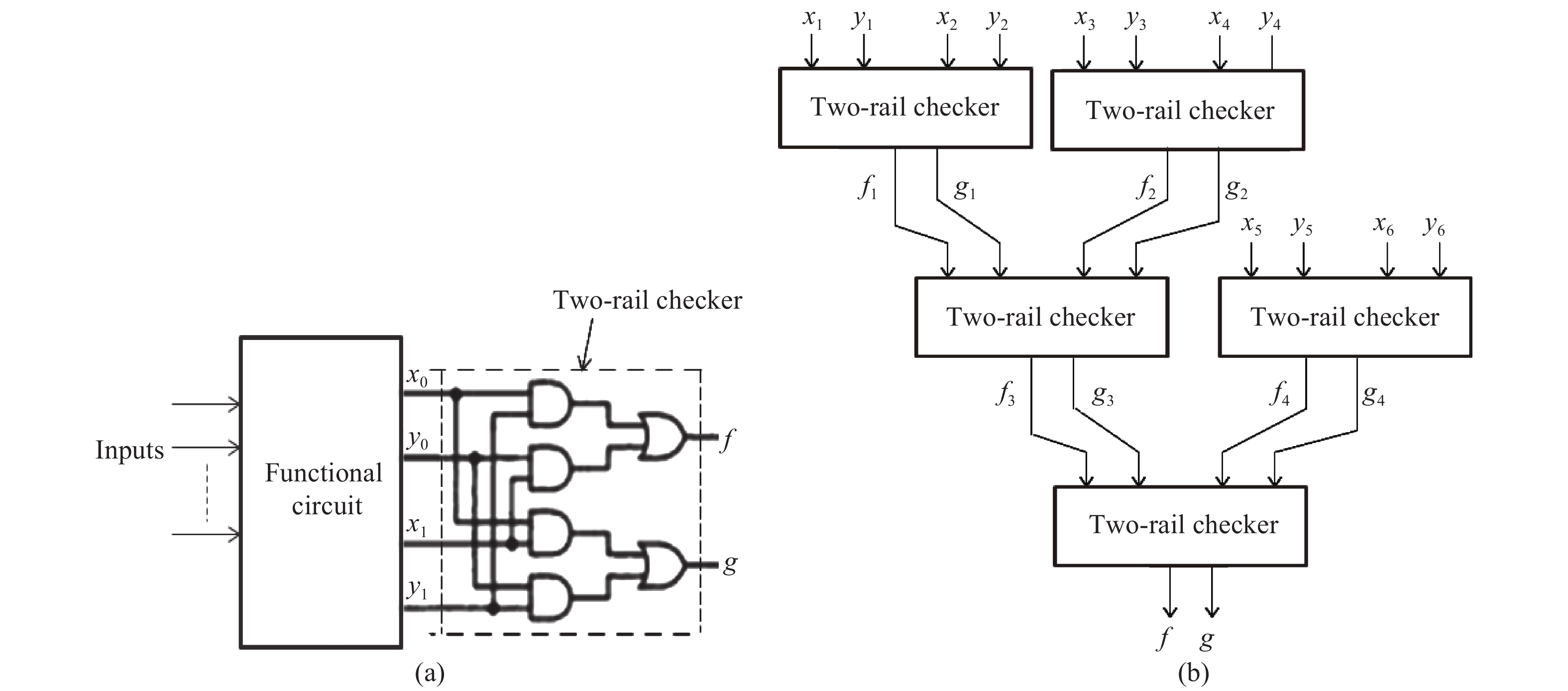

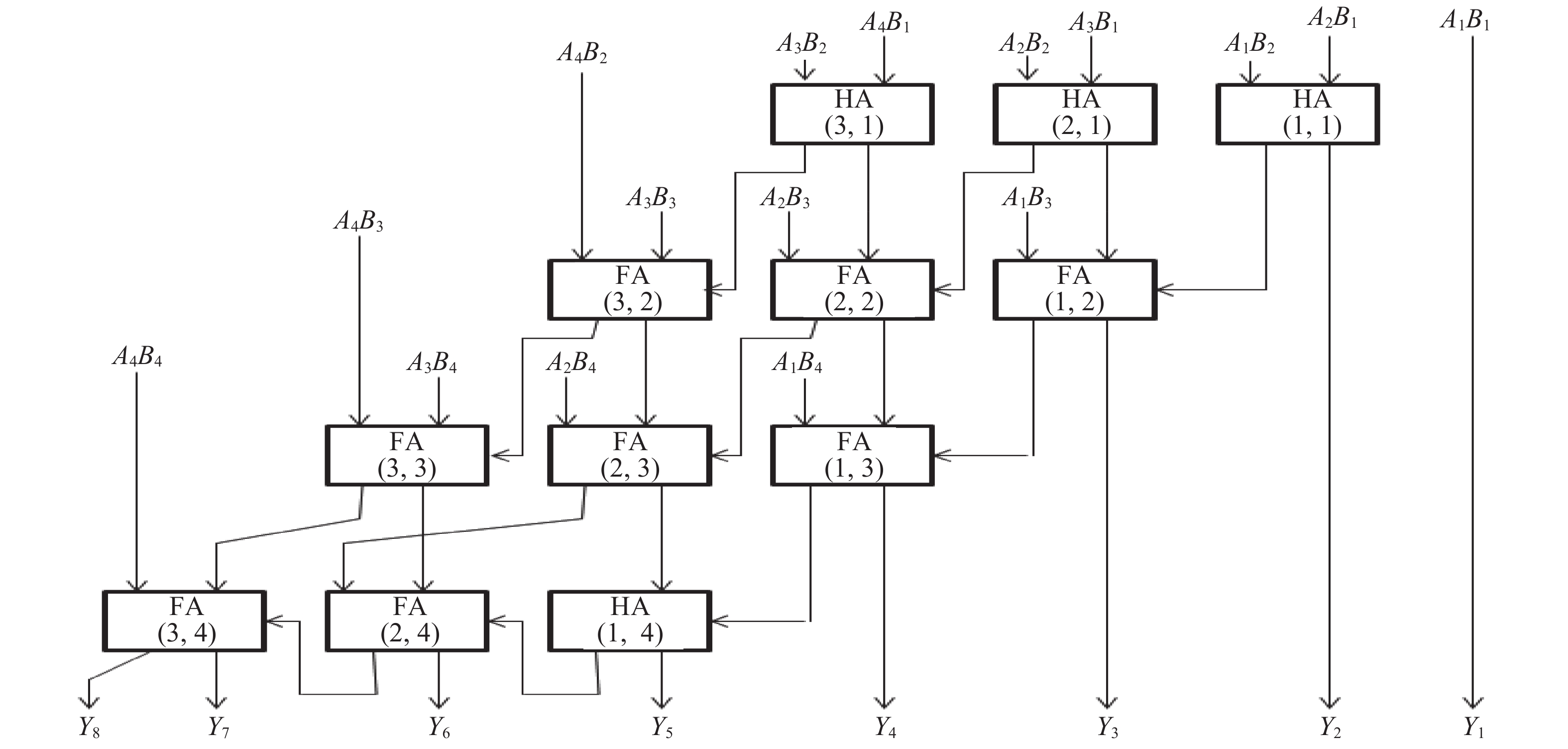

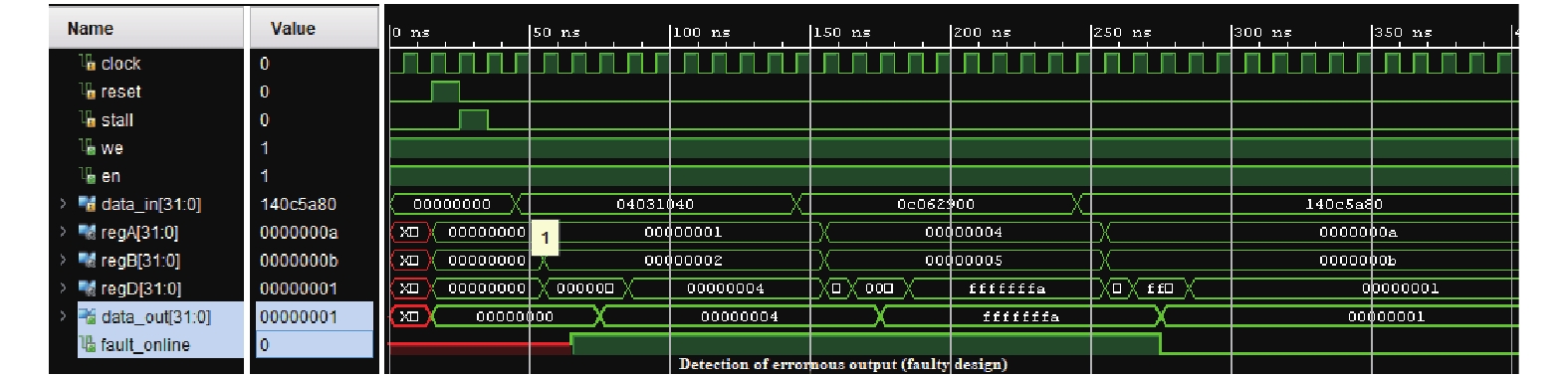

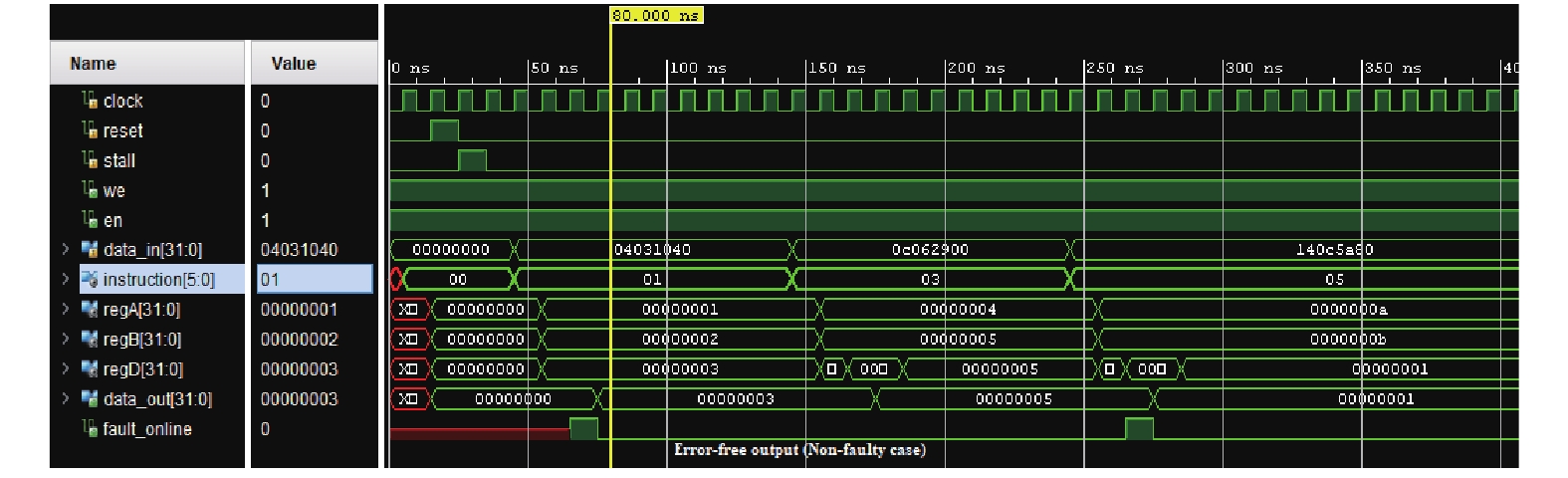

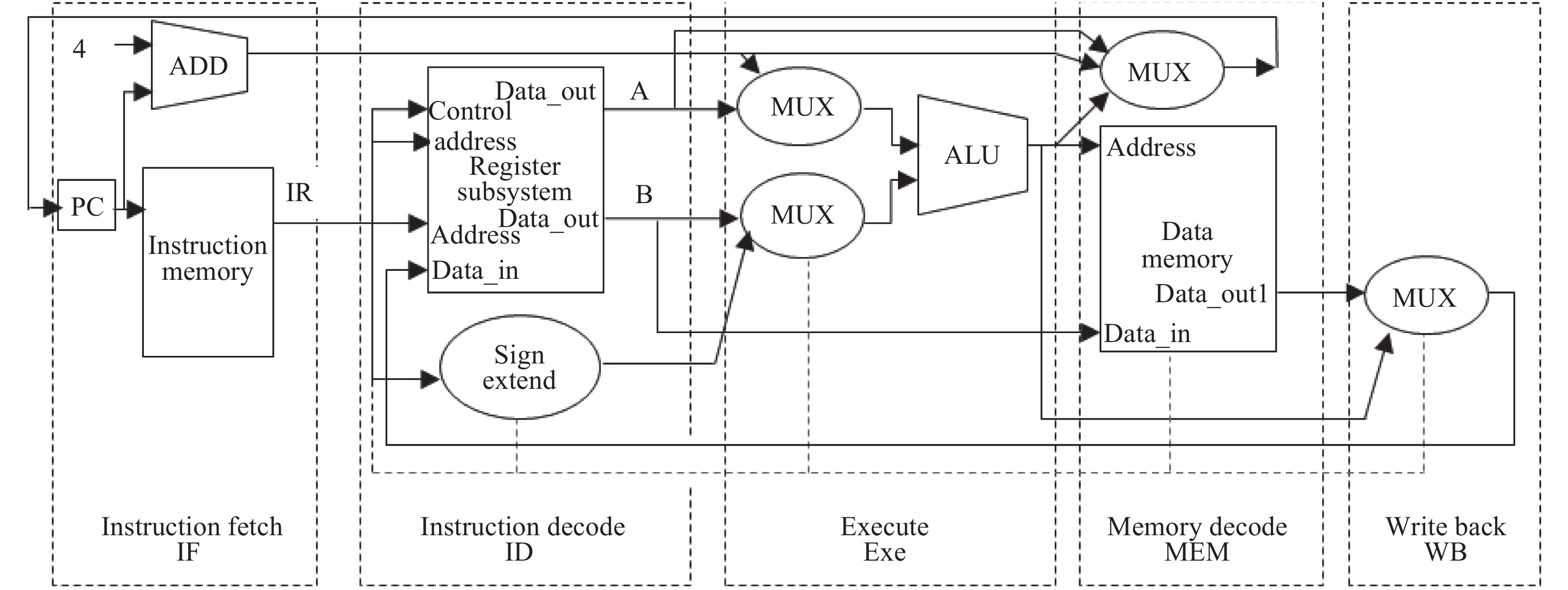

We propose an approach to detect the temporary faults induced by an environmental phenomenon called single event upset (SEU). Berger code based self-checking checkers provides an online detection of faults in digital circuits as well as in memory arrays. In this work, a concurrent Berger code based online self- testable architecture is proposed and integrated in 32-bit DLX reduced instruction set computer (RISC) processor on a single silicon chip. The proposed concurrent test methodology is implemented and verified for various arithmetic and logical operations of the DLX processor. The FPGA implementation of the proposed design shows that a meager increase in hardware utilization facilitates online self-testing to detect temporary faults.-

Keywords:

- single event upset,

- Berger code,

- DLX RISC,

- online testing

-

References

[1] Binu D, Kariyappa B S. A survey on fault diagnosis of analog circuits: taxonomy and state of the art. Int J Electron Commun, 2017, 73: 68 doi: 10.1016/j.aeue.2017.01.002[2] Constantinescu C. Intermittent faults in VLSI circuits. Proceedings of the IEEE Workshop on Silicon Errors in Logic - System Effects, 2007[3] Blough D M, Sullivan G F, Masson G M. Intermittent fault diagnosis in multiprocessor systems. IEEE Trans Comput, 1992, 41(11): 1430 doi: 10.1109/12.177313[4] Borkar S. Microarchitecture and design challenges for gigascale integration. Proceedings of the 37th annual IEEE/ACM International Symposium on Microarchitecture, Portland, Oregon, 2004[5] Constantinescu C. Trends and challenges in VLSI circuit reliability. IEEE Micro, 2003, 23(4): 14 doi: 10.1109/MM.2003.1225959[6] Contant O, Lafortune S D. Diagnosis of intermittent faults. Discrete Event Dynamic Systems, 2004, 14(2): 171 doi: 10.1023/B:DISC.0000018570.20941.d2[7] ElAarag H. A complete design of a RISC processor for pedagogical purposes. J Comput Sci Colleg, 2009, 25(2): 205[8] Ravi S, Joseph M. FPGA implementation of low power self testable MIPS processor. Am-Eur J Sci Res, 2017, 12(3): 135[9] Acharya G P, Rani M A. Design of online self-testable multi-core system using dynamic partial reconfiguration of FPGA. Int J Appl Eng Res, 2017, 12(24): 15261[10] Psarakis M, Gizopoulos D, Sanchez E. Microprocessor software-based self-testing. IEEE Design & Test of Computers, 2010: 4[11] Wen C H P, Wang L C. Simulation- based functional test generation for embedded processors. IEEE Trans Comput, 2006, 55(11): 1335 doi: 10.1109/TC.2006.186[12] Kranitis N, Paschalis A, Gizopoulos D. Software-based self-testing of embedded processors. IEEE Trans Comput, 2005, 54(4): 461 doi: 10.1109/TC.2005.68[13] Psarakis M, Gizopoulos D, Hatzimihail M. Systematic software-based self- test for pipelined processors. IEEE Trans Very Large Scale Integr Syst, 2008, 16(11): 1441 doi: 10.1109/TVLSI.2008.2000866[14] Batcher K, Papachristou C. Instruction randomization self-test for processor cores. Proc 17th IEEE VLSI Test Symposium, 1999: 34.[15] Gizopoulos D, Paschalis A, Zorian Y. Embedded processor-based self-test. Kluwer Academic Publishers, 2013[16] Lo J, Thanawastien S, Rao T R N. Concurrent error correction in arithemetic and logical operations using Berger codes. Proceedings of the 9th Symposium on Computer Arithmetic, Santa Monica, CA, 1989: 233[17] Kavousianos X, Nikolos D, Foukarakis G. New efficient totally Self-checking Berger code checkers. Integration, the VLSI Journal, 1999, 28: 101 doi: 10.1016/S0167-9260(99)00013-9[18] Lala P K. Fault tolerant and fault testable hardware design. Prentice-Hall International, 1985[19] Lala P K. Self-checking and fault-tolerant digital design. Morgan Kaufmann, 2001 -

Proportional views

DownLoad:

DownLoad: