| Citation: |

Jing Leng, Yangyang Lu, Yunwu Zhang, Huan Xu, Kongsheng Hu, Zhicheng Yu, Weifeng Sun, Jing Zhu. A 0.19 ppm/°C bandgap reference circuit with high-PSRR[J]. Journal of Semiconductors, 2018, 39(9): 095002. doi: 10.1088/1674-4926/39/9/095002

****

J Leng, Y Y Lu, Y W Zhang, H Xu, K S Hu, Z C Yu, W F Sun, J Zhu, A 0.19 ppm/°C bandgap reference circuit with high-PSRR[J]. J. Semicond., 2018, 39(9): 095002. doi: 10.1088/1674-4926/39/9/095002.

|

A 0.19 ppm/°C bandgap reference circuit with high-PSRR

DOI: 10.1088/1674-4926/39/9/095002

More Information

-

Abstract

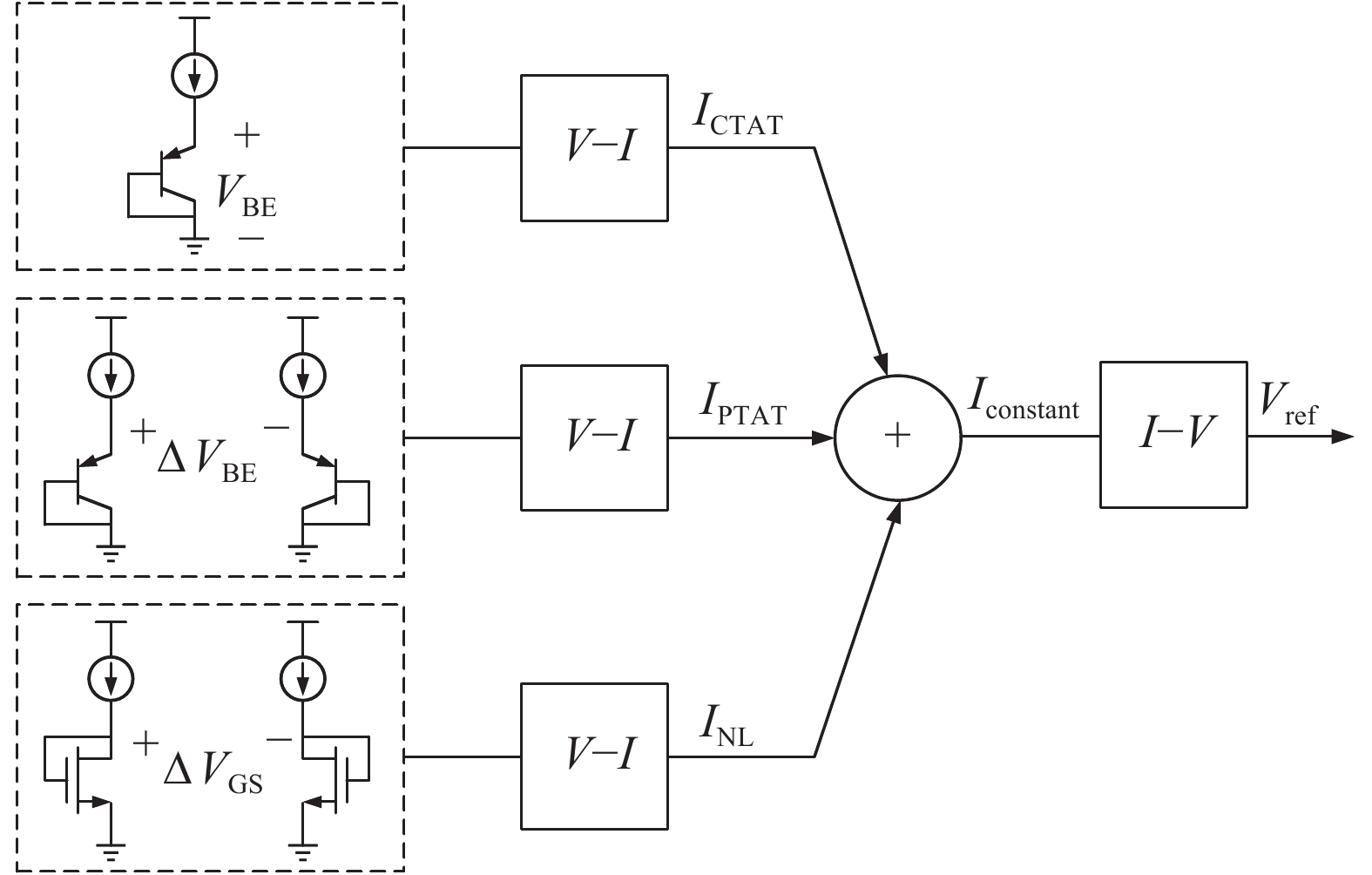

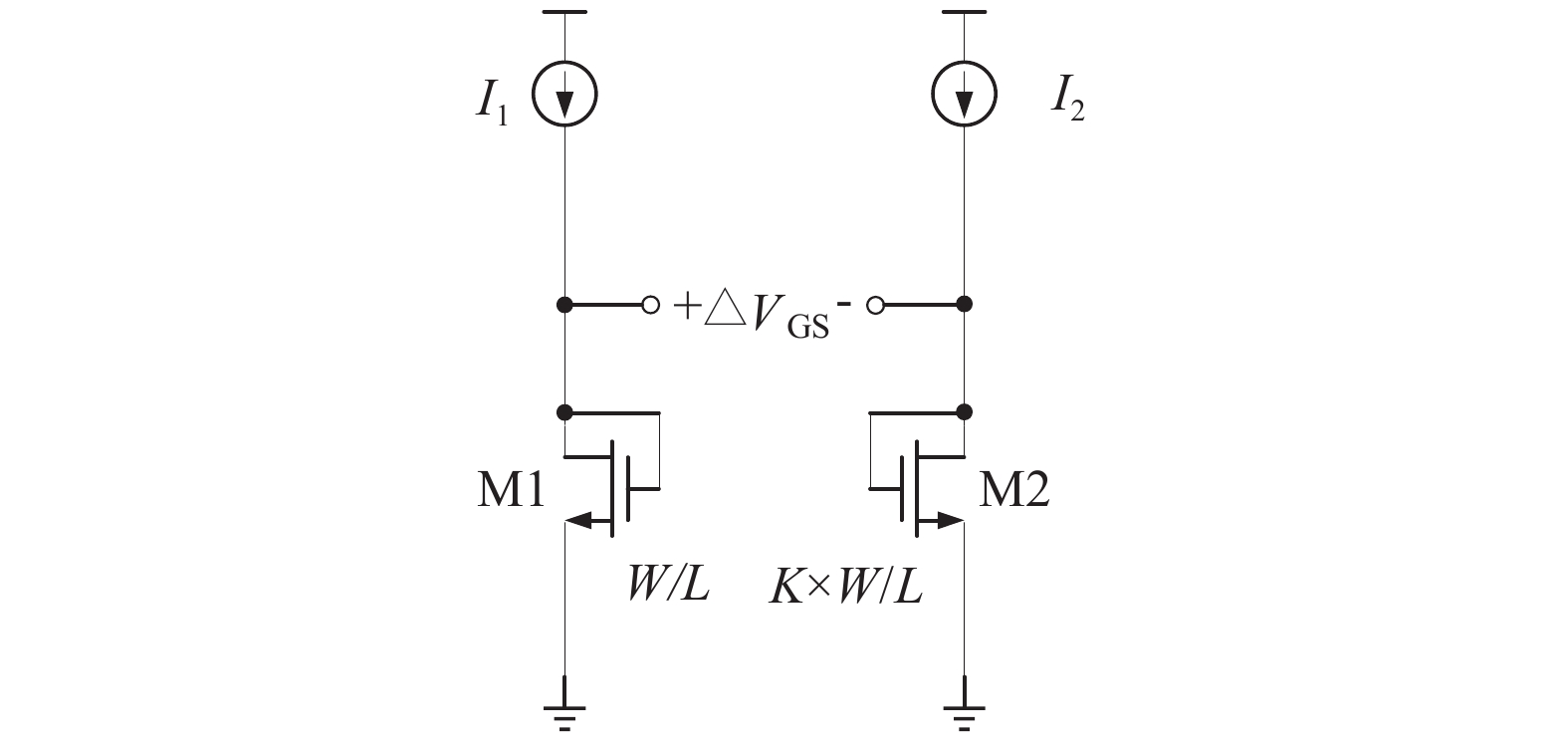

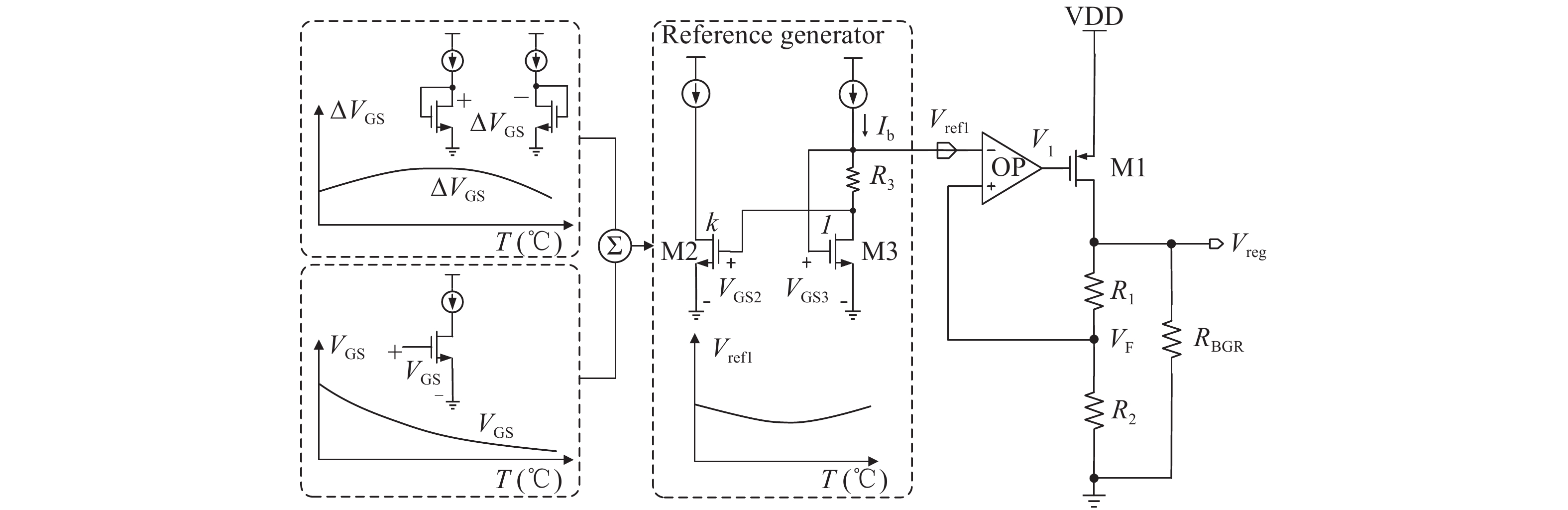

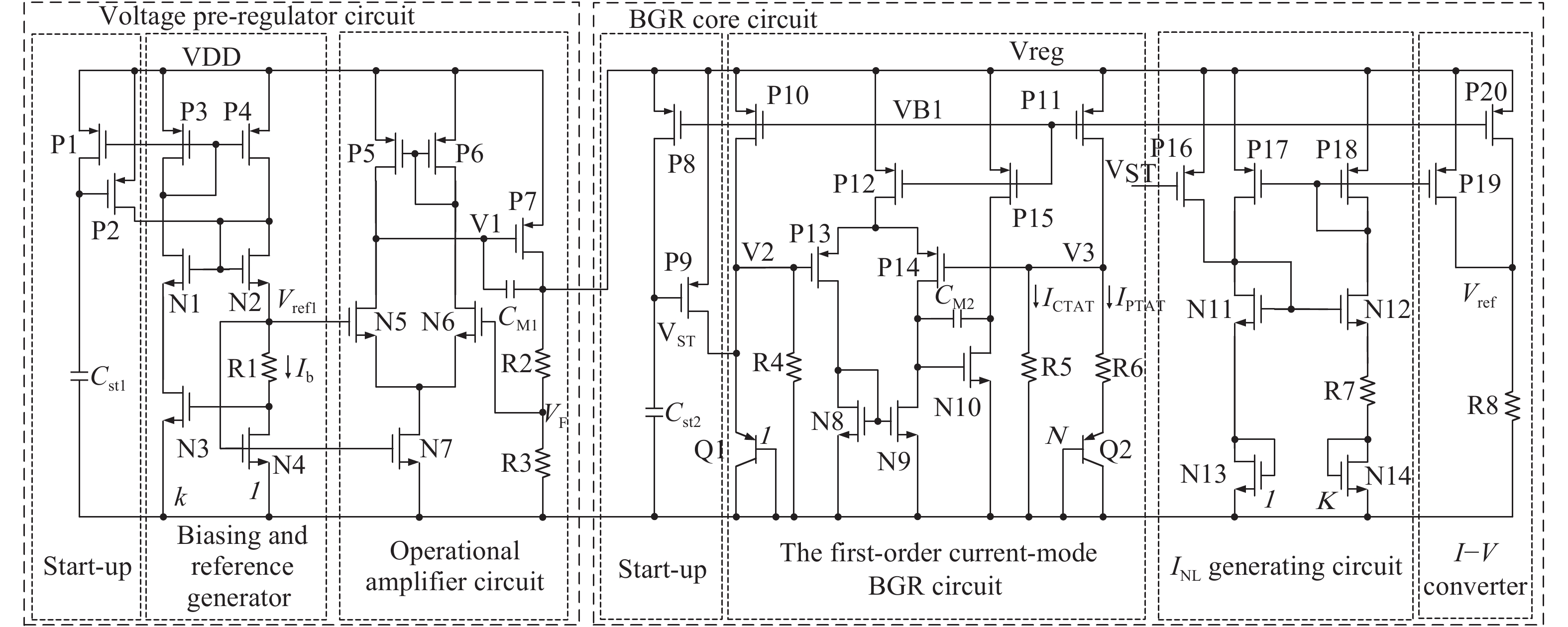

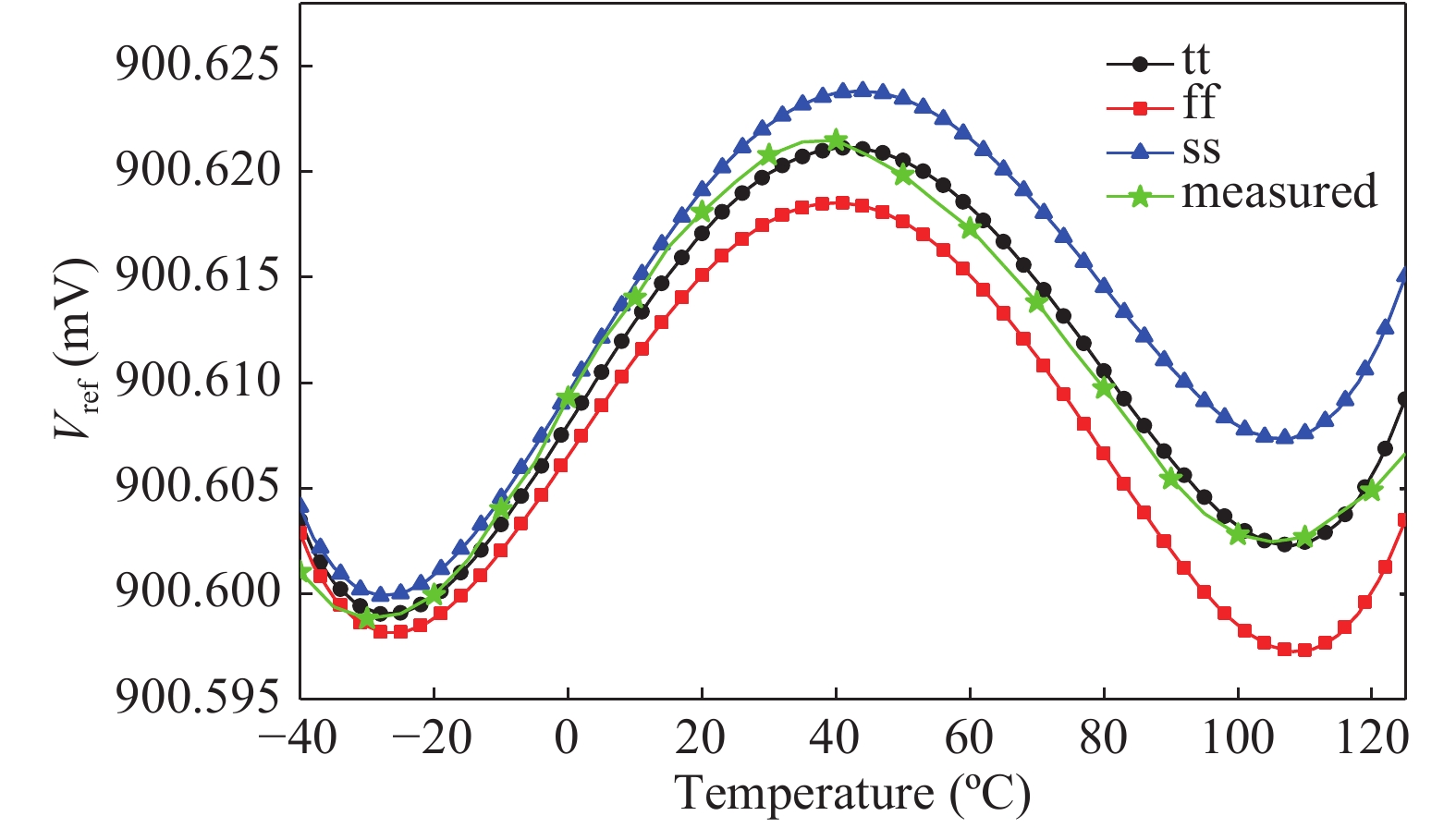

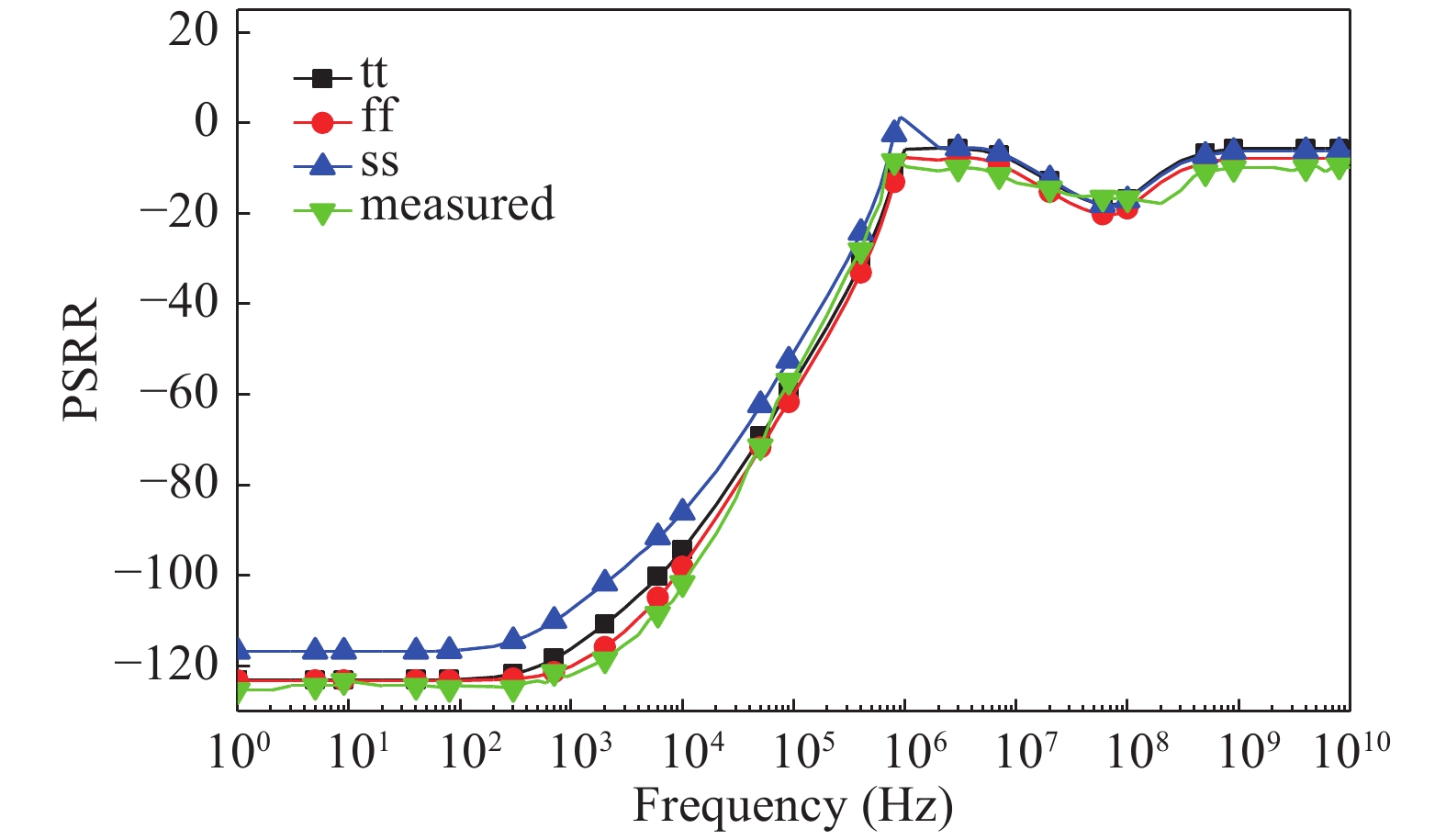

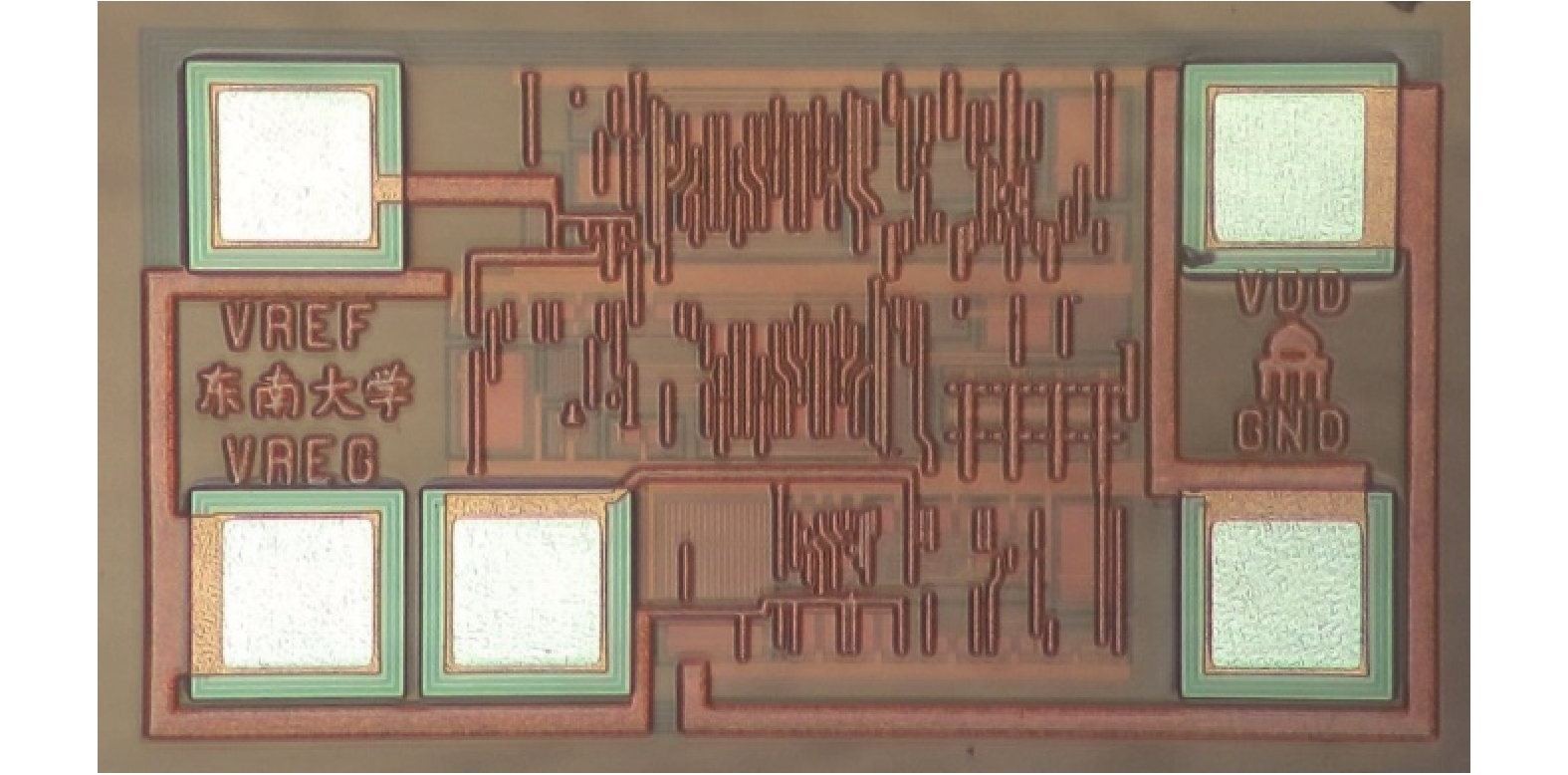

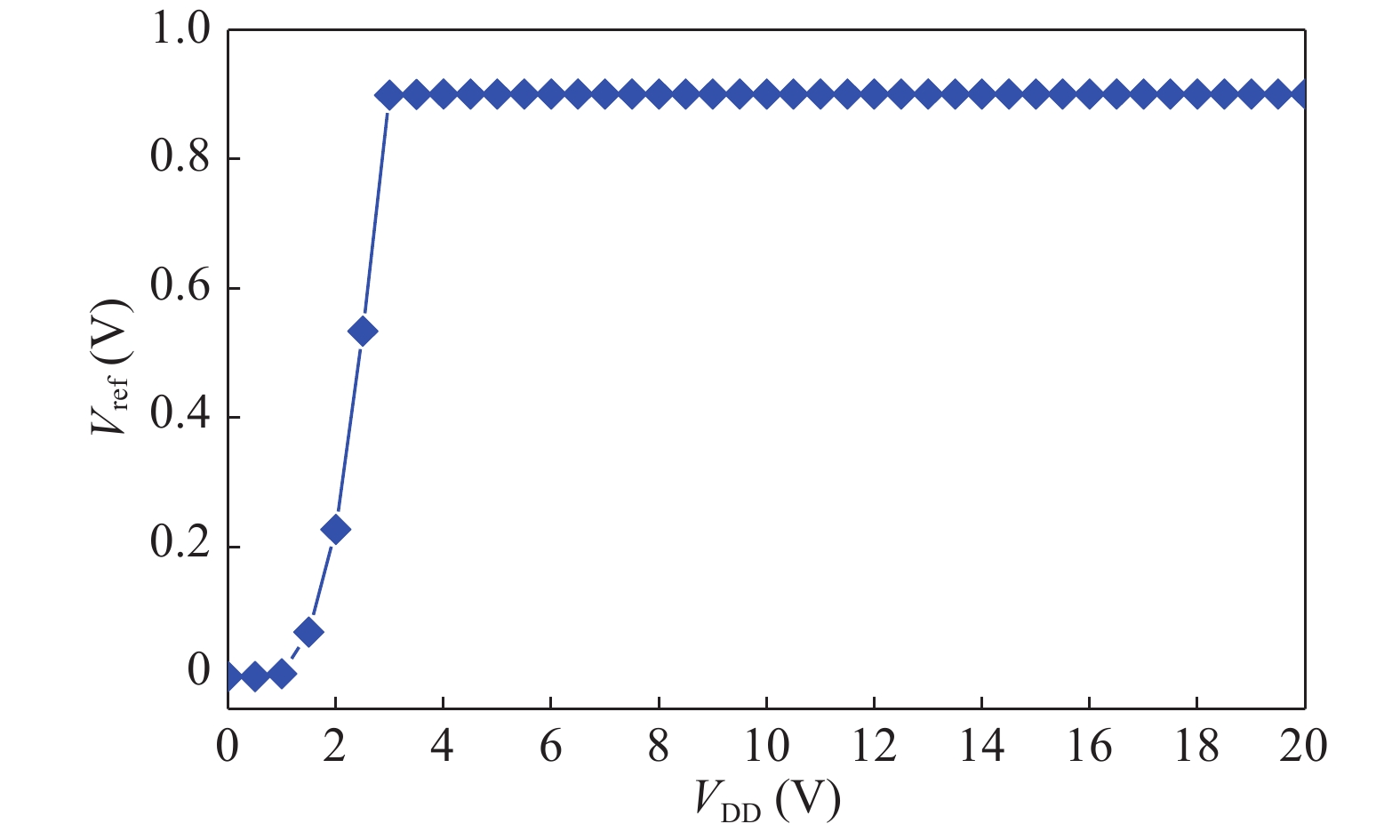

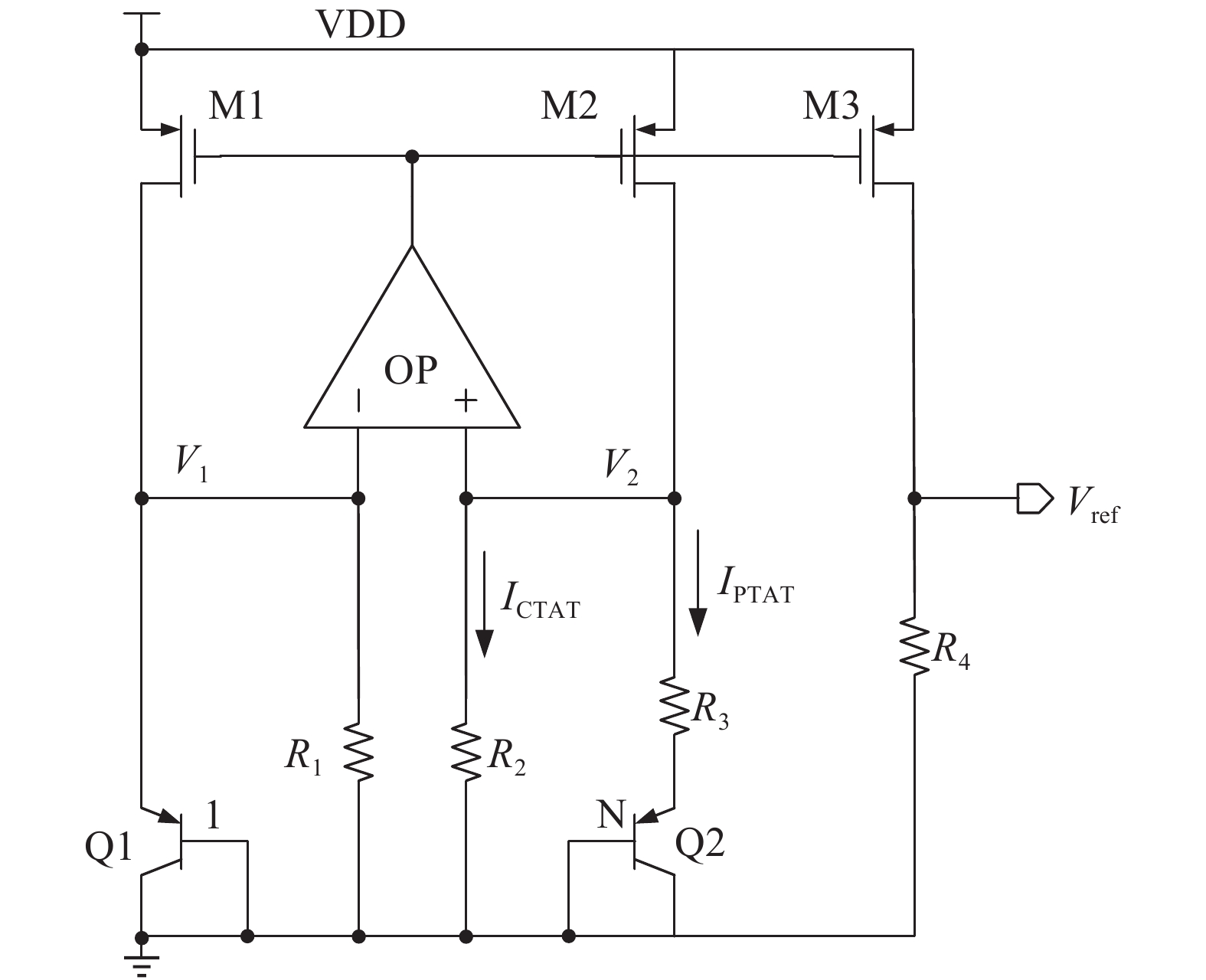

A high-order curvature-compensated CMOS bandgap reference (BGR) topology with a low temperature coefficient (TC) over a wide temperature range and a high power supply reject ratio (PSRR) is presented. High-order correction is realized by incorporating a nonlinear current INL, which is generated by ∆VGS across resistor into current generated by a conventional first-order current-mode BGR circuit. In order to achieve a high PSRR over a broad frequency range, a voltage pre-regulating technique is applied. The circuit was implemented in CSMC 0.5 μm 600 V BCD process. The experimental results indicate that the proposed topology achieves TC of 0.19 ppm/°C over the temperature range of 165 °C (−40 to 125 °C), PSRR of −123 dB @ DC and −56 dB @ 100 kHz. In addition, it achieves a line regulation performance of 0.017%/V in the supply range of 2.8–20 V. -

References

[1] Song B S, Gray P R. A precision curvature-compensated CMOS bandgap reference. IEEE J Solid-State Circuits, 1983, 18(6): 634 doi: 10.1109/JSSC.1983.1052013[2] Vogler B, Rosberg M, Herzer R. A fully integrated 600 V SOI half bridge IGBT gate driver IC. 51th IWK, Internationales Wissenschaftliches Kolloquium, 2006[3] Rincon-Mora G, Allen P E. A 1.1-V current-mode and piecewise-linear curvature-corrected bandgap reference. IEEE J Solid-State Circuits, 1998, 33(10): 1551 doi: 10.1109/4.720402[4] Huang Y, Cheung C, Najafizadeh L. A multi-piecewise curvature-corrected technique for bandgap reference circuits. 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), 2013: 305[5] Wang R, Lu W, Zhao M, et al. A 2.1-ppm/°C current-mode CMOS bandgap reference with piecewise curvature compensation. 2017 IEEE International Symposium on Circuits and Systems (ISCAS), 2017: 1[6] Abbasi M U, Raikos G, Saraswat R, et al. A high PSRR, ultra-low power 1.2 V curvature corrected bandgap reference for wearable EEG application. 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), Grenoble, 2015: 1[7] Leung K N, Mok P K T, Leung C Y. A 2-V 23-μA 5.3-ppm/°C curvature-compensated CMOS bandgap voltage reference. IEEE J Solid-State Circuits, 2003, 38(3): 561 doi: 10.1109/JSSC.2002.808328[8] Zhou Z K, Yue S, Zhi H, et al. A 1.6-V 25-μA 5-ppm/°C curvature-compensated bandgap reference. IEEE Trans Circuits Syst I, 2012, 59(4): 677 doi: 10.1109/TCSI.2011.2169732[9] Tsividis Y P. Accurate analysis of temperature effects in IC–VBE characteristics with application to bandgap reference sources. IEEE J Solid-State Circuits, 1980, 15(6): 1076 doi: 10.1109/JSSC.1980.1051519[10] Palumbo G. Voltage references: from diodes to precision high-order bandgap circuits. IEEE Circuits Devices Mag, 2002, 18(5): 45 doi: 10.1109/MCD.2002.1035357[11] Ji Y, Jeon C, Son H, et al. 5.8 A 9.3 nW all-in-one bandgap voltage and current reference circuit. IEEE International Solid-State Circuits Conference (ISSCC), 2017: 100[12] Osaki Y, Hirose T, Kuroki N et al. 1.2-V supply, 100-nW, 1.09-V bandgap and 0.7-V supply, 52.5-nW, 0.55-V subbandgap reference circuits for nanowatt CMOLSIs S. IEEE J Solid-State Circuits, 2013, 48(6): 1530 doi: 10.1109/JSSC.2013.2252523[13] Wang B, Law M K, Bermak A. A precision CMOS voltage reference exploiting silicon bandgap narrowing effect. IEEE Trans Electron Devices, 2015, 62(7): 2128 doi: 10.1109/TED.2015.2434495[14] Lin C, Chen H, Xu W, et al. A novel high-precision bandgap reference with differential common-gate structure. IEEE 9th International Conference on Anti-counterfeiting, Security, and Identification (ASID), Xiamen, 2015: 47[15] Duan Q, Roh J. A 1.2-V 4.2-ppm/°C high-order curvature-compensated CMOS bandgap reference. IEEE Trans Circuits Syst I, 2015, 62(3): 662 doi: 10.1109/TCSI.2014.2374832[16] Chen H M, Lee C C, Jheng S H, et al. A sub-1 ppm/°C precision bandgap reference with adjusted-temperature-curvature compensation. IEEE Trans Circuits Syst I, 2017, 64(6): 1308 doi: 10.1109/TCSI.2017.2658186[17] Ma B, Yu F. A novel 1.2-V 4.5-ppm/°C curvature-compensated CMOS bandgap reference. IEEE Trans Circuits Syst I, 2014, 61(4): 1026 doi: 10.1109/TCSI.2013.2286032[18] Ming X, Ma Y Q, Zhou Z K, et al. A high-precision compensated CMOS bandgap voltage reference without resistors. IEEE Trans Circuits Syst II, 2010, 57(10): 767 doi: 10.1109/TCSII.2010.2067770[19] Lv J, Wei L, Ang S S. A new curvature-compensated, high-PSRR CMOS bandgap reference. Analog Integrated Circuits and Signal Processing, 2015, 82(3): 675 doi: 10.1007/s10470-015-0494-2 -

Proportional views

DownLoad:

DownLoad: