| Citation: |

Xiaotian Sun, Qiuhui Li, Ruge Quhe, Yangyang Wang, Jing Lu. Super high maximum on-state currents in 2D transistors[J]. Journal of Semiconductors, 2022, 43(12): 120401. doi: 10.1088/1674-4926/43/12/120401

****

X T Sun, Q H Li, R G Quhe, Y Y Wang, J Lu. Super high maximum on-state currents in 2D transistors[J]. J. Semicond, 2022, 43(12): 120401. doi: 10.1088/1674-4926/43/12/120401

|

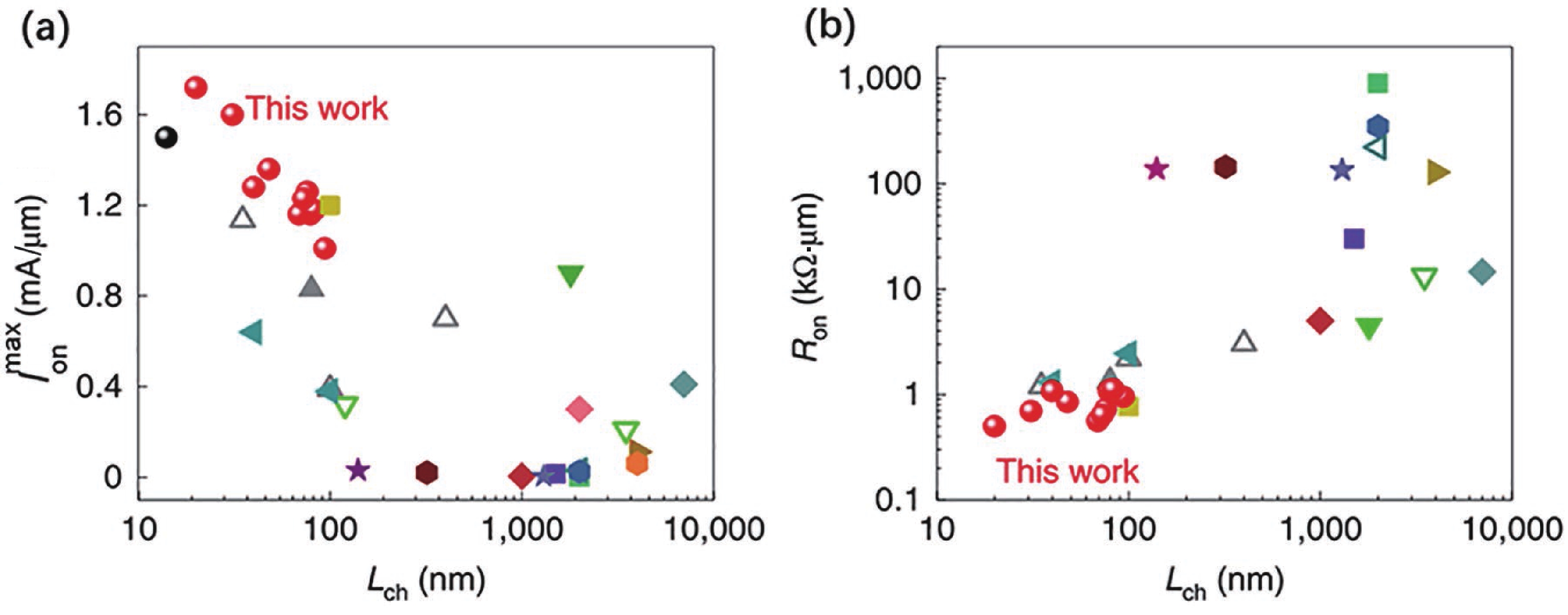

Super high maximum on-state currents in 2D transistors

DOI: 10.1088/1674-4926/43/12/120401

More Information

-

References

[1] Liu Y, Duan X D, Shin H J, et al. Promises and prospects of two-dimensional transistors. Nature, 2021, 591, 43 doi: 10.1038/s41586-021-03339-z[2] Li M Y, Su S K, Wong H S P, et al. How 2D semiconductors could extend Moore's law. Nature, 2019, 567, 169 doi: 10.1038/d41586-019-00793-8[3] Wang Y Y, Liu S Q, Li Q H, et al. Schottky barrier heights in two-dimensional field-effect transistors: From theory to experiment. Rep Prog Phys, 2021, 84, 056501 doi: 10.1088/1361-6633/abf1d4[4] Quhe R G, Xu L, Liu S Q, et al. Sub-10 nm two-dimensional transistors: Theory and experiment. Phys Rep, 2021, 938, 1 doi: 10.1016/j.physrep.2021.07.006[5] Shen P C, Su C, Lin Y X, et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature, 2021, 593, 211 doi: 10.1038/s41586-021-03472-9[6] Liu L, Li T T, Ma L, et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature, 2022, 605, 69 doi: 10.1038/s41586-022-04523-5[7] Ni Z Y, Ye M, Ma J H, et al. Performance upper limit of sub-10 nm monolayer MoS2 transistors. Adv Electron Mater, 2016, 2, 1600191 doi: 10.1002/aelm.201600191[8] Wu R X, Tao Q Y, Li J, et al. Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. Nat Electron, 2022, 5, 497 doi: 10.1038/s41928-022-00800-3[9] Sun X T, Xu L, Zhang Y, et al. Performance limit of monolayer WSe2 transistors; significantly outperform their MoS2 counterpart. ACS Appl Mater Interfaces, 2020, 12, 20633 doi: 10.1021/acsami.0c01750[10] Qiu C G, Zhang Z Y, Xiao M M, et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science, 2017, 355, 271 doi: 10.1126/science.aaj1628[11] The International Technology Roadmap for Semiconductors (ITRS). Online available, https://irds.ieee.org/editions/2021[12] The International Roadmap for Devices and Systems (IRDS). Online available: https://ieeexplore.ieee.org/abstract/document/7046976[13] Natarajan S, Agostinelli M, Akbar S, et al. A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. 2014 IEEE International Electron Devices Meeting, 2014, 3.7.1 doi: 10.1109/IEDM.2014.7046976[14] Zhang Y C, Yu J, Zhu R X, et al. A single-crystalline native dielectric for two-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm. Nat Electron, 2022, 5, 643 doi: 10.1038/s41928-022-00824-9 -

Proportional views

DownLoad:

DownLoad: