| Citation: |

Yang Shen, He Tian, Tianling Ren. Simulation of MoS2 stacked nanosheet field effect transistor[J]. Journal of Semiconductors, 2022, 43(8): 082002. doi: 10.1088/1674-4926/43/8/082002

****

Y Shen, H Tian, T L Ren. Simulation of MoS2 stacked nanosheet field effect transistor[J]. J. Semicond, 2022, 43(8): 082002. doi: 10.1088/1674-4926/43/8/082002

|

Simulation of MoS2 stacked nanosheet field effect transistor

DOI: 10.1088/1674-4926/43/8/082002

More Information

-

Abstract

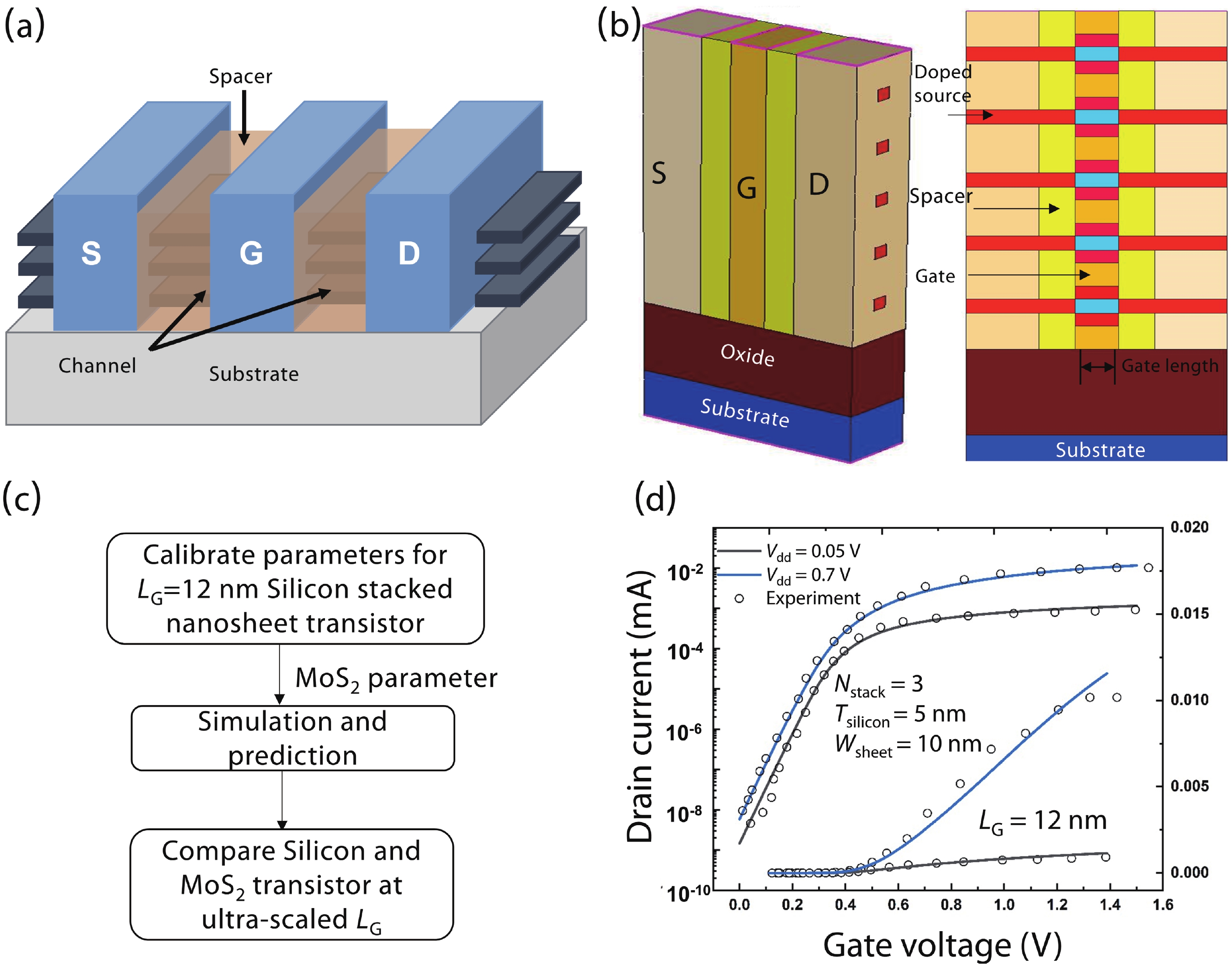

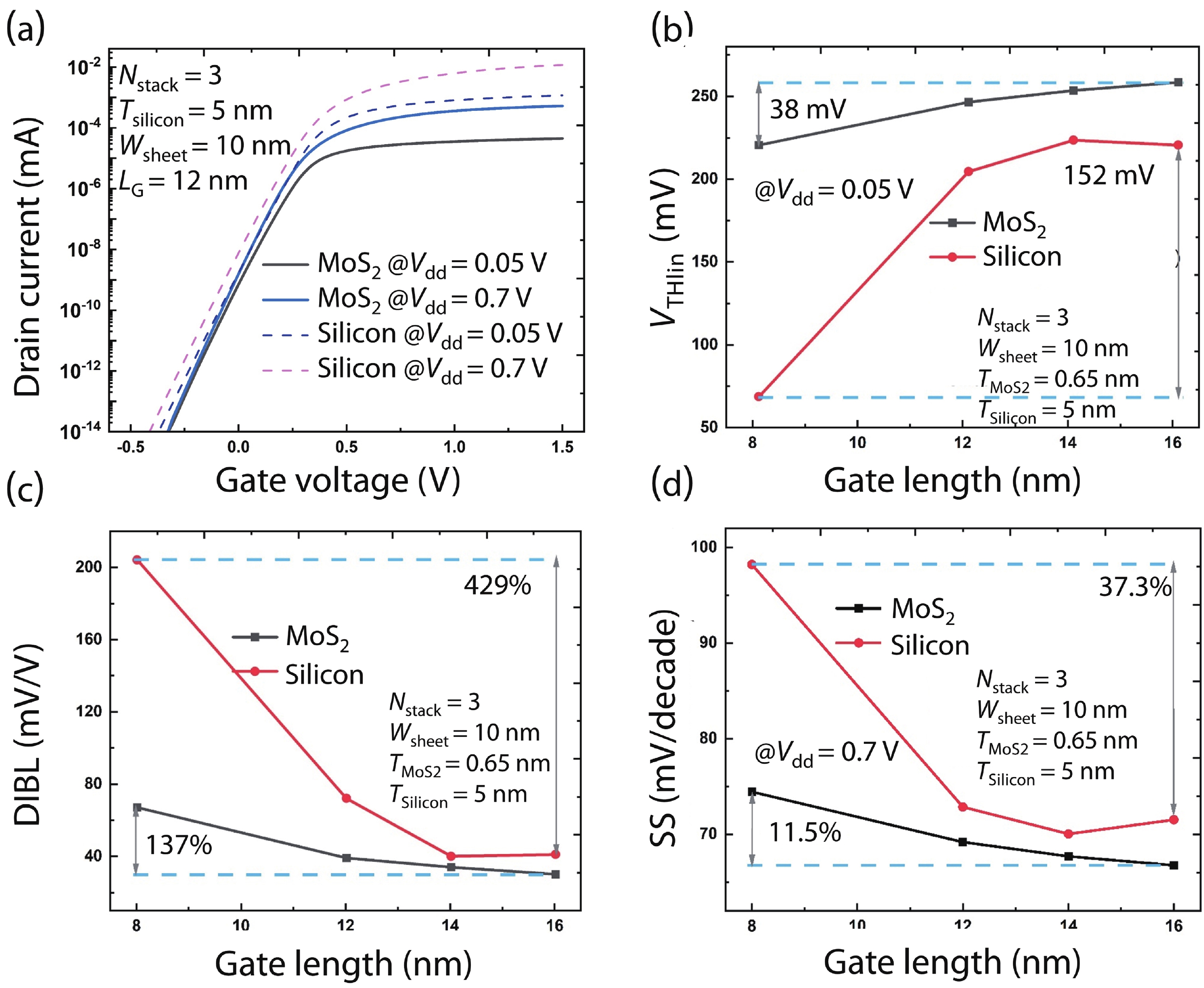

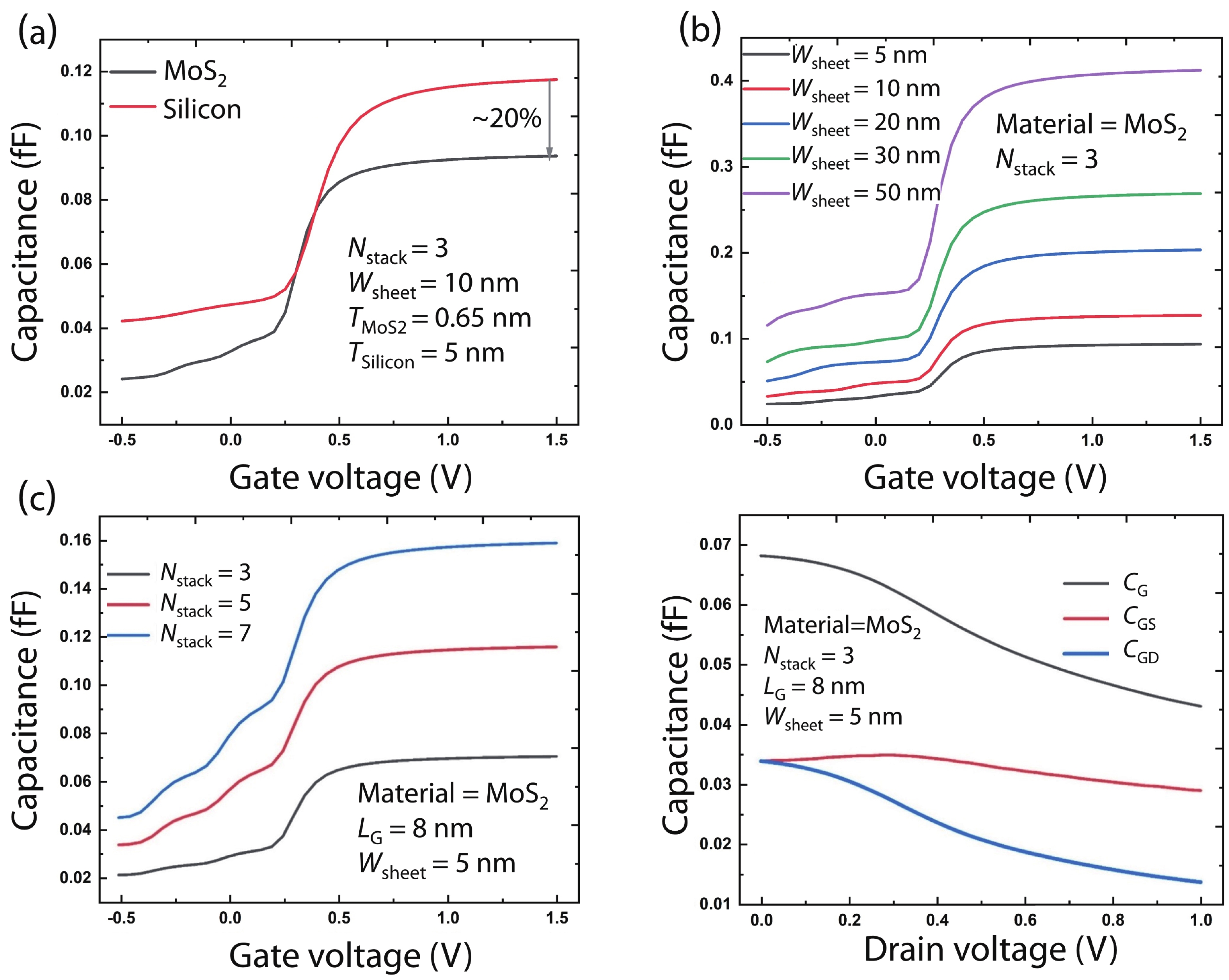

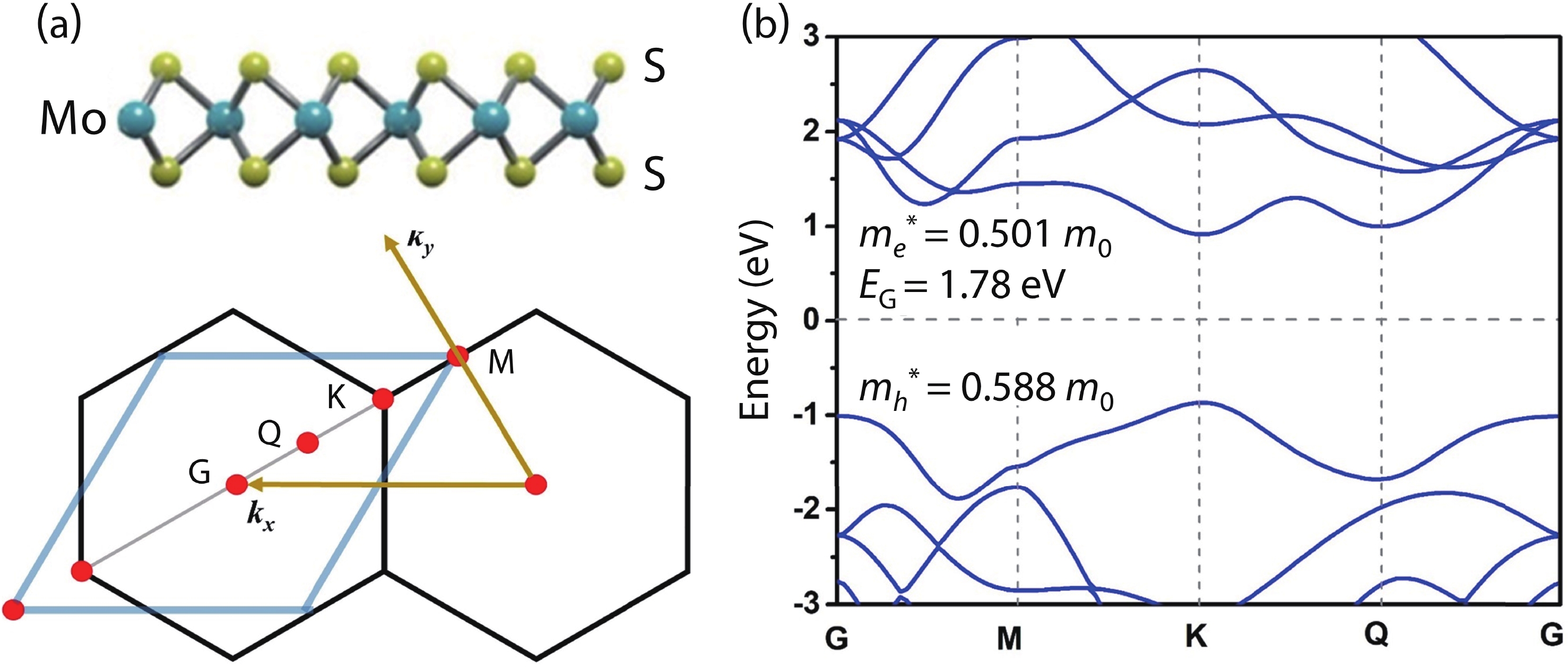

Transition metal dichalcogenides are nowadays appealing to researchers for their excellent electronic properties. Vertical stacked nanosheet FET (NSFET) based on MoS2 are proposed and studied by Poisson equation solver coupled with semi-classical quantum correction model implemented in Sentaurus workbench. It is found that, the 2D stacked NSFET can largely suppress short channel effects with improved subthreshold swing and drain induced barrier lowering, due to the excellent electrostatics of 2D MoS2. In addition, small-signal capacitance is extracted and analyzed. The MoS2 based NSFET shows great potential to enable next generation electronics.-

Keywords:

- MoS2,

- stacked nanosheet GAA,

- TCAD simulation

-

References

[1] Cui J, Chen L, Kang C L, et al. A high-linearity InGaP/GaAs HBT power amplifier for IEEE 802.11a/N. J Semicond, 2013, 34, 065001 doi: 10.1088/1674-4926/34/6/065001[2] Loubet N, Hook T, Montanini P, et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. 2017 Symposium on VLSI Technology, 2017, T230[3] Bansal A K, Jain I, Hook T B, et al. Series resistance reduction in stacked nanowire FETs for 7-nm CMOS technology. IEEE J Electron Devices Soc, 2016, 4, 266 doi: 10.1109/JEDS.2016.2592183[4] Radisavljevic B, Radenovic A, Brivio J, et al. Single-layer MoS2 transistors. Nat Nanotechnol, 2011, 6, 147 doi: 10.1038/nnano.2010.279[5] Sebastian A, Pendurthi R, Choudhury T H, et al. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat Commun, 2021, 12, 693 doi: 10.1038/s41467-020-20732-w[6] Das S, Sebastian A, Pop E, et al. Transistors based on two-dimensional materials for future integrated circuits. Nat Electron, 2021, 4, 786 doi: 10.1038/s41928-021-00670-1[7] Wu F, Tian H, Shen Y, et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature, 2022, 603, 259 doi: 10.1038/s41586-021-04323-3[8] Wang S, Liu X, Zhou P. The road for 2D semiconductors in the silicon age. Adv Mater, 2021, 2021, e2106886 doi: 10.1002/adma.202106886[9] Wu F, Ren J, Yang Y, et al. A 10 nm short channel MoS2 transistor without the resolution requirement of photolithography. Adv Electron Mater, 2021, 7, 2170057 doi: 10.1002/aelm.202170057[10] Xie L, Liao M, Wang S, et al. Graphene-contacted ultrashort channel monolayer MoS2 transistors. Adv Mater, 2017, 29, 1702522 doi: 10.1002/adma.201702522[11] Allain A, Kang J H, Banerjee K, et al. Electrical contacts to two-dimensional semiconductors. Nat Mater, 2015, 14, 1195 doi: 10.1038/nmat4452[12] Shen P C, Su C, Lin Y X, et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature, 2021, 593, 211 doi: 10.1038/s41586-021-03472-9[13] Jariwala D, Sangwan V K, Late D J, et al. Band-like transport in high mobility unencapsulated single-layer MoS2 transistors. Appl Phys Lett, 2013, 102, 173107 doi: 10.1063/1.4803920[14] Chen H W, Li J Y, Chen X Z, et al. Dramatic switching behavior in suspended MoS2 field-effect transistors. Semicond Sci Technol, 2018, 33, 024001 doi: 10.1088/1361-6641/aaa222[15] Pon A, Carmel S, Bhattacharyya A, et al. Simulation of 2D layered material ballistic FETs using a hybrid methodology. 2019 IEEE International Conference on Electron Devices and Solid-State Circuits, 2019, 1 doi: 10.1109/EDSSC.2019.8754400[16] Sudarsanan A, Venkateswarlu S, Nayak K. Superior work function variability performance of horizontally stacked nanosheet FETs for sub-7-nm technology and beyond. 2020 4th IEEE Electron Devices Technology & Manufacturing Conference, 2020, 1 doi: 10.1109/EDTM47692.2020.9117974[17] Valasa S, Tayal S, Thoutam L R. Optimization of design space for vertically stacked junctionless nanosheet FET for analog/RF applications. Silicon, 2022, 1[18] Mohapatra E, Dash T P, Jena J, et al. Design study of gate-all-around vertically stacked nanosheet FETs for sub-7nm nodes. SN Appl Sci, 2021, 3, 540 doi: 10.1007/s42452-021-04539-y[19] Zebrev G I, Tselykovskiy A A, Batmanova D K, et al. Small-signal capacitance and current parameter modeling in large-scale high-frequency graphene field-effect transistors. IEEE Trans Electron Devices, 2013, 60, 1799 doi: 10.1109/TED.2013.2257793[20] Fang N, Nagashio K. Quantum-mechanical effect in atomically thin MoS2 FET. 2D Mater, 2019, 7, 014001 doi: 10.1088/2053-1583/ab42c0 -

Proportional views

DownLoad:

DownLoad: