| Citation: |

Weiyan Zhang, Tao Yu, Zhifeng Zhu, Binghan Li. Temperature-insensitive reading of a flash memory cell[J]. Journal of Semiconductors, 2023, 44(4): 044102. doi: 10.1088/1674-4926/44/4/044102

****

W Y Zhang, T Yu, Z F Zhu, B H Li. Temperature-insensitive reading of a flash memory cell[J]. J. Semicond, 2023, 44(4): 044102. doi: 10.1088/1674-4926/44/4/044102

|

Temperature-insensitive reading of a flash memory cell

DOI: 10.1088/1674-4926/44/4/044102

More Information

-

Abstract

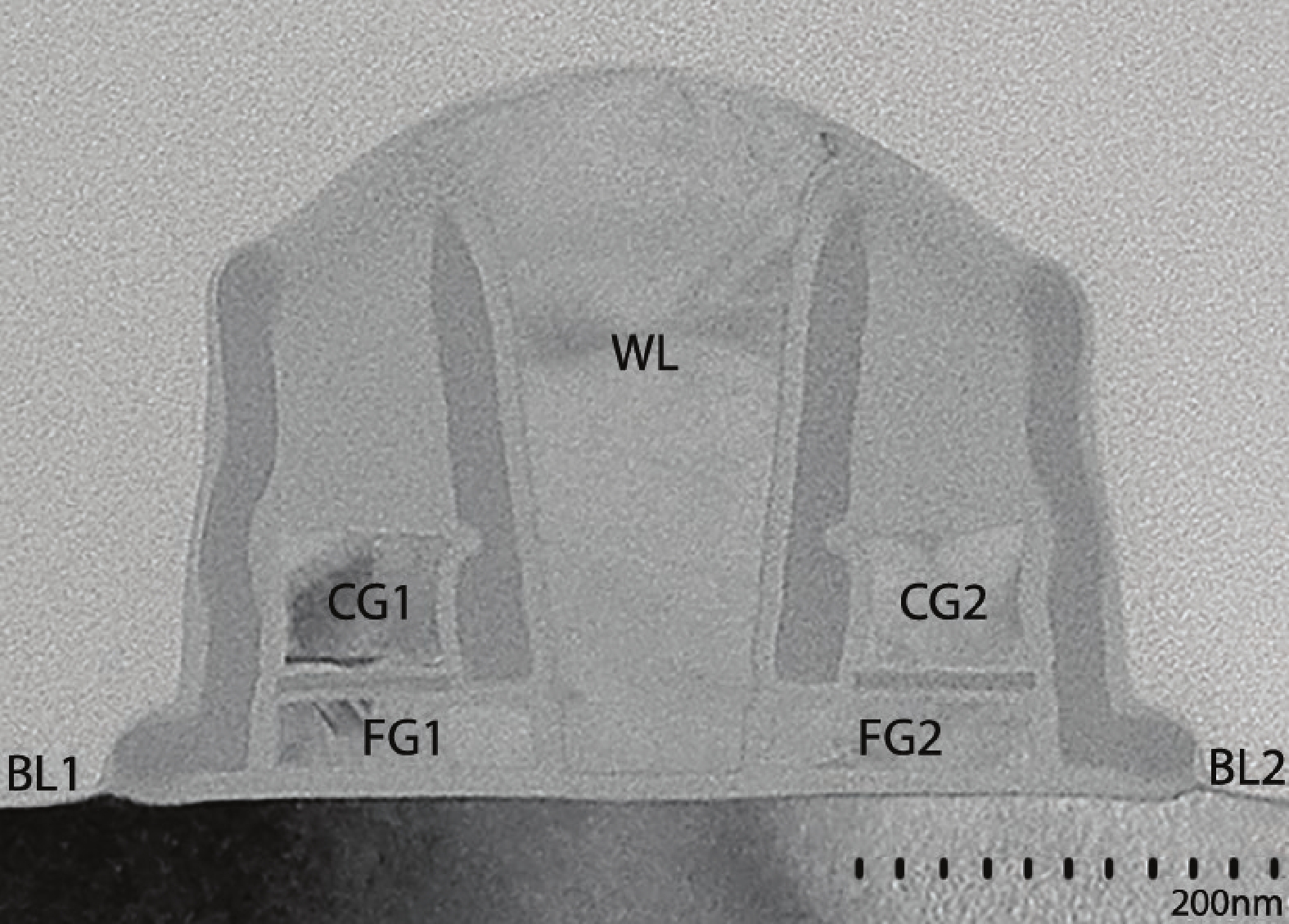

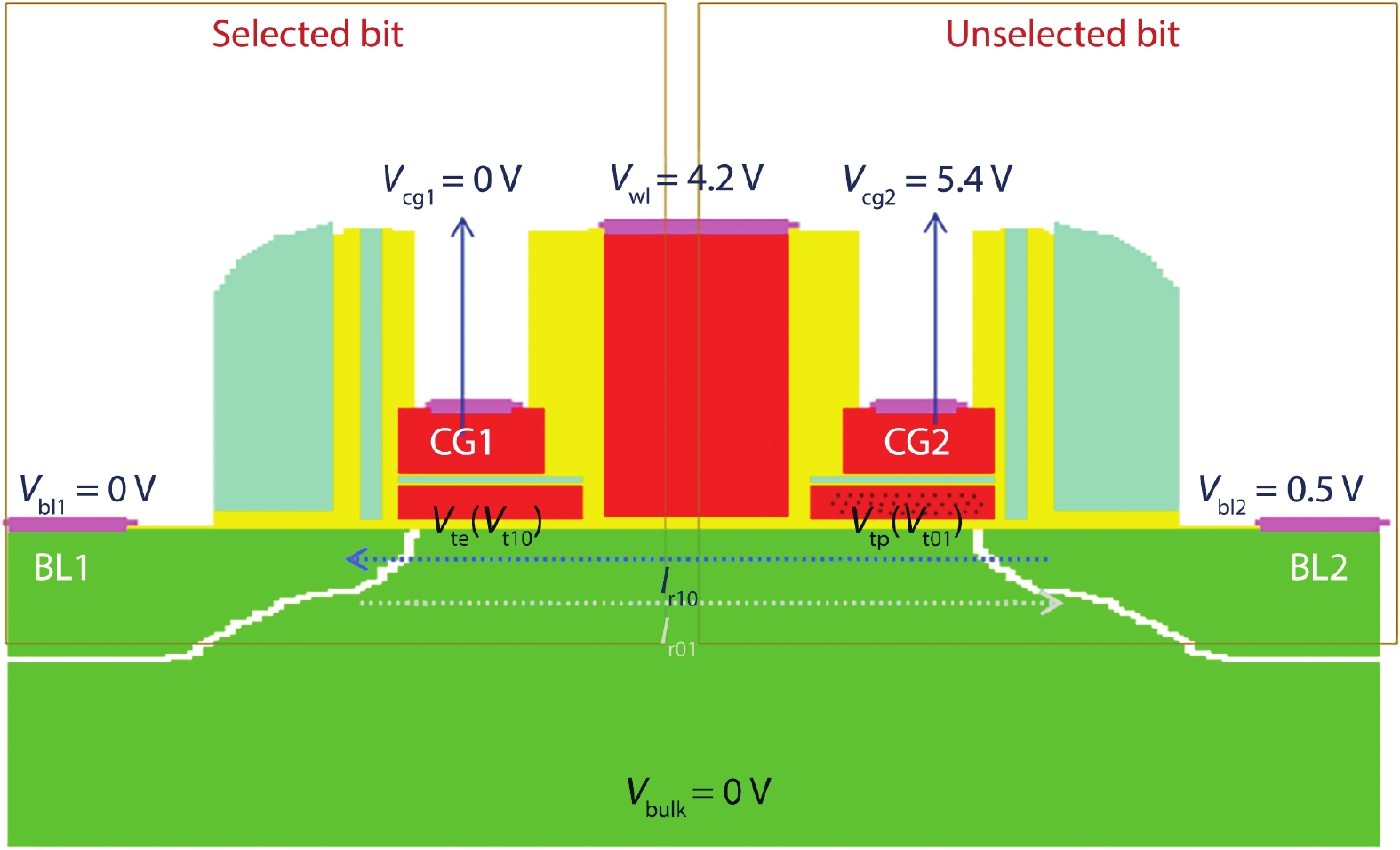

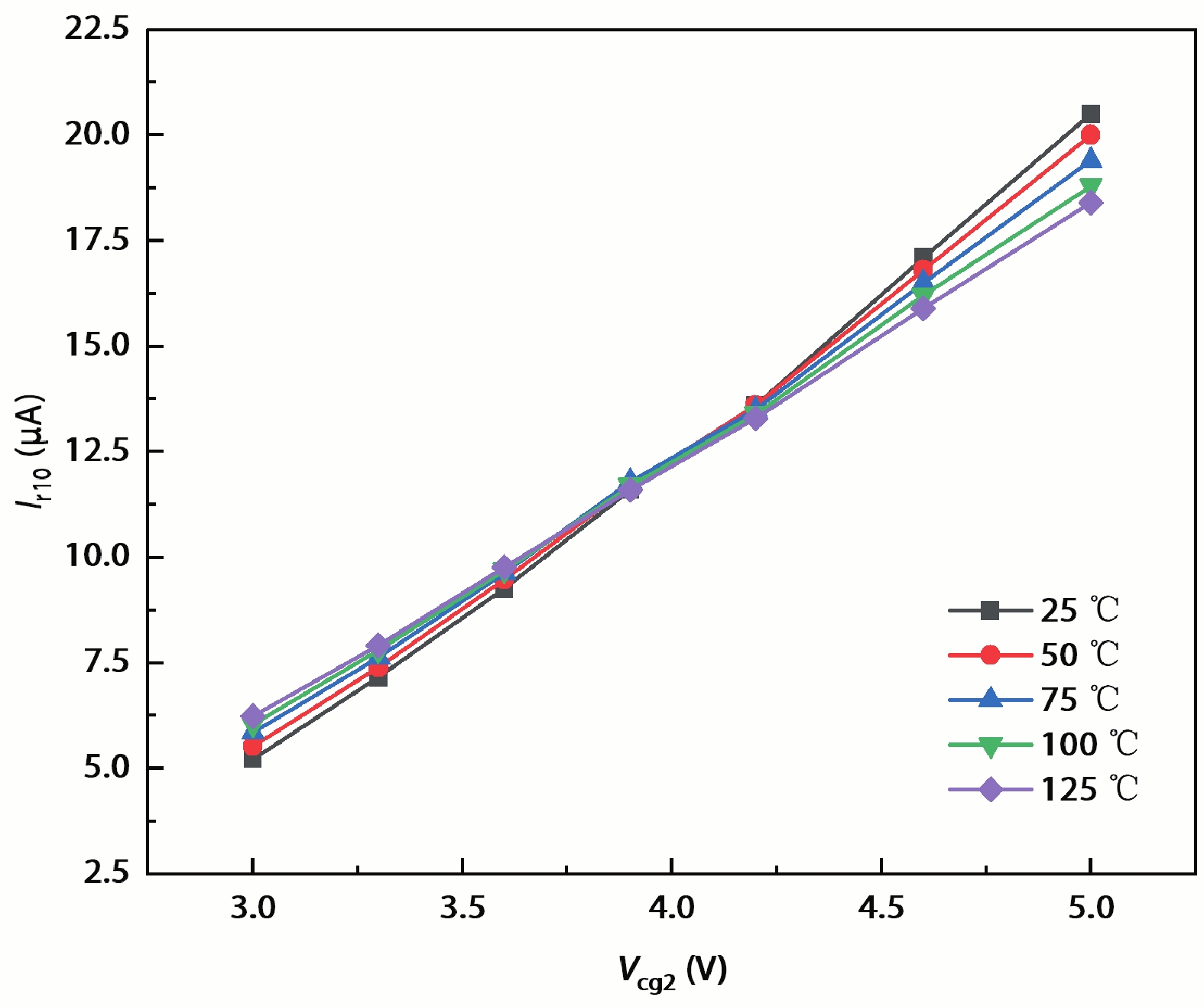

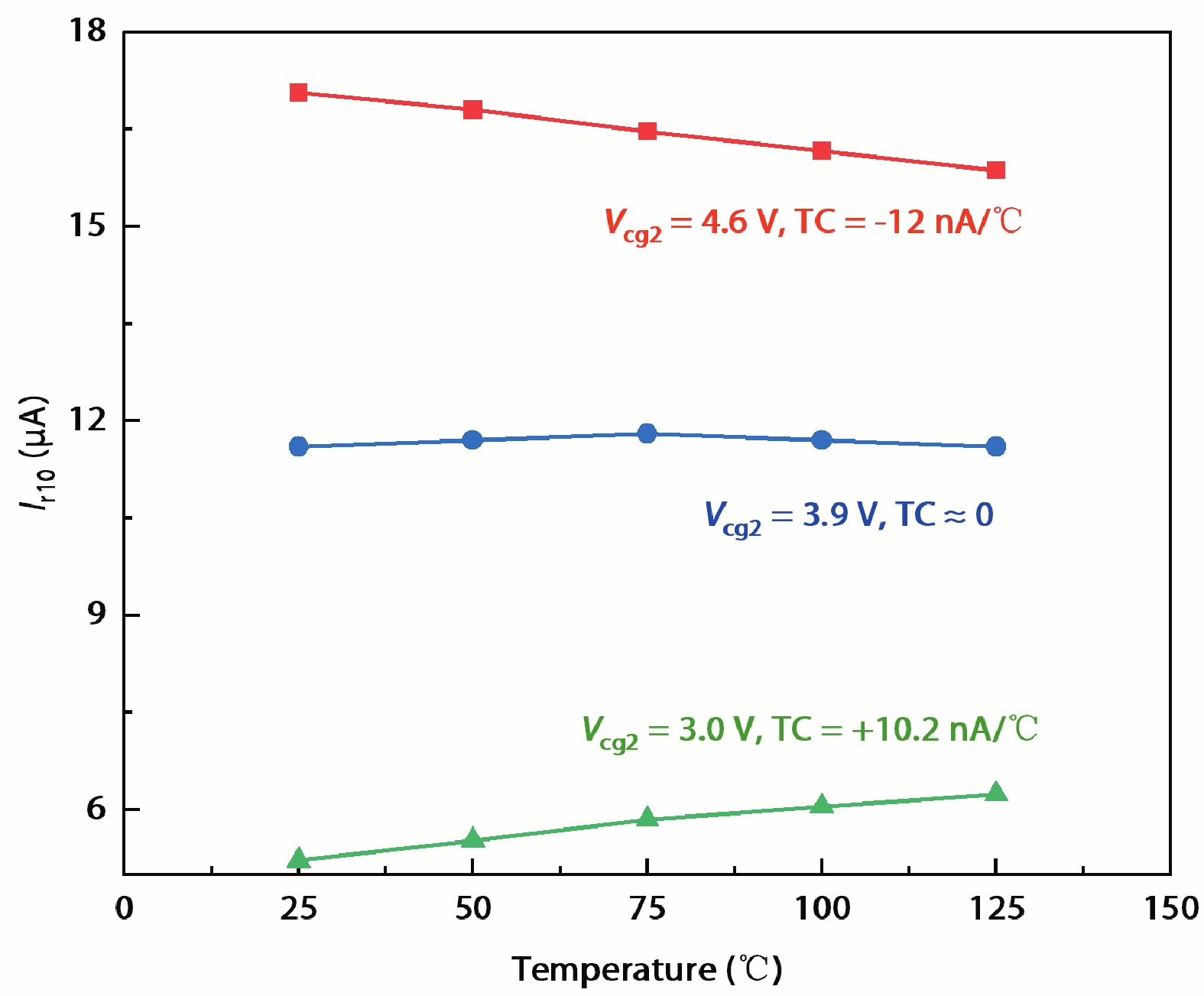

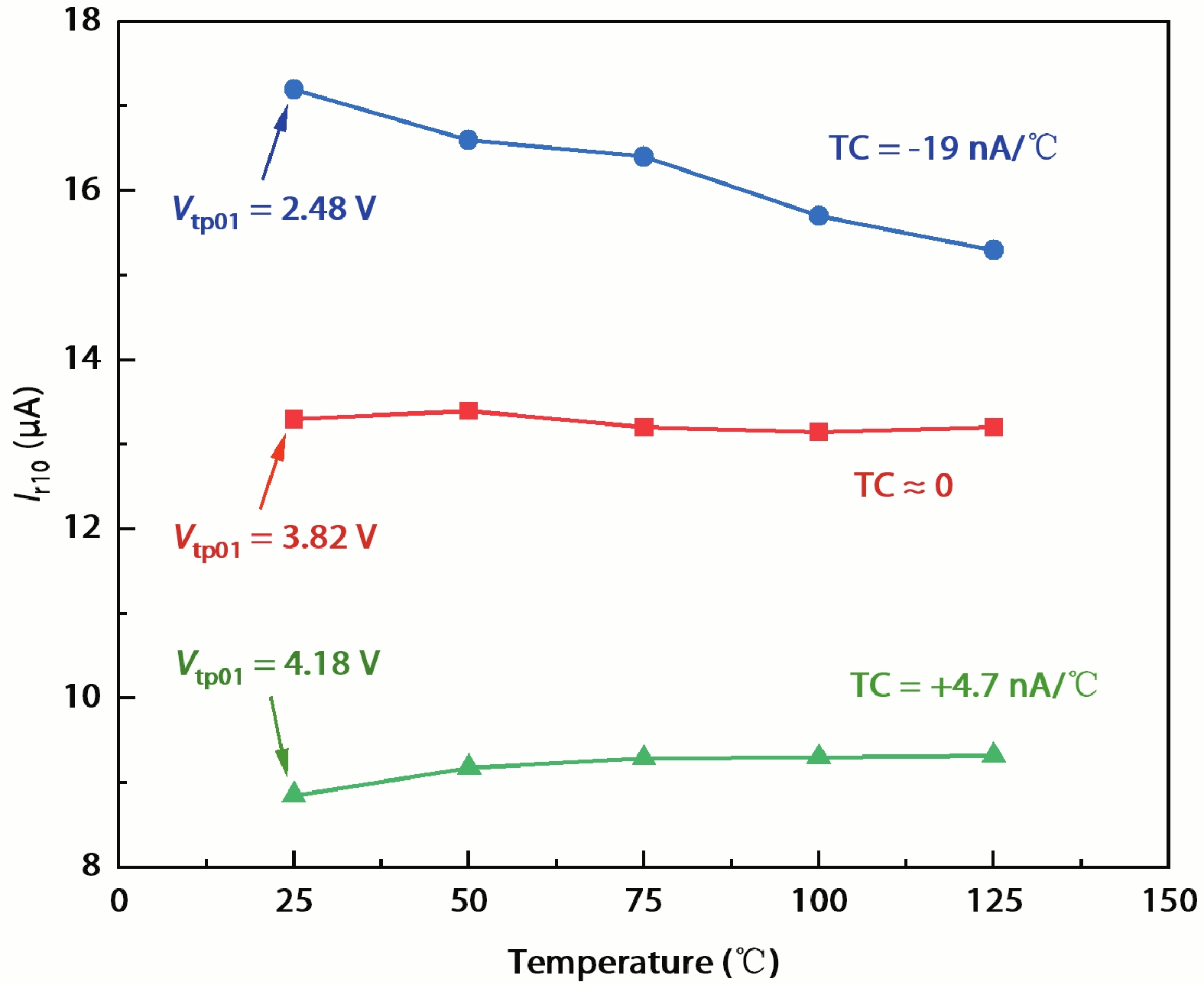

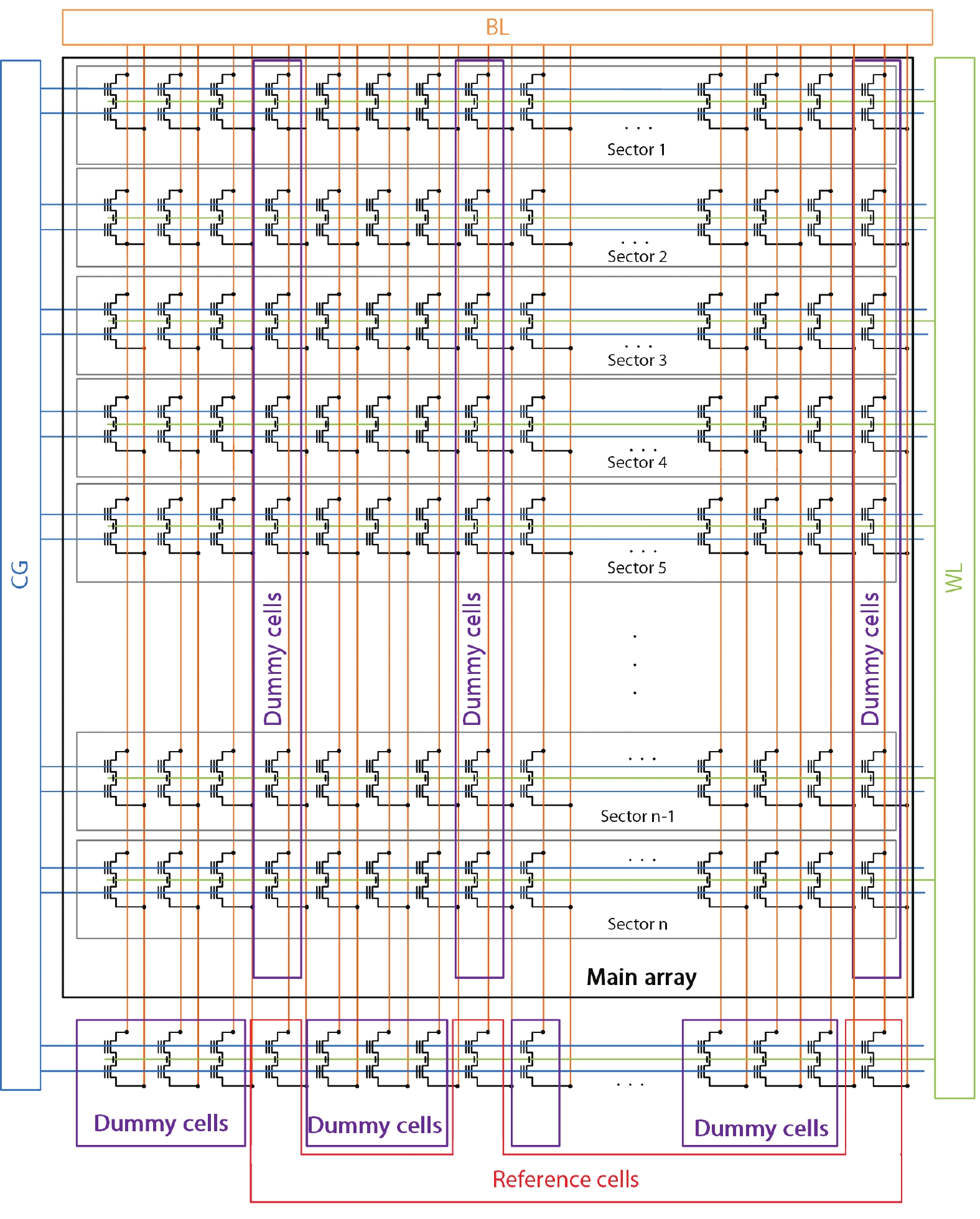

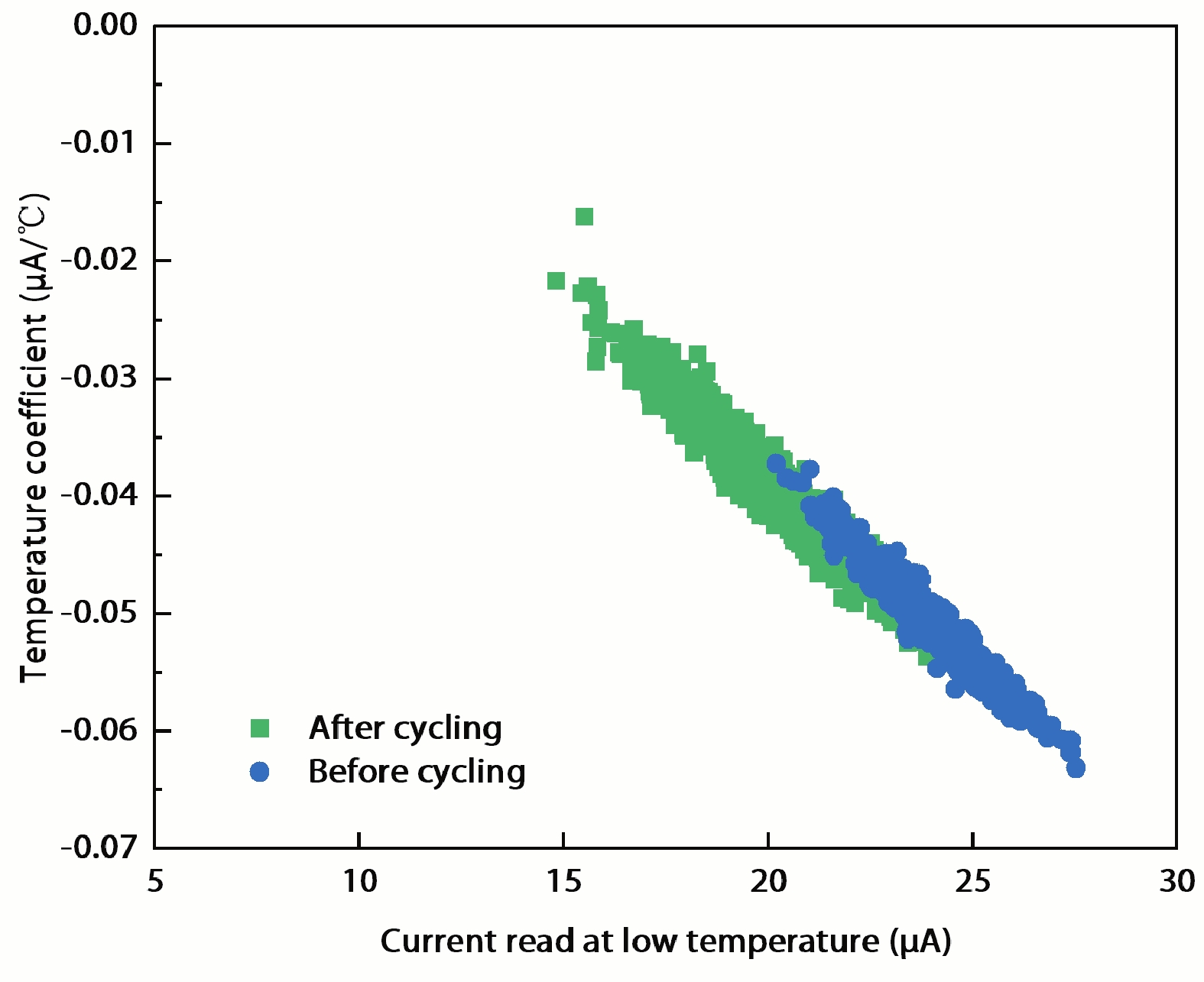

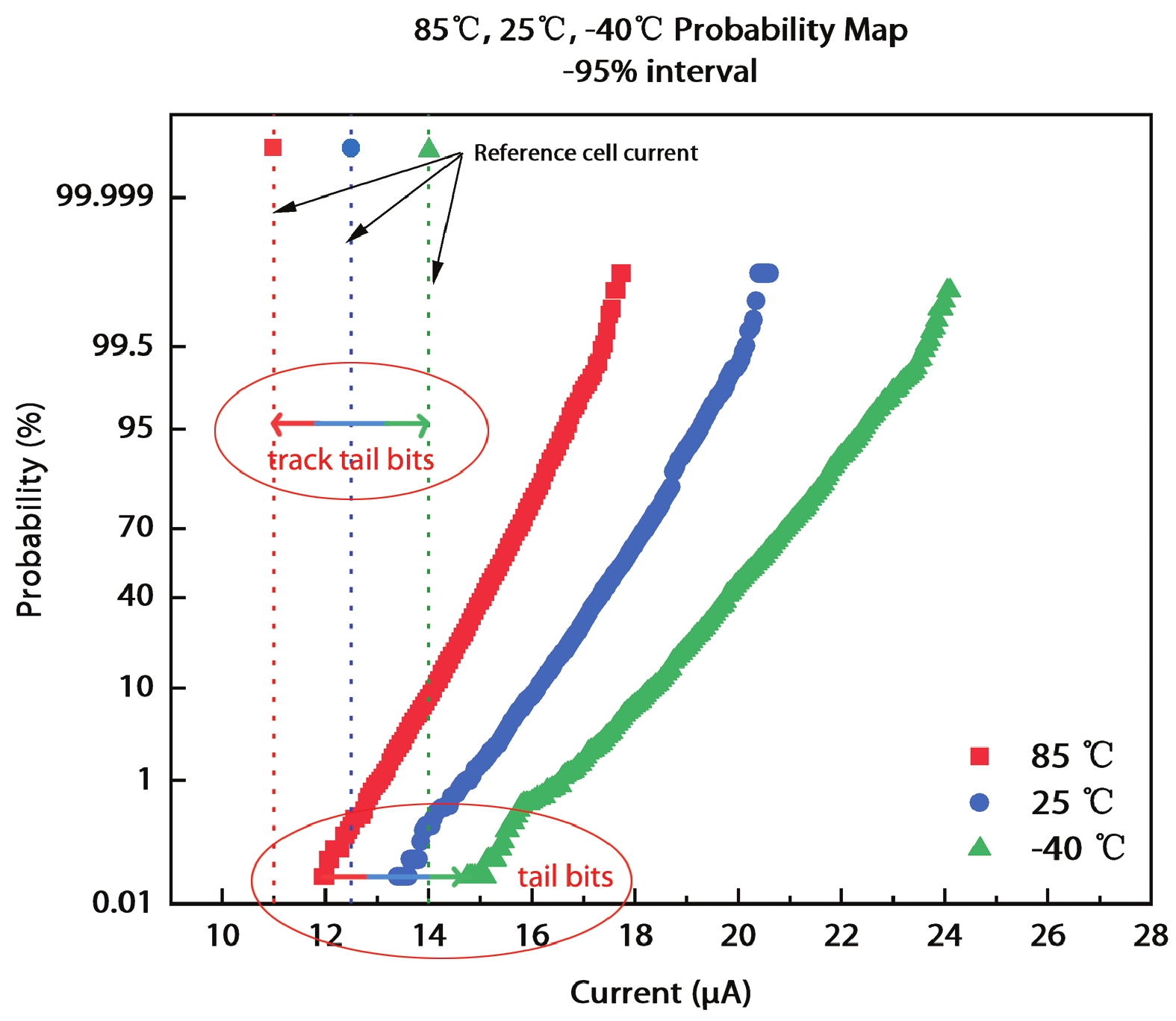

The temperature characteristics of the read current of the NOR embedded flash memory with a 1.5T-per-cell structure are theoretically analyzed and experimentally verified. We verify that for a cell programmed with a “10” state, the read current is either increasing, decreasing, or invariable with the temperature, essentially depending on the reading overdrive voltage of the selected bitcell, or its programming strength. By precisely controlling the programming strength and thus manipulating its temperature coefficient, we propose a new setting method for the reference cells that programs each of reference cells to a charge state with a temperature coefficient closely tracking tail data cells, thereby solving the current coefficient mismatch and improving the read window.-

Keywords:

- flash memory,

- temperature coefficient,

- reference cell,

- flash array

-

References

[1] Han S T, Zhou Y, Roy V A. Towards the development of flexible non-volatile memories. Adv Mater, 2013, 25(38), 5425 doi: 10.1002/adma.201301361[2] Chen F, Chen B, Lin H, et al. Temperature impacts on endurance and read disturbs in charge-trap 3D NAND flash memories. Micromachines, 2021, 12(10), 1152 doi: 10.3390/mi12101152[3] Resnati D, Goda A, Nicosia G, et al. Temperature effects in NAND flash memories: A comparison between 2-D and 3-D arrays. IEEE Electron Device Lett, 2017, 38(4), 461 doi: 10.1109/LED.2017.2675160[4] Zambelli C, Koebernik G, Ullmann R, et al. Modeling erratic bits temperature dependence for Monte Carlo simulation of flash arrays. IEEE Electron Device Lett, 2013, 34(3), 390 doi: 10.1109/LED.2012.2237541[5] Dilello A, Andryzcik S, Kelly B M, et al. Temperature compensation of floating-gate transistors in field-programmable analog arrays. 2017 IEEE International Symposium on Circuits and Systems (ISCAS), 2017, 1 doi: 10.1109/ISCAS.2017.8050290[6] Shin H, Oh M, Choi J, et al. A 28nm embedded flash memory with 100MHz read operation and 7.42Mb/mm2 at 0.85V featuring for automotive application. 2021 Symposium on VLSI Circuits, 2021, 1 doi: 10.23919/VLSICircuits52068.2021.9492384[7] Dong Q, Wang Z, Lim J, et al. A 1Mb 28nm STT-MRAM with 2.8ns read access time at 1.2V VDD using single-cap offset-cancelled sense amplifier and in-situ self-write-termination. 2018 IEEE International Solid-State Circuits Conference (ISSCC), 2018, 480 doi: 10.1109/ISSCC.2018.8310393[8] Guo X, Bayat F M, Prezioso M, et al. Temperature-insensitive analog vector-by-matrix multiplier based on 55 nm NOR flash memory cells. 2017 IEEE Custom Integrated Circuits Conference (CICC), 2017, 1 doi: 10.1109/CICC.2017.7993628[9] Jin D H, Kwon J W, Seo M J, et al. A reference-free temperature-dependency-compensating readout scheme for phase-change memory using flash-ADC-configured sense amplifiers. IEEE J Solid-State Circuits, 2019, 54(6), 1812 doi: 10.1109/JSSC.2019.2899720[10] Fang L, Kong W, Gu J, et al. A novel symmetrical split-gate structure for 2-bit per cell flash memory. J Semicond, 2014, 35(7), 074008 doi: 10.1088/1674-4926/35/7/074008[11] Lue H T, Hsu T H, Wu M T, et al. Studies of the reverse read method and second-bit effect of 2-bit/cell nitride-trapping device by quasi-two-dimensional model. IEEE Trans Electron Devices, 2006, 53(1), 119 doi: 10.1109/TED.2005.860644[12] Tsividis Y, McAndrew C. Operation and modeling of the MOS transistor. 3rd ed. Oxford University Press, 2011[13] Dwivedi A K, Tyagi S, Islam A. Threshold voltage extraction and its reliance on device parameters @ 16-nm process technology. Proceedings of the 2015 Third International Conference on Computer, Communication, Control and Information Technology (C3IT), 2015, 1 doi: 10.1109/C3IT.2015.7060166[14] Tao C, Vega R A, Alptekin E, et al. Understanding short channel mobility degradation by accurate external resistance decomposition and intrinsic mobility extraction. J Appl Phys, 2015, 117(6), 64507 doi: 10.1063/1.4908111 -

Proportional views

DownLoad:

DownLoad:

Weiyan Zhang:got his BS degree from Hunan Normal University in 2020. He is currently a Master student at ShanghaiTech University. His research interests include the structure, process and reliability of the embedded flash memory

Weiyan Zhang:got his BS degree from Hunan Normal University in 2020. He is currently a Master student at ShanghaiTech University. His research interests include the structure, process and reliability of the embedded flash memory Tao Yu:got his Master’s Degree in Physics from Peking University in 2009. He Joined technology development department of Shanghai Huahong Grace Semiconductor Manufacturing Co. Ltd in 2010. His research focuses on the non-volatile memory, especially on the embedded flash

Tao Yu:got his Master’s Degree in Physics from Peking University in 2009. He Joined technology development department of Shanghai Huahong Grace Semiconductor Manufacturing Co. Ltd in 2010. His research focuses on the non-volatile memory, especially on the embedded flash Zhifeng Zhu:received the BSc degree from University of Electronic Science and Technology of China in 2014 and the PhD degree from National University of Singapore in 2019. He joined ShanghaiTech University as an assistant professor in 2020. His research focuses on the theoretical and numerical study of spintronic devices for the application of MRAM and neuromorphic computing

Zhifeng Zhu:received the BSc degree from University of Electronic Science and Technology of China in 2014 and the PhD degree from National University of Singapore in 2019. He joined ShanghaiTech University as an assistant professor in 2020. His research focuses on the theoretical and numerical study of spintronic devices for the application of MRAM and neuromorphic computing Binghan Li:got his PhD from the Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences in 2004. After then he joined Shanghai Huahong Grace Semiconductor Manufacturing Co. Ltd and mainly engaged in the R & D of non-volatile memory. He has published more than ten papers, and applied for more than 50 patents

Binghan Li:got his PhD from the Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences in 2004. After then he joined Shanghai Huahong Grace Semiconductor Manufacturing Co. Ltd and mainly engaged in the R & D of non-volatile memory. He has published more than ten papers, and applied for more than 50 patents