| Citation: |

Dongbin Zhu, Yi Li, Wensheng Shen, Zheng Zhou, Lifeng Liu, Xing Zhang. Resistive random access memory and its applications in storage and nonvolatile logic[J]. Journal of Semiconductors, 2017, 38(7): 071002. doi: 10.1088/1674-4926/38/7/071002

****

D B Zhu, Y Li, W S Shen, Z Zhou, L F Liu, X Zhang. Resistive random access memory and its applications in storage and nonvolatile logic[J]. J. Semicond., 2017, 38(7): 071002. doi: 10.1088/1674-4926/38/7/071002.

|

Resistive random access memory and its applications in storage and nonvolatile logic

DOI: 10.1088/1674-4926/38/7/071002

More Information

-

Abstract

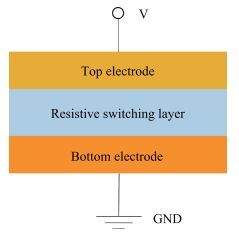

The resistive random access memory (RRAM) device has been widely studied due to its excellent memory characteristics and great application potential in different fields. In this paper, resistive switching materials, switching mechanism, and memory characteristics of RRAM are discussed. Recent research progress of RRAM in high-density storage and nonvolatile logic application are addressed. Technological trends are also discussed.-

Keywords:

- RRAM,

- memory,

- nonvolatile logic,

- metal-oxide,

- resistive switching

-

References

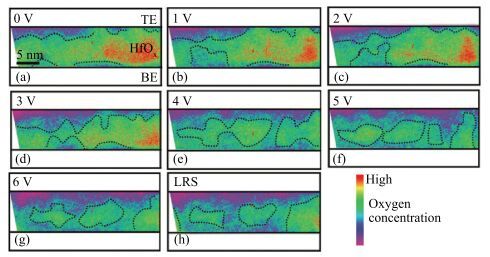

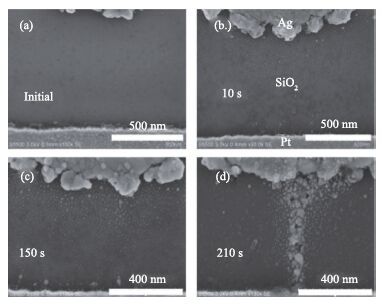

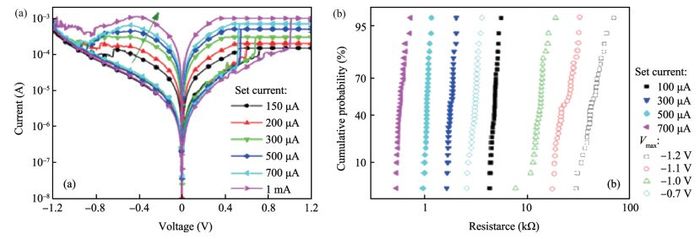

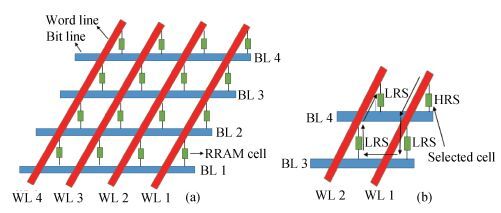

[1] Freitas R F, Wilcke W W. Storage-class memory: the next storage system technology. IBM J Res Dev, 2008, 52: 439 doi: 10.1147/rd.524.0439[2] Lelmini D. Resistive switching memories based on metal oxides: mechanisms, reliability and scaling. Semcond Sci Technol, 2016, 31: 063002 doi: 10.1088/0268-1242/31/6/063002[3] Borghetti J, Snider G S, Kuekes P J, et al. Memristive switches enable 'stateful' logic operations via material implication. Nature, 2010, 464: 873 doi: 10.1038/nature08940[4] Wong H S P, Salahuddin S. Memory leads the way to better computing. Nat Nanotechnol, 2015, 10: 191 doi: 10.1038/nnano.2015.29[5] Li H, Gao B, Chen Z, et al. A learnable parallel processing architecture towards unity of memory and computing. Sci Res, 2015, 5: 13330 https://www.ncbi.nlm.nih.gov/pubmed/26271243[6] Yang J J, Strukov D B, Stewart D R. Memristive devices for computing. Nat Nano, 2013, 8: 13 http://www.ece.ucsb.edu/~strukov/papers/2013/NatNano2013SI.pdf[7] Pan F, Gao S, Chen C, et al. Recent progress in resistive random access memories: materials, switching mechanisms, and performance. Mater Sci Eng R, 2014, 83: 1 doi: 10.1016/j.mser.2014.06.002[8] Salvo B D, Gerardi C, Schaijk R V, et al. Performance and reliability features of advanced nonvolatile memories based on discrete traps. IEEE Trans Device Mater Rel, 2004, 4: 77[9] Ielmimi D. Reliability issues and modeling of flash and post-flash memory. Microelectron Eng, 2009, 86: 1870 doi: 10.1016/j.mee.2009.03.054[10] Gallagher W J, Parkin S S P. Development of the magnetic tunnel junction MRAM at IBM: from first junctions to a 16-Mb MRAM demonstrator chip. IBM J Res Dev, 2006, 50: 5 doi: 10.1147/rd.501.0005[11] Kawahara T, Ito K, Takemura R, et al. Spin-transfer torque RAM technology: review and prospect. Microelectron Rel, 2012, 52: 613 doi: 10.1016/j.microrel.2011.09.028[12] Meena J S, Sze S M, Chand U, et al. Overview of emerging nonvolatile memory technologies. Nanoscale Res Lett, 2014, 9: 526 doi: 10.1186/1556-276X-9-526[13] Raoux S, Burr G W, Breitwisch M J, et al. Phase-change random access memory: a scalable technology. IBM J Res Dev, 2008, 52: 465 doi: 10.1147/rd.524.0465[14] Wong H S P, Lee H Y, Yu S M, et al. Metal-oxide RRAM. Proc IEEE, 2012, 1951: 1970 http://ieeexplore.ieee.org/document/6193402/[15] Tehrani S, Engel B, Slaughter J M, et al. Recent developments in magnetic tunnel junction MRAM. IEEE Trans Magn, 2000, 36: 2752 doi: 10.1109/20.908581[16] Kawahara T, Ito K, Takemura R, et al. Spin-transfer torque RAM technology: review and prospect. Microelectron Reliab, 2012, 52: 613 doi: 10.1016/j.microrel.2011.09.028[17] Wong H S P, Raoux S, Kim S, et al. Phase change memory. Proc IEEE, 2010, 98: 2201 doi: 10.1109/JPROC.2010.2070050[18] Ye C, Wu J J, He G, et al. Physical mechanism and performance factors of metal oxide based resistive switching memory: a review. J Mater Sci Technol, 2016, 32: 1 http://www.sciencedirect.com/science/article/pii/S1005030215001887?via%3Dihub[19] Balatti S, Ambrogio S, Wang Z Q, et al. Voltage-controlled cycling endurance of HfOx-based resistive-switching memory (RRAM). IEEE Trans Electron Devices, 2015, 62: 3365 doi: 10.1109/TED.2015.2463104[20] Hou Y, Celano U, Goux L, et al. Sub-10 nm low current resistive switching behavior in hafnium oxide stack. Appl Phys Lett, 2016, 108: 123106 doi: 10.1063/1.4944841[21] Hickmott T W. Low-frequency negative resistance in thin anodic oxide films. J Appl Phys, 1962, 33: 2669 doi: 10.1063/1.1702530[22] Asamitsu A, Tomioka Y, Kuwahara H, et al. Current switching of resistive states in magnetoresistive manganites. Nature, 1997, 50: 52 doi: 10.1038/40363[23] Beck A, Bednorz J G, Gerber C, et al. Reproducible switching effect in thin oxide films for memory applications. Appl Phys Lett, 2000, 139: 141 doi: 10.1063/1.126902[24] Watanabe Y, Bednorz J G, Bietsch A, et al. Current-driven insulator-conductor transition and nonvolatile memory in chromium-doped SrTiO3 single crystals. Appl Phys Lett, 2001, 3738: 3740 http://adsabs.harvard.edu/abs/2001ApPhL..78.3738W[25] Zhang H W, Liu L F, Gao B, et al. Gd-doping effect on performance of HfO2 based resistive switching memory devices using implantation approach. Appl Phys Lett, 2011, 98 https://www.researchgate.net/profile/Jinfeng_Kang/publication/224215825_Gd-doping_effect_on_performance_of_HfO2_based_resistive_switching_memory_devices_using_implantation_approach/links/02e7e5320f68167aef000000.pdf[26] Zhang F F, Li X, Gao B, et al. Complementary metal oxide semiconductor compatible Hf-based resistive random access memory with ultralow switching current/power. Jpn J Appl Phys, 2012, 51: 04DD08 doi: 10.1143/JJAP.51.04DD08/pdf[27] Liu L F, Yu D, Chen B, et al. Improvement of reliability characteristics of TiO2-based resistive switching memory device with an inserted ZnO layer. Jpn J Appl Phys, 2012, 51: 101101 doi: 10.1143/JJAP.51.101101/pdf[28] Bousoulas P, Stathopoulos S, Tsialoukis D, et al. Low-power and highly uniform 3-b multilevel switching in forming free TiO2-x-based RRAM with embedded Pt nanocrystals. IEEE Electron Device Lett, 2016, 874: 877 http://ieeexplore.ieee.org/abstract/document/7482775[29] Liu L F, Hou Y, Chen B, et al. Improved unipolar resistive switching characteristics of mixed-NiOx/NiOy-film-based resistive switching memory devices. Jpn J Appl Phys, 2015, 54: 094201 doi: 10.7567/JJAP.54.094201[30] Zhang H W, Gao B, Sun B, et al. Ionic doping effect in ZrO2 resistive switching memory. Appl Phys Lett, 2010, 96: 123502 doi: 10.1063/1.3364130[31] Sun B, Liu L F, Xu N, et al. The effect of current compliance on the resistive switching behaviors in TiN/ZrO2/Pt memory device. Jpn J Appl Phys, 2009, 48: 04C061 doi: 10.1143/JJAP.48.04C061/pdf[32] Prakash A, Park J, Song J, et al. Demonstration of low power 3-bit multilevel cell characteristics in a TaOx-based RRAM by stack engineering. IEEE Electron Device Lett, 2015, 32: 34 http://ieeexplore.ieee.org/Xplore/login.jsp?url=http%3A%2F%2Fieeexplore.ieee.org%2Fxpls%2Fabs_all.jsp%3Farnumber%3D6967704&authDecision=-203[33] Zhao Y D, Huang P, Chen Z, et al. Modeling and optimization of bilayered TaOx RRAM based on defect evolution and phase transition effects. IEEE Electron Device Lett, 2016, 63: 1524 doi: 10.1109/TED.2016.2532470[34] Xu N, Liu L F, Sun X, et al. Characteristics and mechanism of conduction/set process in TiN/ZnO/Pt resistance switching random-access memories. Appl Phys Lett, 2008, 92: 232112 doi: 10.1063/1.2945278[35] Tran X A, Zhu W, Liu W J, et al. A self-rectifying AlOy bipolar RRAM with sub-50-μA set/reset current for cross-bar architecture. IEEE Electron Device Lett, 2012, 33: 1402 doi: 10.1109/LED.2012.2210855[36] Son D I, Kim T W, Shim J H, et al. Flexible organic bistable devices based on graphene embedded in an insulating poly(methyl methacrylate) polymer layer. Nano Lett, 2010, 10: 2441 doi: 10.1021/nl1006036[37] Liu L F, Yu D, Ma W J, et al. Multilevel resistive switching in Ag/SiO2/Pt resistive switching memory device. Jpn J Appl Phys, 2015, 54: 021802 doi: 10.7567/JJAP.54.021802[38] Kuo C C, Chen I C, Shih C C, et al. Galvanic effect of Au--Ag electrodes for conductive bridging resistive switching memory. IEEE Electron Device Lett, 2015, 36: 1321 doi: 10.1109/LED.2015.2496303[39] Palma G, Vianello E, Thomas O, et al. A novel HfO2-GeS2-Ag based conductive bridge RAM for reconfigurable logic applications. Solid-State Device Research Conference (ESSDERC), 2013: 264[40] Ota K, Belmonte A, Chen Z, et al. Impact of the filament morphology on the retention characteristics of Cu/Al2O3-based CBRAM devices. IEDM, 2016: 556[41] Bernard Y, Renard V T, Gonon P, et al. Back-end-of-line compatible conductive bridging RAM based on Cu and SiO2. Microelect Eng, 2011, 88: 814 doi: 10.1016/j.mee.2010.06.041[42] Belmonte A, Egraeve D, Fantini A, et al. Origin of the current discretization in deep reset states of an Al2O3/Cu-based conductive-bridging memory, and impact on state level and variability. Appl Phys Lett, 2014, 104: 233508 doi: 10.1063/1.4883856[43] Waser R, Aono M. Nanoionics-based resistive switching memories. Nat Mater, 2007, 6: 833 doi: 10.1038/nmat2023[44] Gao B, Yu S, Xu N, et al. Oxide-based RRAM switching mechanism: a new ion-transport-recombination model. IEDM Tech Dig, 2008: 4796751 http://ieeexplore.ieee.org/document/4796751/authors[45] Son J Y, Shin Y H. Direct observation of conducting filaments on resistive switching of NiO thin films. Appl Phys Lett, 2008, 92: 222106 doi: 10.1063/1.2931087[46] Celano Y, Chen Y Y, Wouters D J, et al. Filament observation in metal-oxide resistive switching devices. Appl Phys Lett, 2013, 102: 121602 doi: 10.1063/1.4798525[47] Kim D C, Seo S, Ahn S E, et al. Electrical observations of filamentary conductions for the resistive memory switching in NiO films. Appl Phys Lett, 2006, 88: 202102 doi: 10.1063/1.2204649[48] Guan W, Long S, Liu Q, et al. Nonpolar nonvolatile resistive switching in Cu doped ZrO2. IEEE Electron Device Lett, 2008, 29: 434 doi: 10.1109/LED.2008.919602[49] Rozenberg M J, Inoue I H, Sanchez M J. Nonvolatile memory with multilevel switching: a basic model. Phys Rev Lett, 2004, 92: 178302 doi: 10.1103/PhysRevLett.92.178302[50] Fors R, Khartsev S I, Grishin A M. Giant resistance switching in metal--insulator--manganite junctions: evidence for Mott transition. Phys Rev B, 2005, 71: 045305 doi: 10.1103/PhysRevB.71.045305[51] Tsymbal E Y, Kohlstedt H. Tunneling across a ferroelectric. Science, 2006, 313: 181 doi: 10.1126/science.1126230[52] Gao B, Sun B, Zhang H W, et al. Unified physical model of bipolar oxide-based resistive switching memory. IEEE Electron Device Lett, 2009, 30: 1326 doi: 10.1109/LED.2009.2032308[53] Gao B, Kang J F, Chen Y S, et al. Oxide-based RRAM: unified microscopic principle for both unipolar and bipolar switching. IEDM Tech Dig, 2011: 17.4.1 http://ieeexplore.ieee.org/xpl/abstractAuthors.jsp?reload=true&arnumber=6131573&searchWithin%3Dmemory%26searchWithin%3Dstorage+class+memory%26sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A6131464%29[54] Huang P, Liu X Y, Li W H, et al. A physical based analytic model of RRAM operation for circuit simulation. IEDM Tech Dig, 2012: 26.6.1 http://ieeexplore.ieee.org/document/6479110/?reload=true&arnumber=6479110&punumber%3D6471855%26sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A6478950%29%26pageNumber%3D2%26rowsPerPage%3D100[55] Huang P, Liu X Y, Chen B, et al. A physics-based compact model of metal--oxide-based RRAM DC and AC operations. IEEE Trans Electron Devices, 2013, 4090: 4097 https://www.researchgate.net/profile/Kangliang_Wei/publication/260590321_A_Physics-Based_Compact_Model_of_Metal-Oxide-Based_RRAM_DC_and_AC_Operations/links/5582a8bf08ae12bde6e4e60c.pdf[56] Li H T, Huang P, Gao B, et al. A SPICE model of resistive random access memory for large-scale memory array simulation. IEEE Electron Device Lett, 2014, 211: 21 https://www.researchgate.net/publication/260719823_A_SPICE_Model_of_Resistive_Random_Access_Memory_for_Large-Scale_Memory_Array_Simulation[57] Gao B, Zhang H W, Yu S M, et al. Oxide-based RRAM: uniformity improvement using a new material-oriented methodology. VLSI Technol, 2009, 30: 31 http://ieeexplore.ieee.org/document/5200623/[58] Valov I, Linn E, Tappertzhofen S, et al. Nanobatteries in redox-based resistive switches require extension of memristor theory. Nat Commun, 2013, 4: 1771 doi: 10.1038/ncomms2784[59] Kim S, Choi S H, Lu W. Comprehensive physical model of dynamic resistive switching in an oxide memristor. ACS Nano, 2014, 8: 2369 doi: 10.1021/nn405827t[60] Hubbard W A, Kerelsky A, Jasmin G, et al. Nanofilament formation and regeneration during Cu/Al2O3 resistive memory switching. Nano Lett, 2015, 15: 3983 doi: 10.1021/acs.nanolett.5b00901[61] Liu Q, Sun J, Lv H B, et al. Real-time observation on dynamic growth/dissolution of conductive filaments in oxide-electrolyte-based ReRAM. Adv Mater, 2012, 24: 1844 doi: 10.1002/adma.v24.14[62] Son J Y, Shin Y H. Direct observation of conducting filaments on resistive switching of NiO thin films. Appl Phys Lett, 2008, 22: 2106 http://cat.inist.fr/?aModele=afficheN&cpsidt=20477368[63] Celano U, Chen Y Y, Wouters D J, et al. Filament observation in metal--oxide resistive switching devices. Appl Phys Lett, 2013, 102: 121602 doi: 10.1063/1.4798525[64] Celano U, Goux L, Degraeve R, et al. Imaging the three-dimensional conductive channel in filamentary-based oxide resistive switching memory. Nano Lett, 2015, 15(12): 7970 doi: 10.1021/acs.nanolett.5b03078[65] Park G S, Kim Y B, Park Y S, et al. In situ observation of filamentary conducting channels in an asymmetric Ta2O5-x/TaO2-x bilayer structure. Nat Commun, 2013, 4: 2382[66] Zhu X J, Su W J, Liu Y W, et al. Observation of conductance quantization in oxide-based resistive switching memory. Adv Mater, 2012, 24: 3941 doi: 10.1002/adma.v24.29[67] Li C, Gao B, Yao Y, et al. Direct observations of nano lament evolution in switching processes in HfO2-based resistive random access memory by in situ TEM studies. Adv Mater, 2017, 29: 1602976 doi: 10.1002/adma.201602976[68] Yang U C, Gao P, Gaba S, et al. Observation of conducting lament growth in nanoscale resistive memories. Nat Commun, 2012, 3: 732 doi: 10.1038/ncomms1737[69] Celanoa U, Gouxa L, Opsomer K, et al. Scanning probe microscopy as a scalpel to probe filament formation in conductive bridging memory devices. Microelectron Eng, 2014, 120: 67 doi: 10.1016/j.mee.2013.06.001[70] Celano U, Goux L, Belmonte A, et al. Understanding the dual nature of the filament dissolution in conductive bridging devices. J Phys Chem Lett, 2015, 6: 1919 doi: 10.1021/acs.jpclett.5b00633[71] Sun H T, Liu Q, Li C F, et al. Direct observation of conversion between threshold switching and memory switching induced by conductive filament morphology. Adv Fun Mater, 2014, 5679: 5686 http://onlinelibrary.wiley.com/resolve/doi?DOI=10.1002/adfm.201401304[72] Lee H Y, Chen P S, Wu Y Y, et al. Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO2 based RRAM. IEDM Tech Dig, 2008: 297 http://ieeexplore.ieee.org/xpl/abstractAuthors.jsp?reload=true&tp=&arnumber=4796677&contentType=Conference+Publications&sortType%3Dasc_p_Sequence%26filter%3DAND(p_IS_Number%3A4796592)%26rowsPerPage%3D100[73] Goux L, Sankaran K, Kar G, et al. Field-driven ultrafast sub-ns programming in W/Al2O3/Ti/CuTe-based 1T1R CBRAM system. Proc Symp VLSI Technol, 2012: 69[74] Chen C Y, Goux L, Fantini A, et al. Doped Gd--O based RRAM for embedded application. IMW, 2016, 1: 4 http://ieeexplore.ieee.org/document/7495266/[75] Piccolboni G, Parise M, Molas G, et al. Vertical CBRAM (V-CBRAM): from experimental data to design perspectives. IEEE International Memory Workshop (IMW), 2016 http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=7495296[76] Bousoulas P, Asenov P, Tsoukalas D. Physical modelling of the SET/RESET characteristics and analog properties of TiOx/HfO2-x/TiOx-based RRAM devices. International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2016: 249[77] Woo J, Belmonte A, Redolfi A, et al. Introduction of WO3 layer in a Cu-based Al2O3 conductive bridge RAM system for robust cycling and large memory window. IEEE J Electron Devices, 2016, 4: 163 doi: 10.1109/JEDS.2016.2526632[78] Hsu C W, Wang I T, Lo C L, et al. Self-rectifying bipolar TaOx/TiO2 RRAM with superior endurance over 10E12 cycles for 3D high-density storage-class memory. Proc Symp VLSI Technol, 2013: 166[79] Belmonte A, Kim W, Chan B T, et al. 90 nm W/Al2O3/Ti/Cu 1T1R CBRAM cell showing low-power, fast and disturb-free operation. IEEE International Memory Workshop, 2013, 26: 29[80] Yang Y C, Chen C, Zeng F, et al. Multilevel resistance switching in Cu/TaOx/Pt structures induced by a coupled mechanism. J Appl Phys, 2010, 107: 093701 doi: 10.1063/1.3399152[81] Sedghi N, Li H, Brunell F, et al. The role of nitrogen doping in ALD Ta2O5 and its influence on multilevel cell switching in RRAM. Appl Phys Lett, 2017, 110: 102902 doi: 10.1063/1.4978033[82] Kim W, Menzel S, Wouters D J, et al. 3-bit multilevel switching by deep reset phenomenon in Pt/W/TaOx/Pt-ReRAM devices. IEEE Electron Device Lett, 2016, 37: 564 doi: 10.1109/LED.2016.2542879[83] Tsuruoka T, Hasegawa T, Terabe K, et al. Conductance quantization and synaptic behavior in a Ta2O5-based atomic switch. Nanotech, 2012, 23: 435705 doi: 10.1088/0957-4484/23/43/435705[84] Deng Y, Huang P, Chen B, et al. RRAM crossbar array with cell selection device: a device and circuit interaction study. IEEE Trans Electron Devices, 2013, 60: 719 doi: 10.1109/TED.2012.2231683[85] Kim S, Kim H, Choi S, et al. Numerical study of read scheme in one-selector one-resistor crossbar array. Solid State Electron, 2015, 114: 8 http://silk.kookmin.ac.kr/img_up/shop_pds/kmusilk/contents/myboard/S.-J.Choi.pdf[86] Lee M, Park Y, Suh D, et al. Two series oxide resistors applicable to high speed and high density nonvolatile memory. Adv Mat, 2007, 19: 3919 doi: 10.1002/(ISSN)1521-4095[87] Koo Y, Baek K, Hwang H, et al. Te-based amorphous binary OTS device with excellent selector characteristics for x-point memory applications. Proc Symp VLSI Technol, 2016: 16322184 http://ieeexplore.ieee.org/stamp/redirect.jsp?arnumber=/7569798/7573353/07573389.pdf[88] Burr G W, Virwani K, Shenoy R S, et al. Large-scale (512 kbit) integration of multilayer-ready access-devices based on mixed-ionic-electronic-conduction (Miec) at 100 yield. Proc Symp VLSI Technol, 2012: 41[89] Lee W, Park J, Shin J, et al. Varistor-type bidirectional switch (JMAX >>10×107A/cm2, selectivity 10E4) for 3D bipolar resistive memory arrays. Proc Symp VLSI Technol, 2012: 37[90] Jo S H, Kumar T, Narayanan S, et al. 3D-stackable crossbar resistive memory based on field assisted super-linear threshold (FAST) selector. IEDM Tech Dig, 2014: 6.7.1[91] Kim K H, Jo S H, Gaba S, et al. Nanoscale resistive memory with intrinsic diode characteristics and long endurance. Appl Phys Lett, 2010, 96: 053106 doi: 10.1063/1.3294625[92] Son M, Lee J, Park J, et al. Excellent selector characteristics of nanoscale box for high-density bipolar ReRAM applications. IEEE Electron Device Lett, 2011, 32: 1579 doi: 10.1109/LED.2011.2163697[93] Kim S, Liu X, Park J, et al. Ultrathin V2O5/NbO2 hybrid memory with both memory and selector characteristics for high density 3D vertically stackable RRAM applications. Proc Symp VLSI Technol, 2012: 155[94] Aluguri R, Tseng T. Overview of selector devices for 3-D stackable cross point RRAM arrays. IEEE J Electron Devices, 2016, 4: 294 doi: 10.1109/JEDS.2016.2594190[95] Kim W G, Lee H M, Kim B Y, et al. NbO2-based low power and cost effective 1S1R switching for high density cross point ReRAM application. Proc Symp VLSI Technol, 2014[96] Koo Y, Baek K, Hwang H. Te-based amorphous binary OTS device with excellent selector characteristics for x-point memory applications. Proc Symp VLSI Technol, 2016: 1 http://ieeexplore.ieee.org/stamp/redirect.jsp?arnumber=/7569798/7573353/07573389.pdf[97] Gopalakrishnan K, Shenoy R S, Rettner C T, et al. Highly-scalable novel access device based on mixed ionic electronic conduction (MIEC) materials for high density phase change memory (PCM) arrays. Proc Symp VLSI Technol, 2010: 205 http://geoffreyburr.org/papers/VLSI2010.pdf[98] Lee W, Park J, Kim S, et al. High current density and nonlinearity combination of selection device based on TaOx/TiO2/TaOx structure for one selector---one resistor arrays. ACS Nano, 2012, 9: 8166[99] Jo S H, Kumar T, Narayanan S, et al. 3D stackable crossbar resistive memory based on field assisted superlinear threshold (FAST) selector. IEDM Tech Dig, 2014: 6.7.1 https://www.crossbar-inc.com/assets/resource/paper/IEDM2014-Paper-3D-Stackable-Crossbar-Resistive-Memory.pdf[100] Luo Q, Xu X, Liu H, et al. Cu BEOL compatible selector with high selectivity (>10×107), extremely low off-current (~pA) and high endurance (>10×1010). IEDM Tech Dig, 201: 10. 4. 1[101] Luo Q, Xu X, Lv H, et al. Fully BEOL compatible TaOx-based selector with high uniformity and robust performance. IEDM Tech Dig, 2016: 11.7.1[102] Hudec B, Hsu C W, Wang I T, et al. 3D resistive RAM cell design for high-density storage class memory-a review. Sci Chi Inf Sci, 2016, 59: 061403 doi: 10.1007/s11432-016-5566-0[103] Hsieh M C, Liao Y C, Chin Y W, et al. Ultra high density 3D via RRAM in pure 28 nm CMOS process. IEDM Tech Dig, 2013: 10.3.1 http://ieeexplore.ieee.org/document/6724600/?arnumber=6724600&sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A6724533%29%26pageNumber%3D3[104] Seok J, Song S J, Yoon J H, et al. A review of three-dimensional resistive switching cross-bar array memories from the integration and materials property points of view. Adv Funct Mater, 2015, 24: 5316[105] Chen H, Gao B, Li H T, et al. Towards high-speed, write-disturb tolerant 3D vertical RRAM arrays. Proc Symp VLSI Technol, 2014 http://ieeexplore.ieee.org/document/6894434/keywords[106] Deng Y X, Chen H Y, Gao B, et al. Design and optimization methodology for 3D RRAM arrays. IEDM Tech Dig, 2013: 25.7.1 http://ieeexplore.ieee.org/Xplore/login.jsp?url=http%3A%2F%2Fieeexplore.ieee.org%2Fxpls%2Ficp.jsp%3Farnumber%3D6724693&authDecision=-203[107] Yu S M, Chen H Y, Gao B, et al. HfOx-based vertical resistive switching random access memory suitable for bit-cost-effective three-dimensional cross-point architecture. ACS Nano, 2014, 7: 320[108] Li H T, Li K S, Lin C H, et al. Four-layer 3D vertical RRAM integrated with FinFET as a versatile computing unit for brain-inspired cognitive information. Proc Symp VLSI Technol, 2016[109] Xu X, Luo Q, Gong T, et al. Fully CMOS compatible 3D vertical RRAM with self-aligned self-selective cell enabling sub-5nm scaling. Proc Symp VLSI Technol, 2016 http://ieeexplore.ieee.org/stamp/redirect.jsp?arnumber=/7569798/7573353/07573388.pdf[110] Luo Q, Xu X, Liu H, et al. Demonstration of 3D vertical RRAM with ultra low-leakage, high-selectivity and self-compliance memory cells. IEDM Tech Dig, 2015: 10.2.1 http://ieeexplore.ieee.org/stamp/redirect.jsp?arnumber=/7402013/7409598/07409667.pdf[111] Luo Q, Xu X, Liu H, et al. Super non-linear RRAM with ultra-low power for 3D vertical nano-crossbar arrays. Nanoscale, 2016, 8: 15629 doi: 10.1039/C6NR02029A[112] Yu S M, Deng Y X, Gao B, et al. Design guidelines for 3D RRAM cross-point architecture. IEEE International Symposium on Circuits and Systems (ISCAS), 2014: 421 http://ieeexplore.ieee.org/document/6865155/[113] Chen P Y, Yu S M. Impact of vertical RRAM device characteristics on 3D cross-point array design. International Memory Workshop (IMW), 2014 http://ieeexplore.ieee.org/xpl/abstractAuthors.jsp?reload=true&arnumber=6849382[114] Chen P Y, Li Z W, Yu S M, et al. Design tradeoffs of vertical RRAM-based 3-D cross-point array. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2016, 24: 3460 doi: 10.1109/TVLSI.2016.2553123[115] Li Z W, Chen P Y, Liu H J, et al. Quasi-analytical model of 3-D vertical-RRAM array architecture for MB-level design. IEEE Trans Electron Devices, 2017: 99[116] Adam G C, Hoskins B D, Prezioso M, et al. 3-D memristor crossbars for analog and neuromorphic computing applications. IEEE Trans Electron Devices, 2017, 312: 318[117] Bai Y, Wu H Q, Wang K, et al. Stacked 3D RRAM array with graphene/CNT as edge electrodes. Sci Rep, 2015, 5: 13785 doi: 10.1038/srep13785[118] Bai Y, Wu H Q, Wu R, et al. Study of multi-level characteristics for 3D vertical resistive switching memory. Sci Rep, 2014, 4: 5780 https://www.researchgate.net/profile/Huaqiang_Wu/publication/264126799_Study_of_Multi-level_Characteristics_for_3D_Vertical_Resistive_Switching_Memory/links/543533b70cf2bf1f1f28281f.pdf?disableCoverPage=true[119] Ni L, Wang Y, Yu H, et al. An energy-efficient matrix multiplication accelerator by distributed in-memory computing on binary RRAM crossbar. ASP-DAC, 2016, 280: 285 http://ieeexplore.ieee.org/stamp/redirect.jsp?arnumber=/7422345/7427971/07428024.pdf[120] Li H, Chen Z, Ma W, et al. Nonvolatile logic and in situ data transfer demonstrated in crossbar resistive RAM array. IEEE Electron Device Lett, 2015, 1142: 1145 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=7274656&filter%3DAND%28p_IS_Number%3A7302615%29[121] Zhou Y X, Li Y, Xu L, et al. Boolean logics in three steps with two anti-serially connected memristors. Appl Phys Lett, 2015, 106: 233502 doi: 10.1063/1.4922344[122] Zhou Y X, Li Y, Su Y T, et al. Nonvolatile reconfigurable sequential logic in HfO2 resistive random access memory array. Nanoscale, 2017, 9: 6649 doi: 10.1039/C7NR00934H[123] Li Y, Zhou Y X, Xu L, et al. Realization of functional complete stateful boolean logic in memristive crossbar. ACS Appl Mater Interfaces, 2016, 8: 34559 doi: 10.1021/acsami.6b11465[124] Kang J F, Huang P, Gao B, et al. Design and application of oxide-based resistive switching devices for novel computing architectures. IEEE J Electron Devices, 2016, 307: 313 http://ieeexplore.ieee.org/iel7/6245494/7549118/07486051.pdf[125] Rosezin R, Linn E, Kugeler C, et al. Crossbar logic using bipolar and complementary resistive switches. IEEE Electron Device Lett, 2011, 32: 710 doi: 10.1109/LED.2011.2127439[126] Linn E, Rosezin R, Tappertzhofen S, et al. Beyond von Neumann--logic operations inpassive crossbar arrays alongside memory operations. Nanotechnology, 2012, 23: 305205 doi: 10.1088/0957-4484/23/30/305205[127] Breuer T, Siemon A, Linn E, et al. A HfO2-based complementary switching crossbar Adder. Adv Electron Mater, 2015, 1: 64[128] Siemon A, Menzel S, Waser R, et al. A complementary resistive switch-based crossbar array adder. IEEE J Emerg Sel Top Circuits Syst, 2014, 5: 64[129] Gokmen T, Vlasov Y. Acceleration of deep neural network training with resistive cross-point devices. arXiv preprint arXiv, 2016, 1603: 07341 https://arxiv.org/pdf/1603.07341[130] Huang P, Kang J F, Zhao Y D, et al. Reconfigurable nonvolatile logic operations in resistance switching crossbar array for large-scale circuits. Adv Mater, 2016, 28: 9758 doi: 10.1002/adma.201602418[131] Chen Y C, Chang Y F, Wu X H, et al. Dynamic conductance characteristics in HfOx based resistive random access memory. RSC Adv, 2017, 12984: 12989[132] Lim S, Yoo J, Song J, et al. Excellent threshold switching device (IOFF~1 pA) with atom-scale metal filament for steep slope ( < 5 mV/dec), ultra low voltage (VDD = 0.25 V) FET applications. IEDM, 2016: 34.7.1[133] Chang K C, Zhang R, Chang T C, et al. High performance, excellent reliability multifunctional graphene oxide doped memristor achieved by self-protective compliance current structure. IEDM, 2014: 33.3.2[134] Huang Y, Shen Z H, Wu Y, et al. Amorphous ZnO based resistive random access memory. RSC Adv, 2016, 17867: 17872 http://pubs.rsc.org/en/Content/ArticleLanding/RA/2016/C5RA22728C#! -

Proportional views

DownLoad:

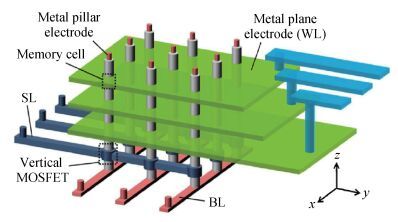

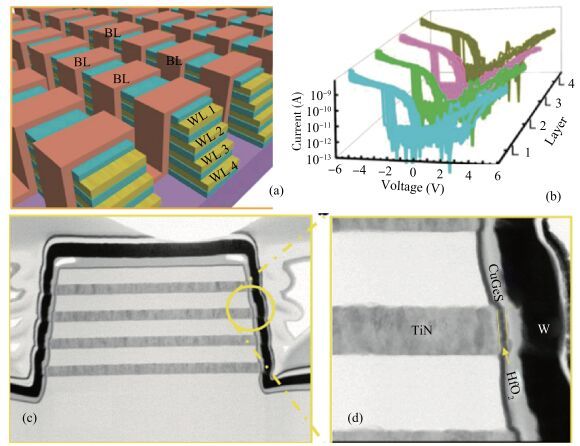

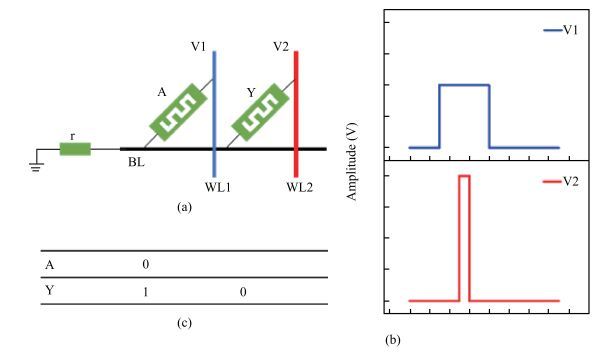

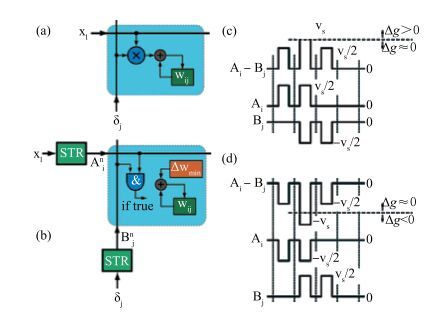

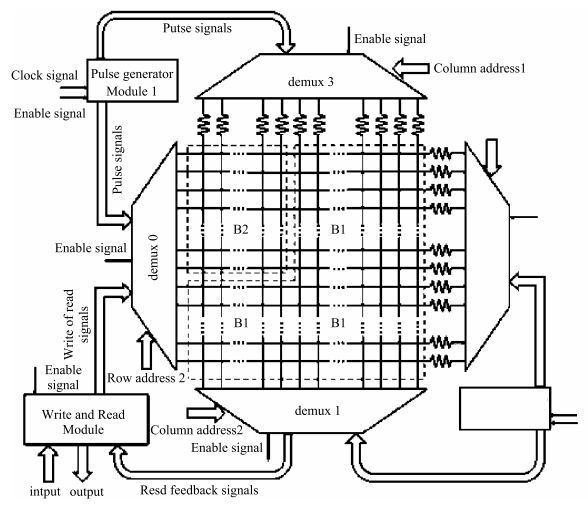

DownLoad: