| Citation: |

Jiang Lu, Xiaoli Tian, Shuojin Lu, Hongyu Zhou, Yangjun Zhu, Zhengsheng Han. Dynamic avalanche behavior of power MOSFETs and IGBTs under unclamped inductive switching conditions[J]. Journal of Semiconductors, 2013, 34(3): 034002. doi: 10.1088/1674-4926/34/3/034002

****

J Lu, X L Tian, S J Lu, H Y Zhou, Y J Zhu, Z S Han. Dynamic avalanche behavior of power MOSFETs and IGBTs under unclamped inductive switching conditions[J]. J. Semicond., 2013, 34(3): 034002. doi: 10.1088/1674-4926/34/3/034002.

|

Dynamic avalanche behavior of power MOSFETs and IGBTs under unclamped inductive switching conditions

DOI: 10.1088/1674-4926/34/3/034002

More Information

-

Abstract

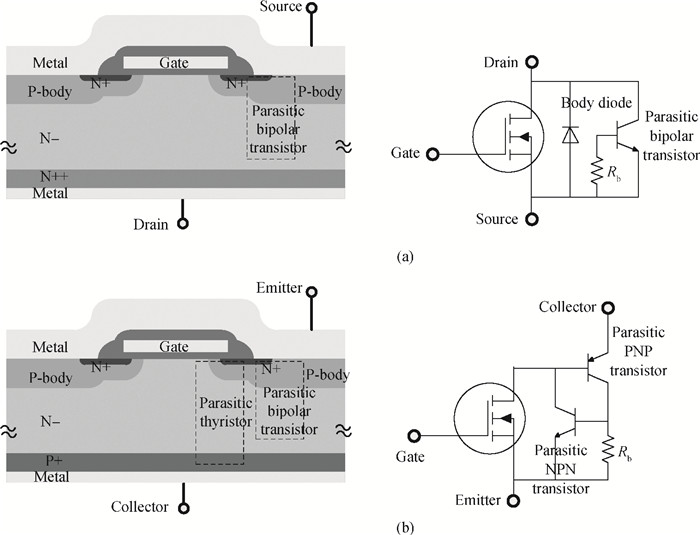

The ability of high-voltage power MOSFETs and IGBTs to withstand avalanche events under unclamped inductive switching (UIS) conditions is measured. This measurement is to investigate and compare the dynamic avalanche failure behavior of the power MOSFETs and the IGBT, which occur at different current conditions. The UIS measurement results at different current conditions show that the main failure reason of the power MOSFETs is related to the parasitic bipolar transistor, which leads to the deterioration of the avalanche reliability of power MOSFETs. However, the results of the IGBT show two different failure behaviors. At high current mode, the failure behavior is similar to the power MOSFETs situation. But at low current mode, the main failure mechanism is related to the parasitic thyristor activity during the occurrence of the avalanche process and which is in good agreement with the experiment result.-

Keywords:

- UIS test,

- parasitic bipolar transistor,

- power MOSFETs,

- IGBT,

- parasitic thyristor

-

References

[1] Daniel D, Andrej V. Analysis of the electrical and thermal properties of power DMOS devices during UIS supported by 2-D process and device simulation. The Fifth International Conference on Advanced Semiconductor Device and Microsystems, 2004:211 http://ieeexplore.ieee.org/document/1441198/?reload=true&arnumber=1441198[2] Pawel I, Siemieniec R, Rösch M, et al. Experimental study and simulations on two different avalanche modes in trench power MOSFETs. IET Circuits Devices Syst, 2007, 1(5):341 doi: 10.1049/iet-cds:20060370[3] Daniel D, Andrej V, Juraj M, et al. Evaluation of the ruggedness of power DMOS transistor from electro-thermal simulation of UIS behavior. Solid-State Electron, 2008, 52:892 doi: 10.1016/j.sse.2007.12.006[4] Breglio G, Irace A, Napoli E, et al. Study of a failure mechanism during UIS switching of planar PT-IGBT with current sense cell. Microelectron Reliab, 2007, 47:1756 doi: 10.1016/j.microrel.2007.07.009[5] Lefranc P, Planson D, Morel H, et al. Analysis of the dynamic avalanche of punch through insulated gate bipolar transistor (PT-IGBT). Solid-State Electron, 2009, 53:944 doi: 10.1016/j.sse.2009.06.009[6] Riccio M, Irace A, Breglio G, et al. Electro-thermal instability in multi-cellular trench-IGBTs in avalanche condition experiments and simulations. The 23rd International Symposium on Power Semiconductor Devices & IC's, 2011:124 http://ieeexplore.ieee.org/document/5890806/authors[7] Lu Jiang, Wang Lixin, Lu Shuojin, et al. Study on the avalanche behavior of power MOSFETs under different temperature conditions. Journal of Semiconductors, 2011, 32(1):014001 doi: 10.1088/1674-4926/32/1/014001[8] Tim M, Marco S, Anthony M, et al. Power MOSFET avalanche design guidelines. International Rectifier Application Note: AN-1005[9] Abdus S. Insulated gate bipolar transistor (IGBT) basics. IXTS Application Note: IXAN0063[10] Baliga B J. Fundamentals of power semiconductor devices. Springer, 2008 doi: 10.1007%2F978-0-387-47314-7 -

Proportional views

DownLoad:

DownLoad: