| Citation: |

Yaqian Qian, Shushan Qiao, Rongqiang Yang. Variation tolerance for high-speed negative capacitance FinFET SRAM bit cell[J]. Journal of Semiconductors, 2020, 41(6): 062403. doi: 10.1088/1674-4926/41/6/062403

****

Y Q Qian, S S Qiao, R Q Yang, Variation tolerance for high-speed negative capacitance FinFET SRAM bit cell[J]. J. Semicond., 2020, 41(6): 062403. doi: 10.1088/1674-4926/41/6/062403.

|

Variation tolerance for high-speed negative capacitance FinFET SRAM bit cell

DOI: 10.1088/1674-4926/41/6/062403

More Information

-

Abstract

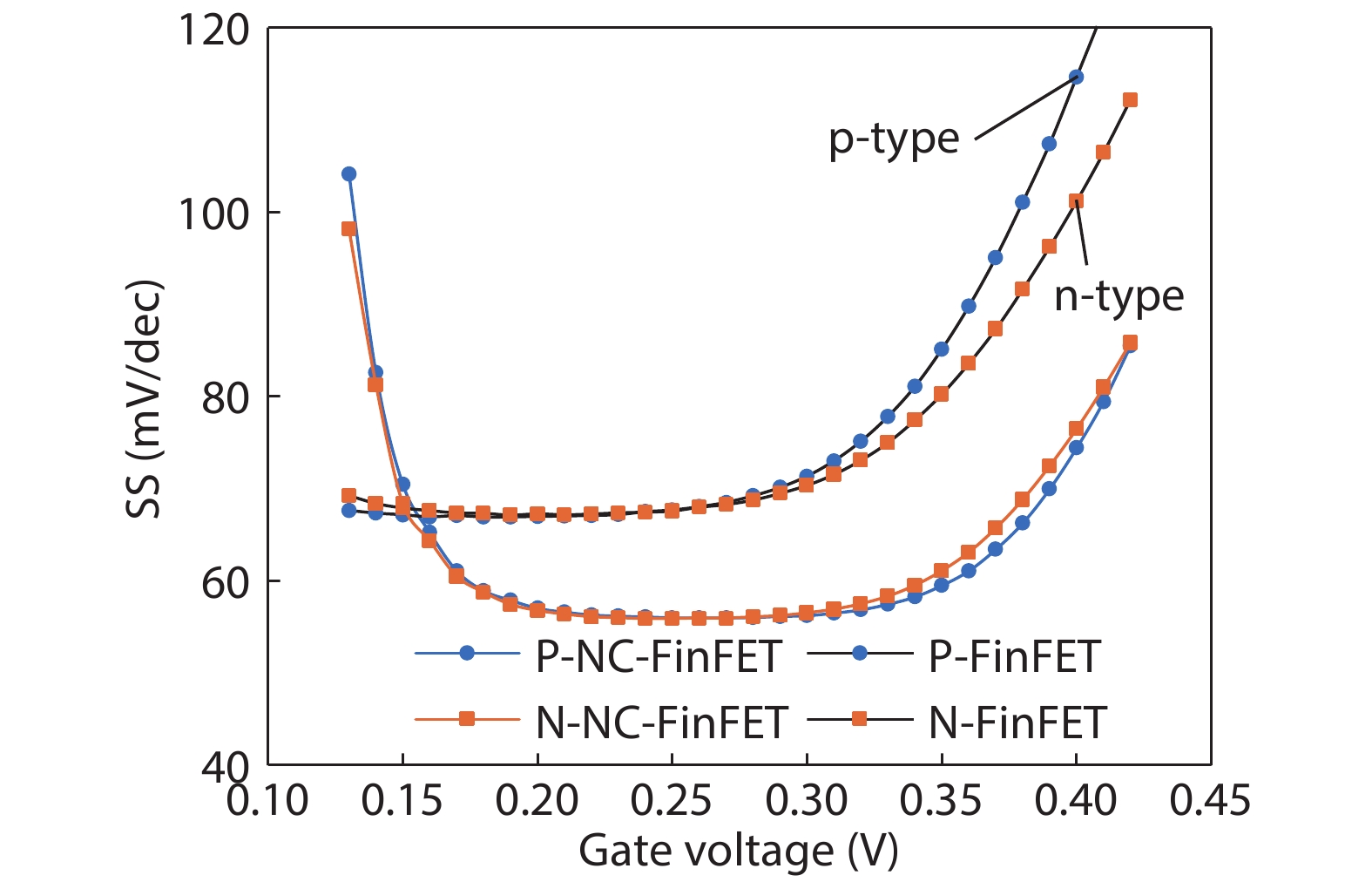

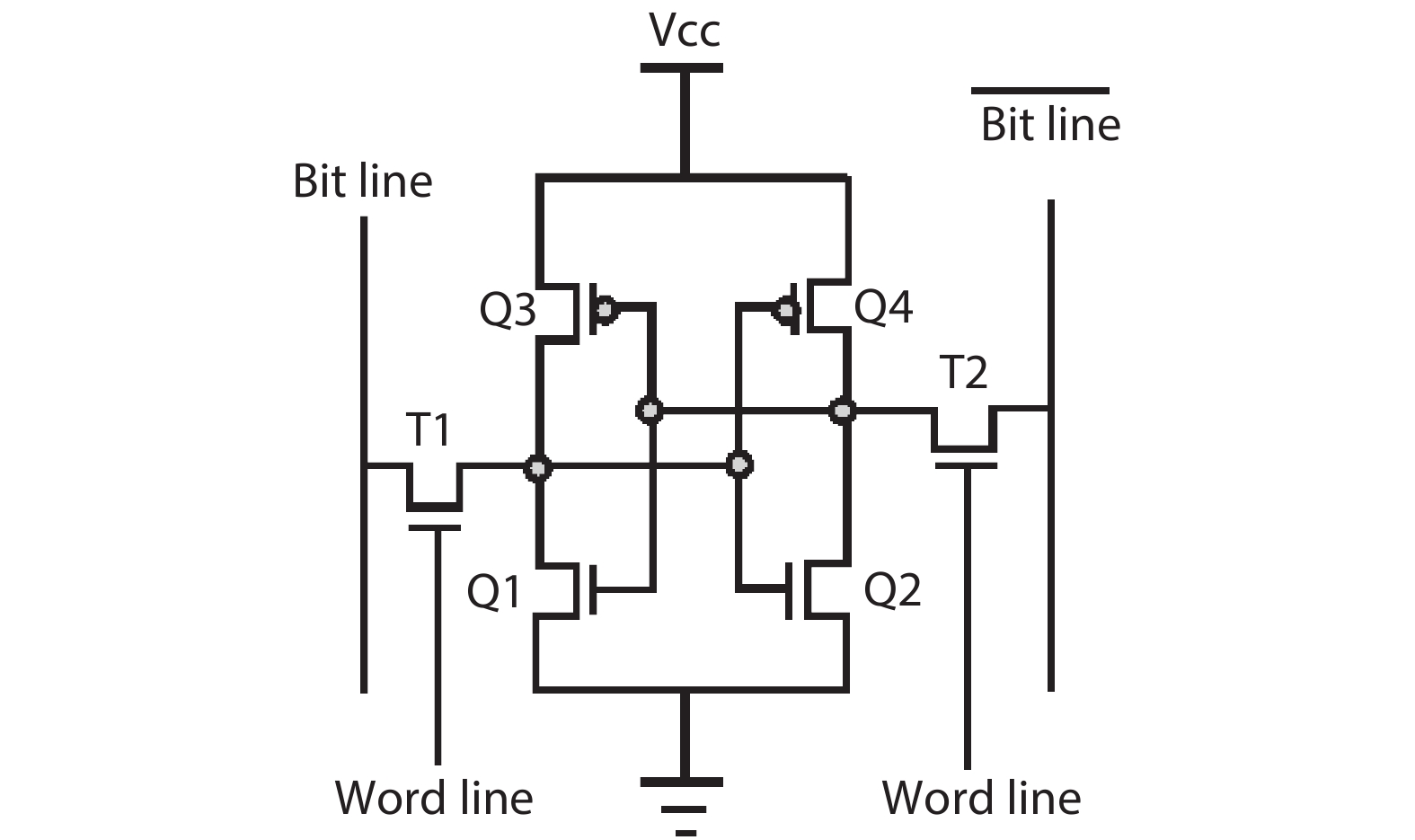

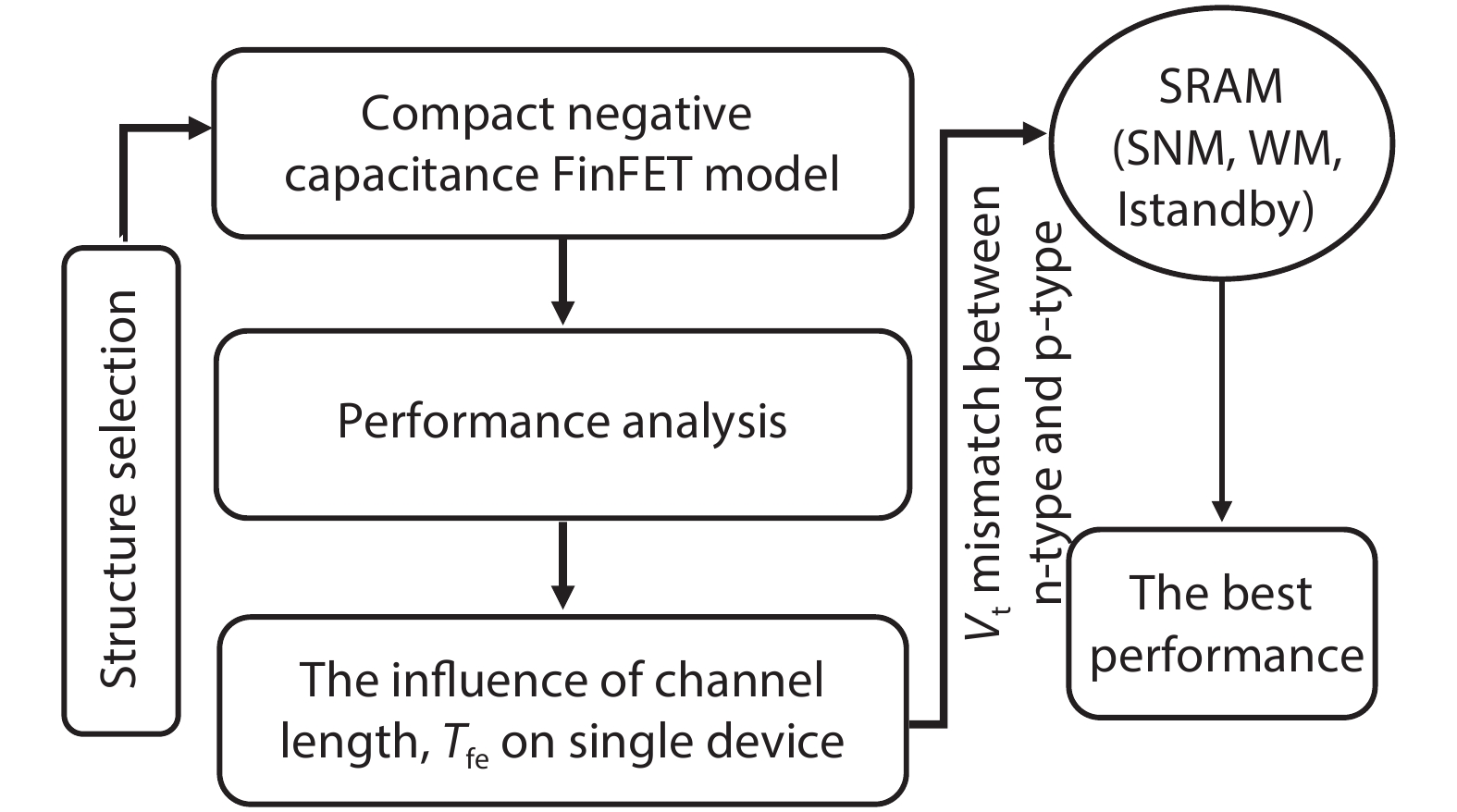

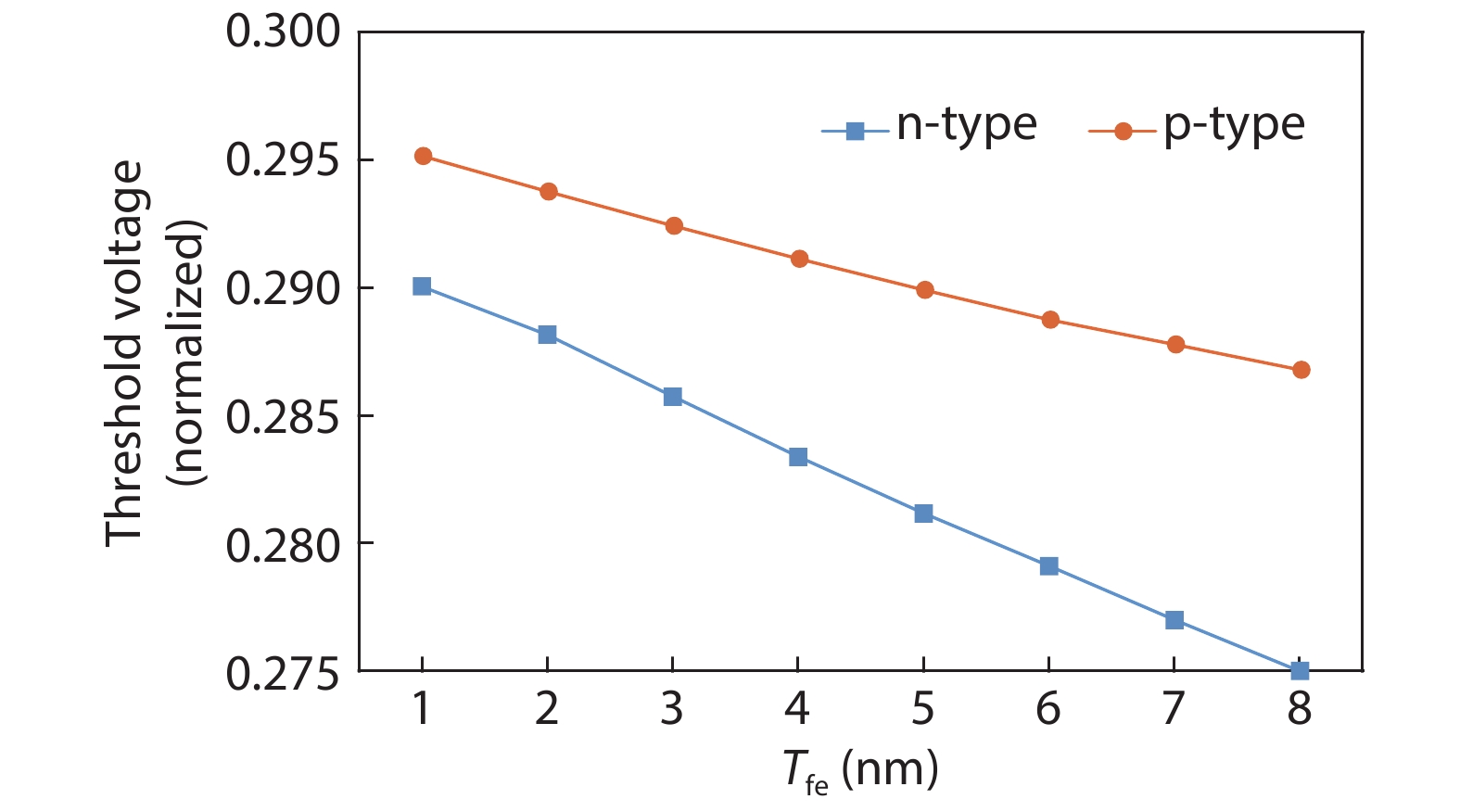

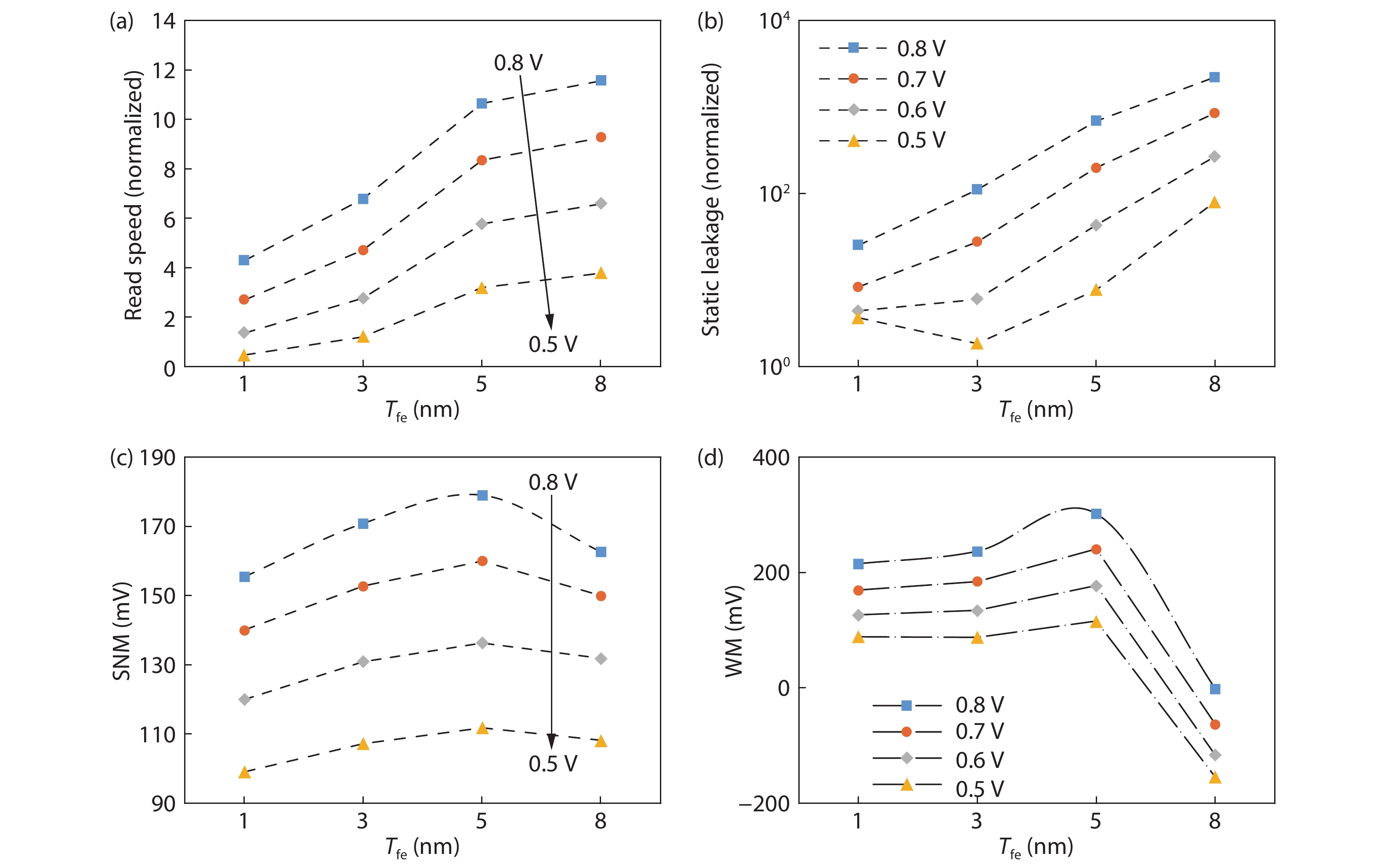

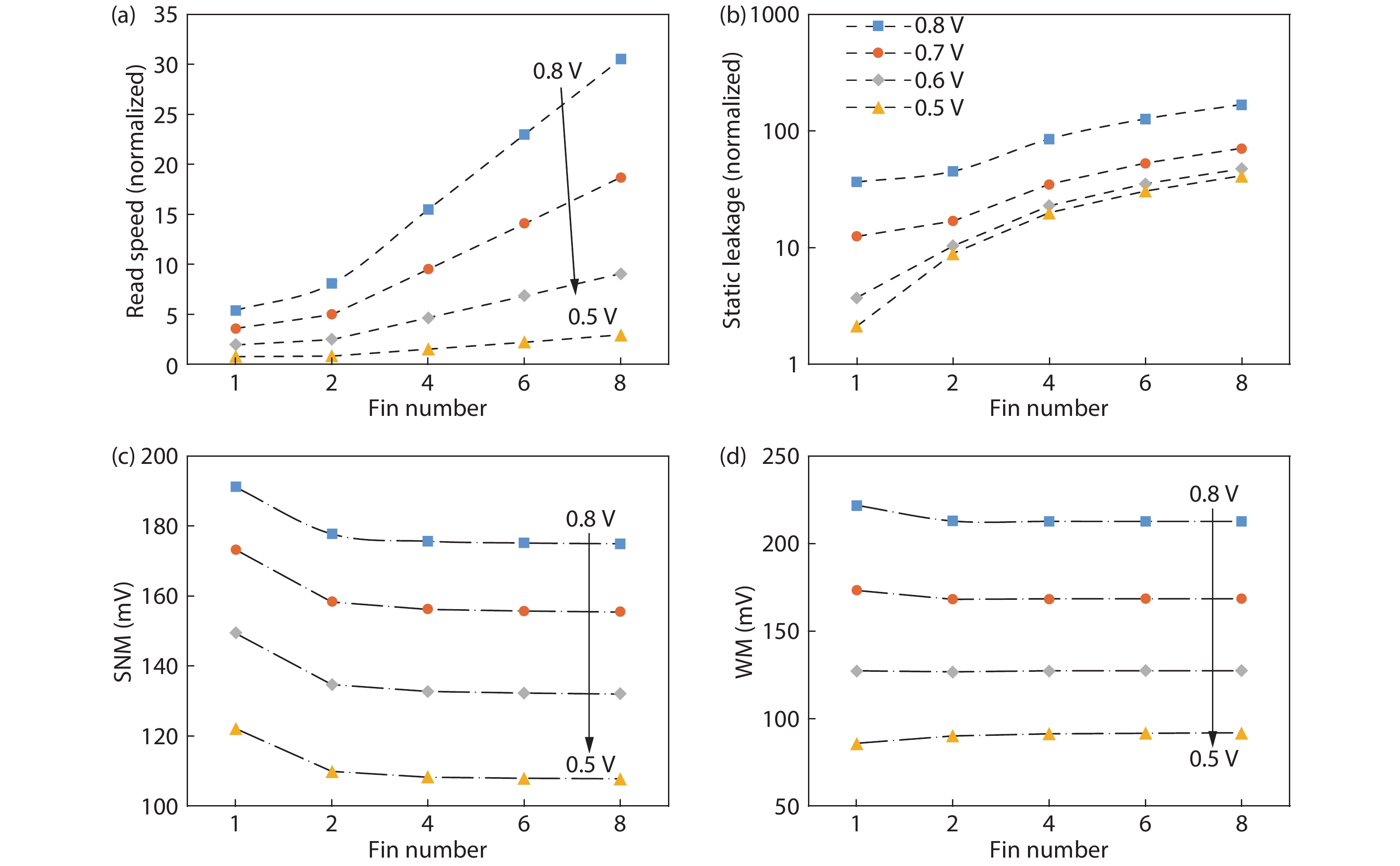

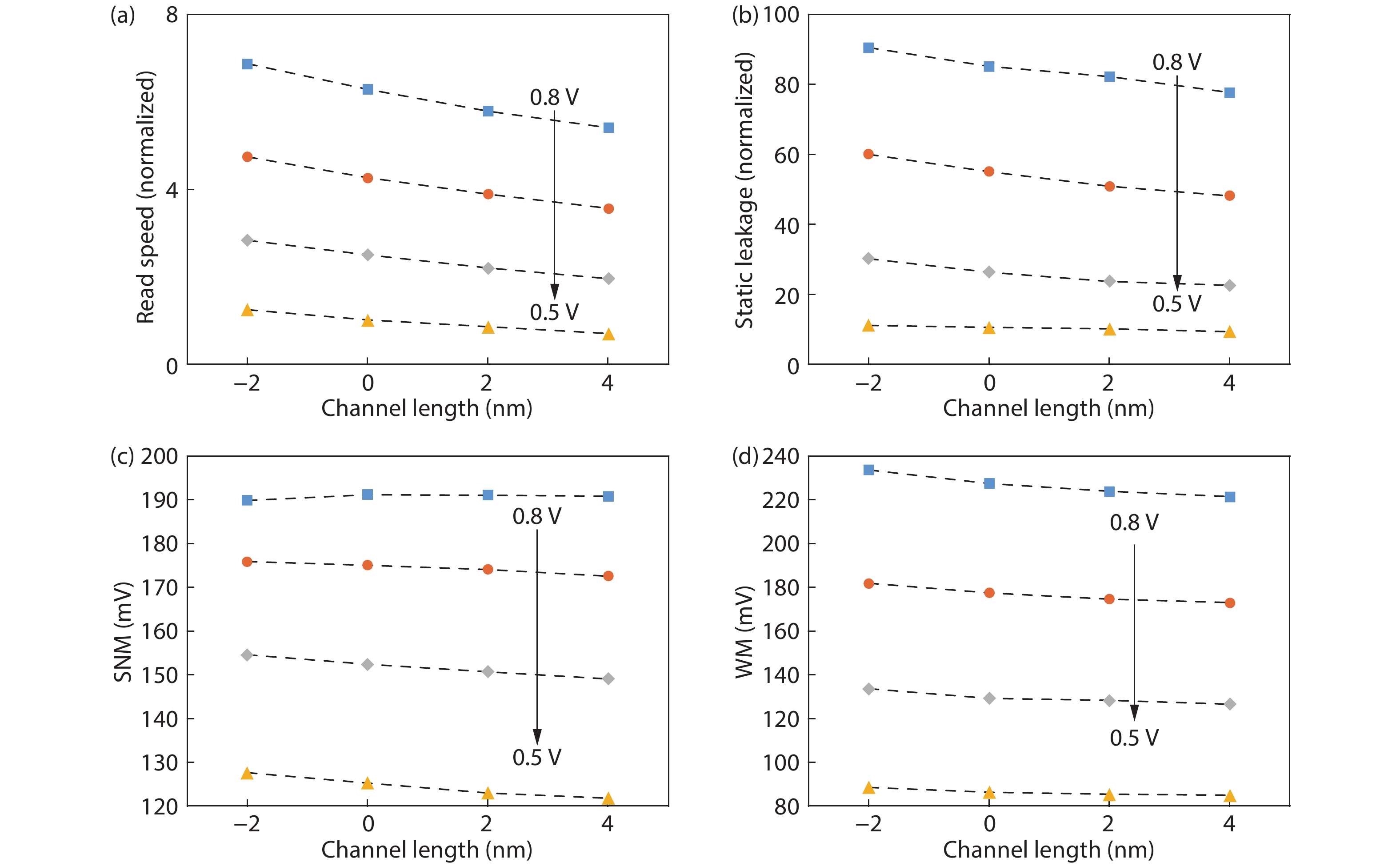

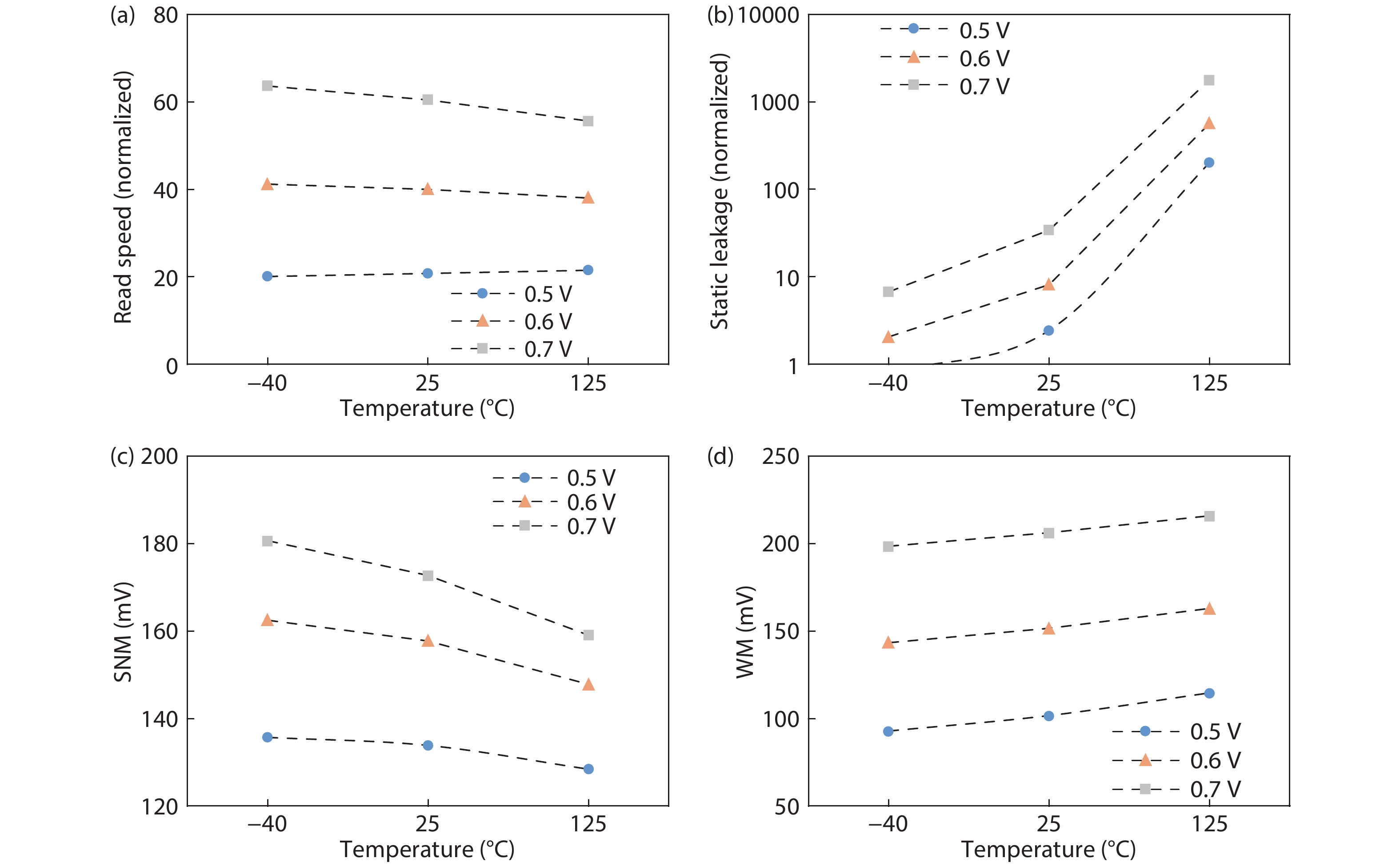

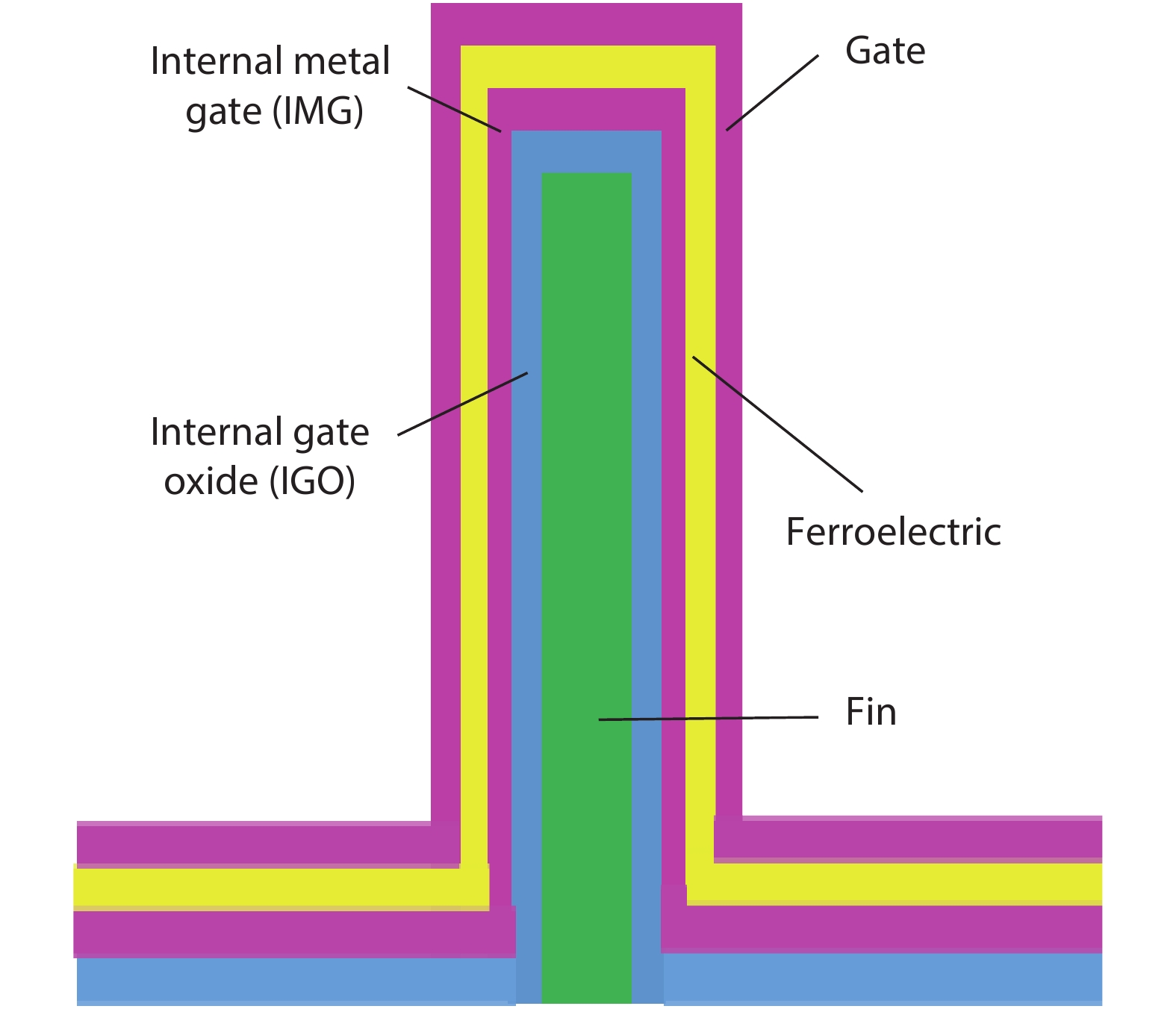

Negative capacitance FinFET (NC-FinFET) has a promising developmental prospect due to its superior performance in SS < 60 mV/dec (subthreshold swing), especially in SRAM. Noise margin is an important metric to evaluate the performance for SRAM, together with static leakage, read speed, etc. In this paper, we study the effects of the variation of ferroelectric material (thickness, polarization), FinFET critical physical parameters (fin number, channel length) and some ambient factors (working temperature, supply voltage) on the performance of NC-FinFET SRAM within the reasonable fluctuation tolerance range. The SRAM bit cell is analyzed with a basic 6T structure. The impact of fin number and channel length for NC-FinFET SRAM is different from that of conventional FinFETs. Additionally, the ferroelectric material and some other factors are assessed in detail. -

References

[1] Li K, Chen P, Lai T, et al. Sub-60mV-swing negative-capacitance FinFET without hysteresis. IEEE International Electron Devices Meeting (IEDM), 2015, 22[2] Lin C, Khan A I, Salahuddin S, et al. Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. IEEE Trans Electron Devices, 2016, 63(5), 21972199 doi: 10.1109/TED.2016.2514783[3] Khandelwal S, Khan A I, Duarte J P, et al. Circuit performance analysis of negative capacitance FinFETs. IEEE Symposium on VLSI Technology, 2016, 1[4] Ko E, Lee H, Goh Y, et al. Sub-60-mV/decade negative capacitance FinFET with sub-10-nm hafnium-based ferroelectric capacitor. IEEE J Electron Devices Soc, 2017, 5(5), 306309 doi: 10.1109/JEDS.2017.2731401[5] Ota H, Fukuda K, Ikegami T, et al. Perspective of negative capacitance FinFETs investigated by transient TCAD simulation. IEEE International Electron Devices Meeting (IEDM), 2017, 15[6] Khandelwal S, Duarte J P, Khan A I, et al. Impact of parasitic capacitance and ferroelectric parameters on negative capacitance FinFET characteristics. IEEE Electron Device Lett, 2017, 38(1), 142144 doi: 10.1109/LED.2016.2628349[7] Banga H, Agarwal D. Single bit-line 10T SRAM cell for low power and high SNM. International Conference on Recent Innovations in Signal processing and Embedded Systems (RISE), 2017, 433[8] Zhang G, Li Y, Yu S F. Techniques to improve read noise margin and write margin for bit-cell of 14 nm FINFET node. China Semiconductor Technology International Conference, 2015, 1[9] Chen K T, Gu S S, Lee M H. Ferroelectric HfZrO xFETs on SOI substrate with reverse-DIBL (drain-induced barrier lowering) and NDR (negative differential resistance). IEEE J Electron Devices Soc, 2018, 6, 900904 doi: 10.1109/JEDS.2018.2863283[10] Aziz A, Ghos S, Datta S, et al. Physics-based circuit compatible SPICE model for ferroelectric transistors. IEEE Electron Device Lett, 2016, 37(6), 805808 doi: 10.1109/LED.2016.2558149[11] Kumar V, Shrivatava R K, Padaliya M M. A temperature compensated read assist for low Vmin and high performance high density 6T SRAM in FinFET technology. 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), 2018, 447[12] Li Y, Yao K, Samudra G S. Delay and power evaluation of negative capacitance ferroelectric MOSFET based on SPICE model. IEEE Trans Electron Devices, 2017, 64(5), 24032408 doi: 10.1109/TED.2017.2674020[13] Dutta T, Pahwa G, Trivedi A R, et al. performance evaluation of 7-nm node negative capacitance FinFET-based SRAM. IEEE Electron Device Lett, 2017, 38(8), 1161 doi: 10.1109/LED.2017.2712365[14] Pahwa G, Dutta T, Agarwal A, et al. Analysis and compact modeling of negative capacitance transistor with high on-current and negative output differential resistance —Part I: model description. IEEE Trans Electron Devices, 2016, 63(12), 4981 doi: 10.1109/TED.2016.2614432[15] Pahwa G, Dutta T, Agarwal A, et al. Analysis and compact modeling of negative capacitance transistor with high on-current and negative output differential resistance—Part II: model validation. IEEE Trans Electron Devices, 2016, 63(12), 4986 doi: 10.1109/ted.2016.2614436[16] Dong Q, Ma Y N, Chen H, et al. A novel method for accurate measurement and decoupling of SRAM standby leakage. IEEE 11th International Conference on Solid-State and Integrated Circuit Technology, 2012, 1[17] Prasad G, Kusuma R. Statistical (M-C) and static noise margin analysis of the SRAM cells. Students Conference on Engineering and Systems (SCES), 2013, 1 -

Proportional views

DownLoad:

DownLoad: