| Citation: |

Yutong Ying, Fujiang Lin, Xuefei Bai. Design and analysis of an energy-efficient O-QPSK coherent IR-UWB transceiver with a 0.52° RMS phase-noise fractional synthesizer[J]. Journal of Semiconductors, 2018, 39(3): 035003. doi: 10.1088/1674-4926/39/3/035003

****

Y T Ying, F J Lin, X F Bai. Design and analysis of an energy-efficient O-QPSK coherent IR-UWB transceiver with a 0.52° RMS phase-noise fractional synthesizer[J]. J. Semicond., 2018, 39(3): 035003. doi: 10.1088/1674-4926/39/3/035003.

|

Design and analysis of an energy-efficient O-QPSK coherent IR-UWB transceiver with a 0.52° RMS phase-noise fractional synthesizer

DOI: 10.1088/1674-4926/39/3/035003

More Information

-

Abstract

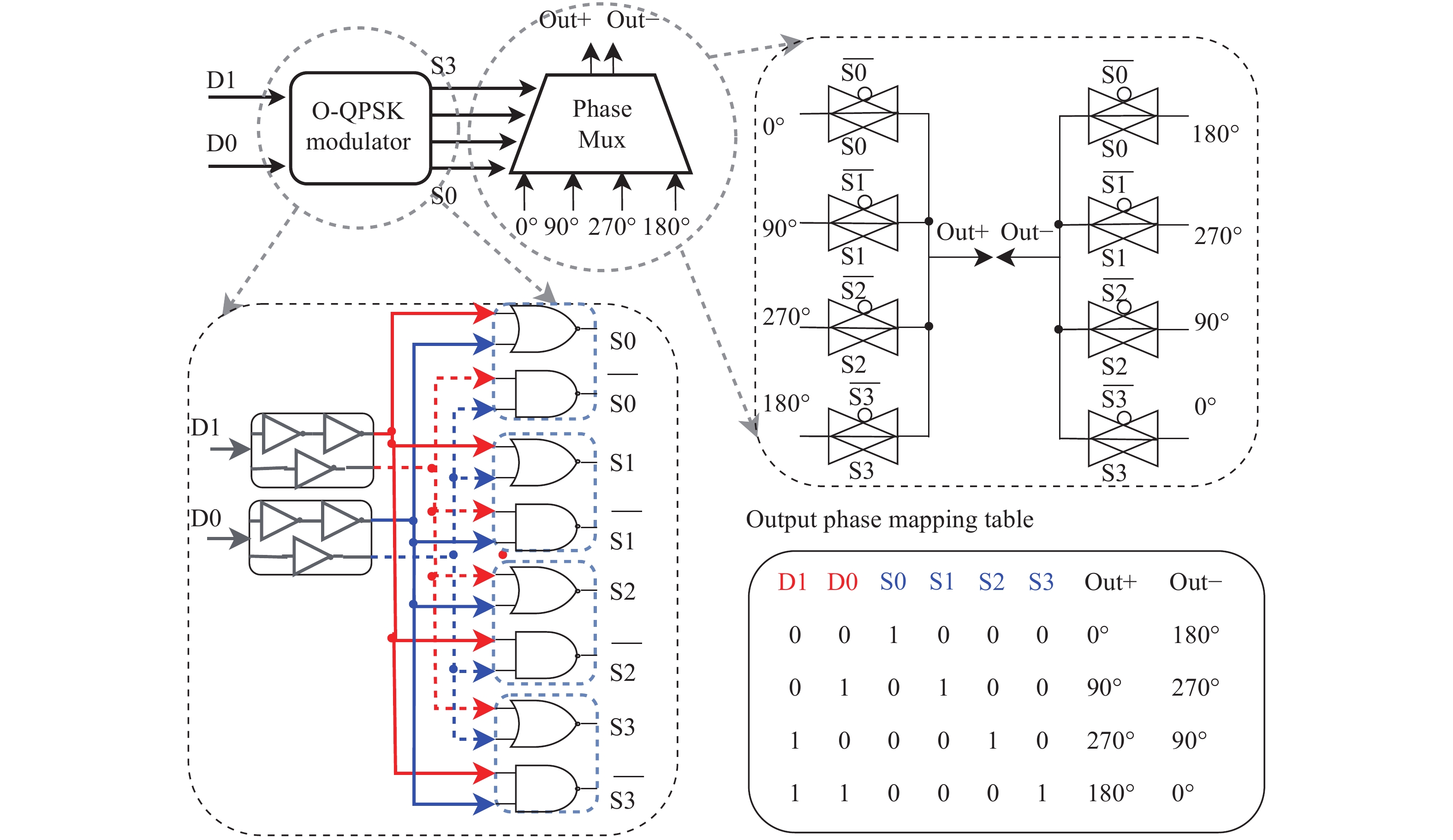

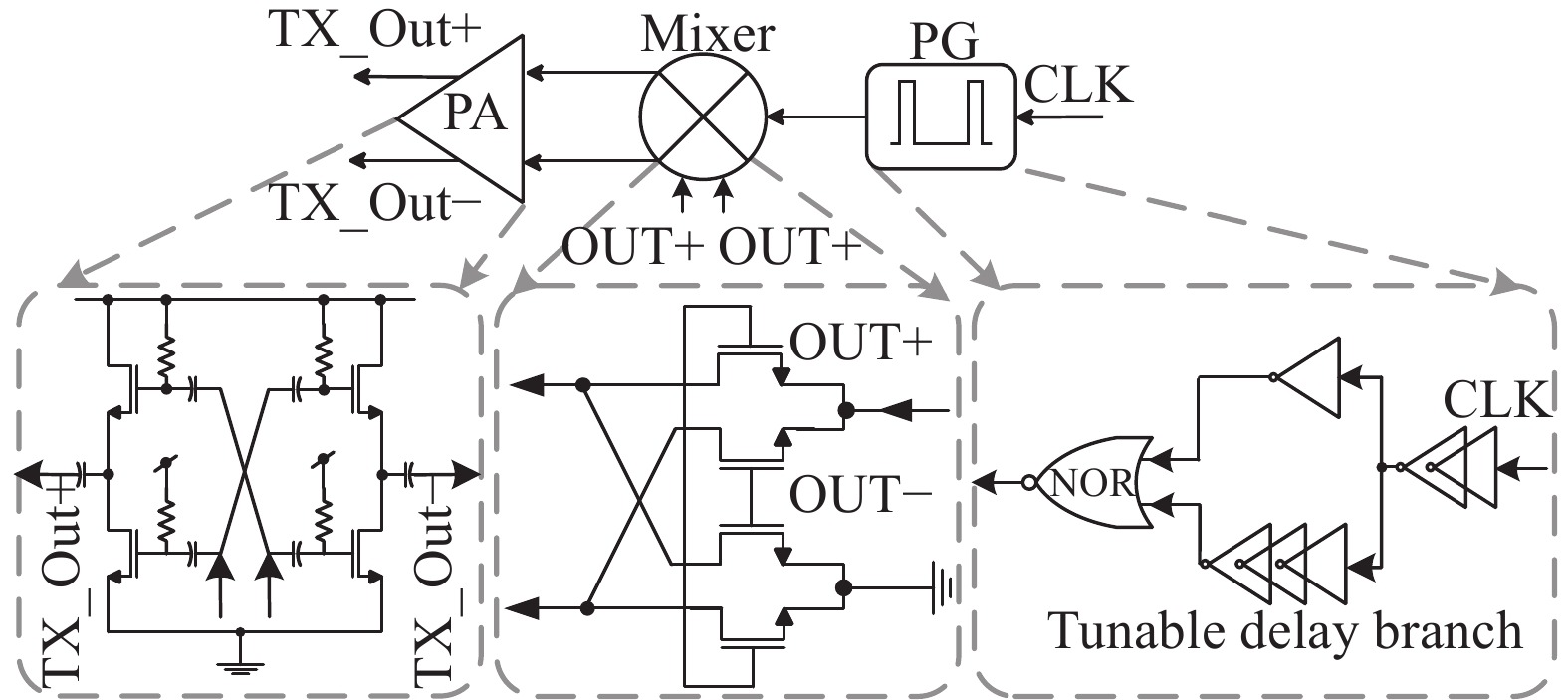

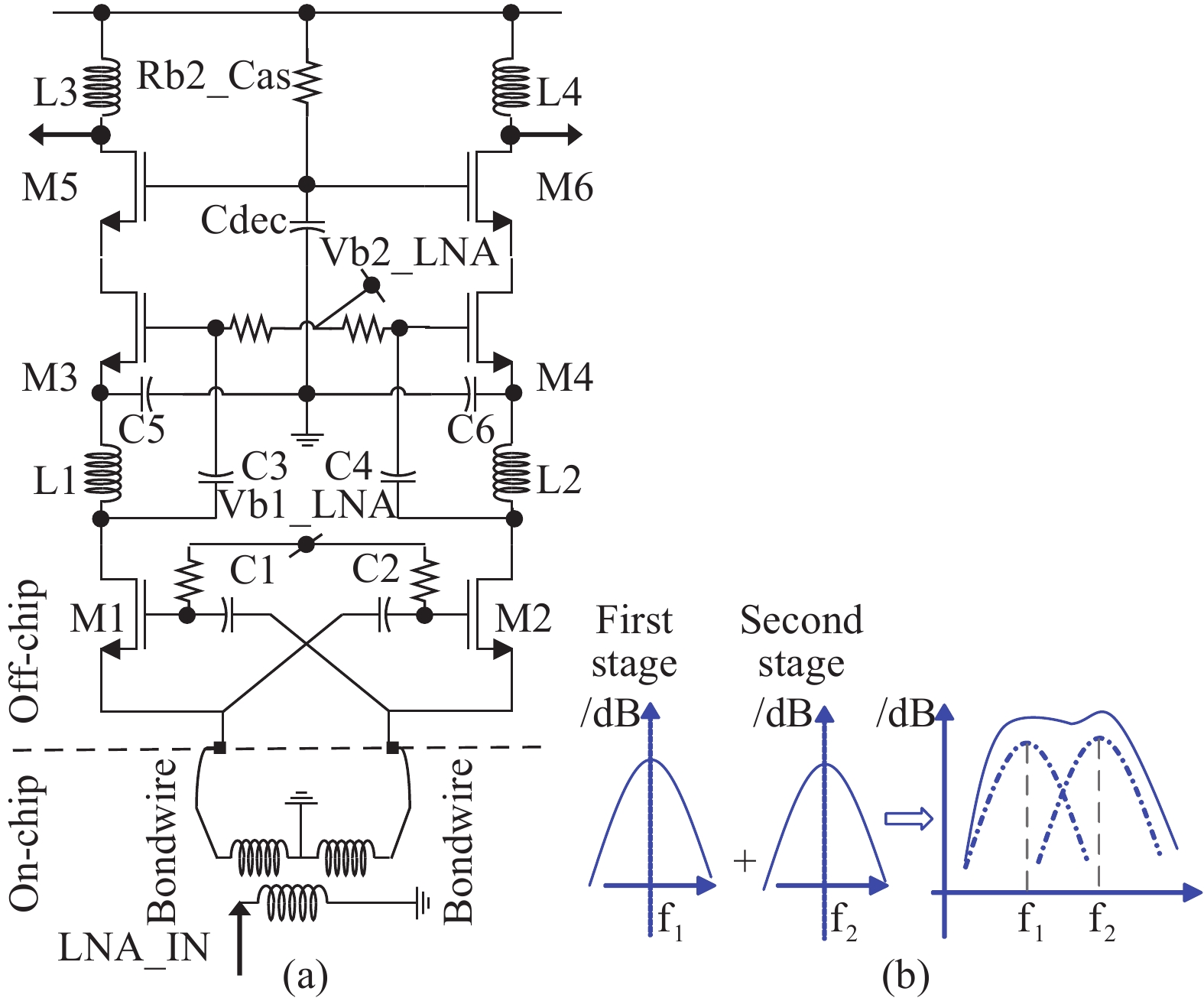

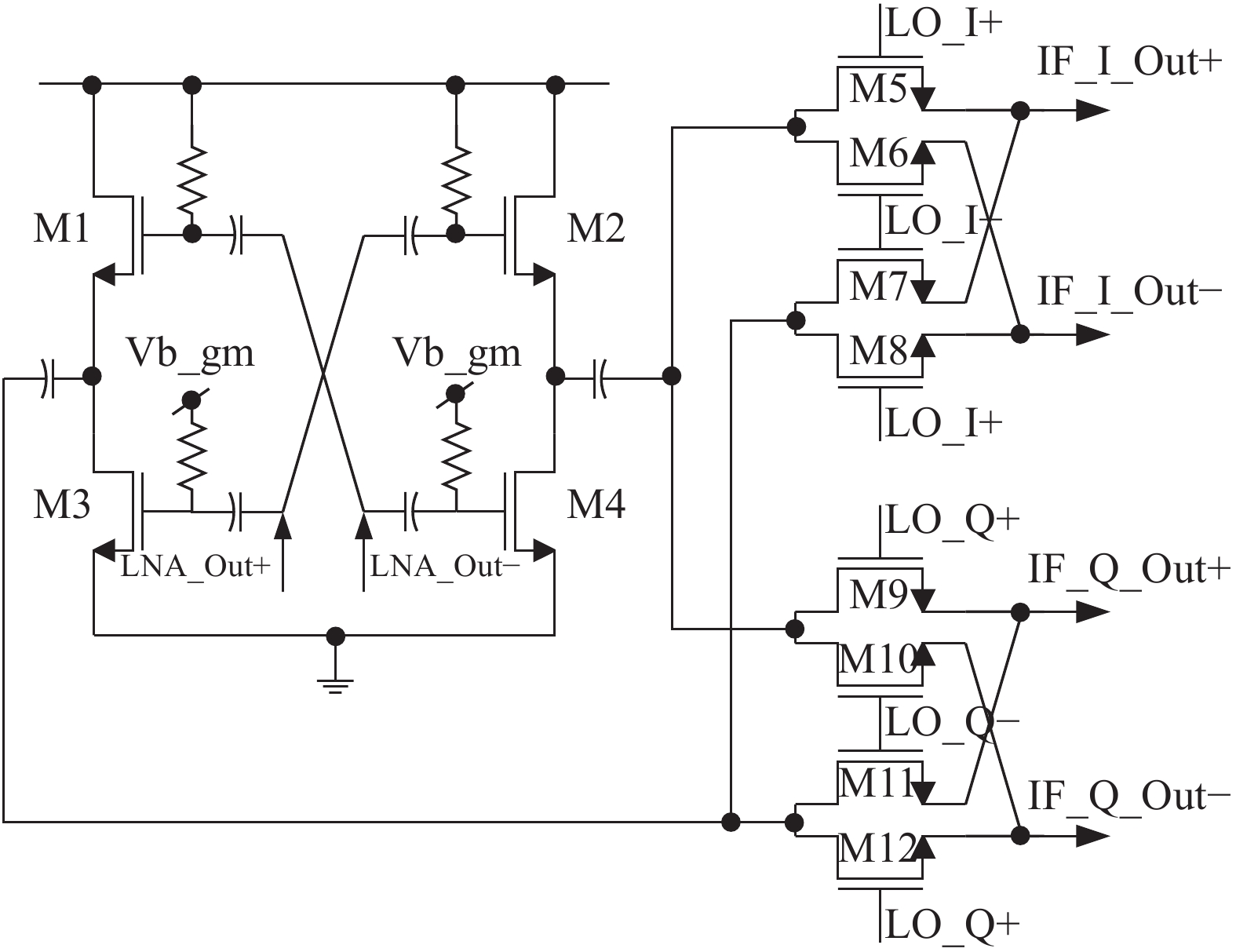

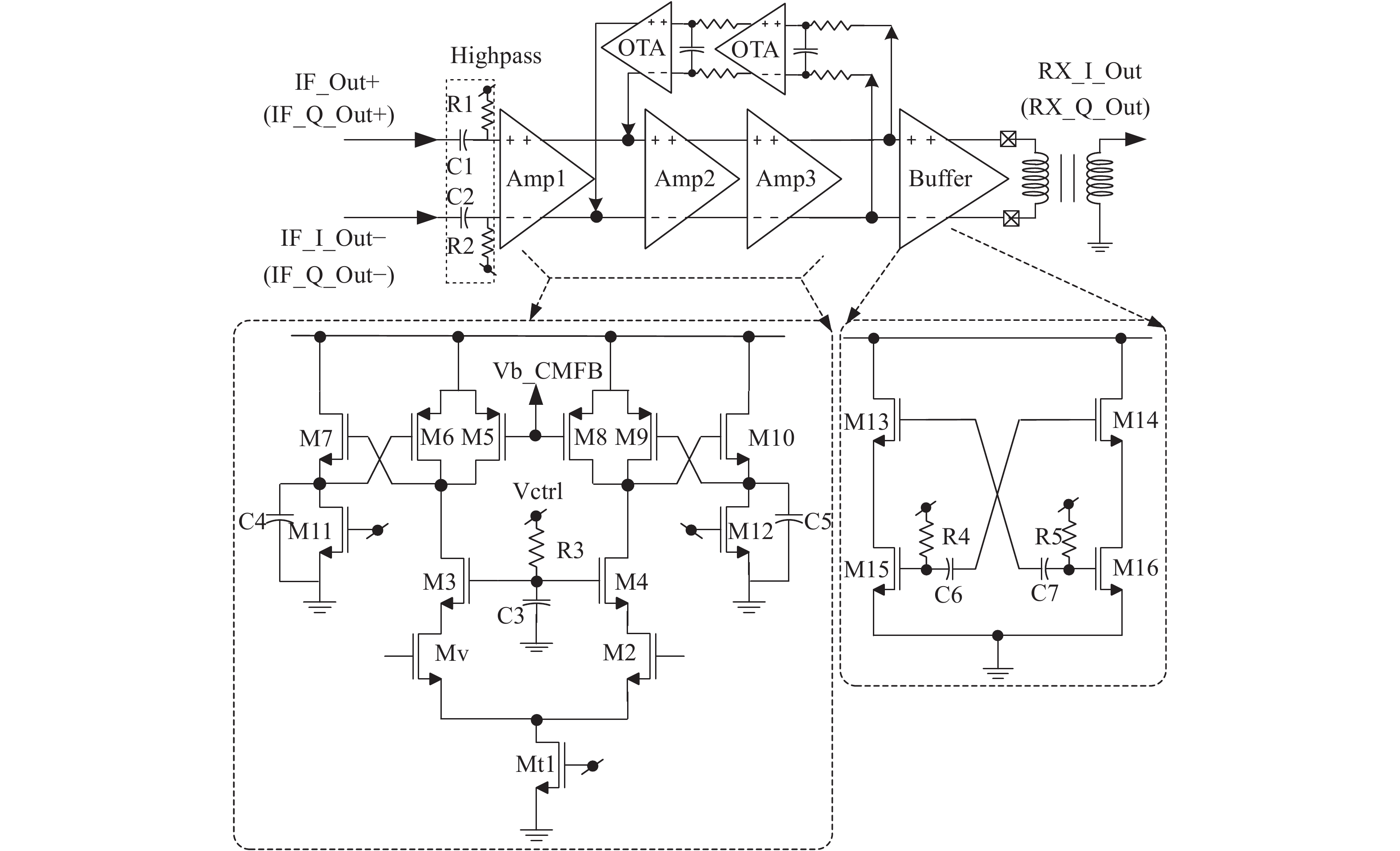

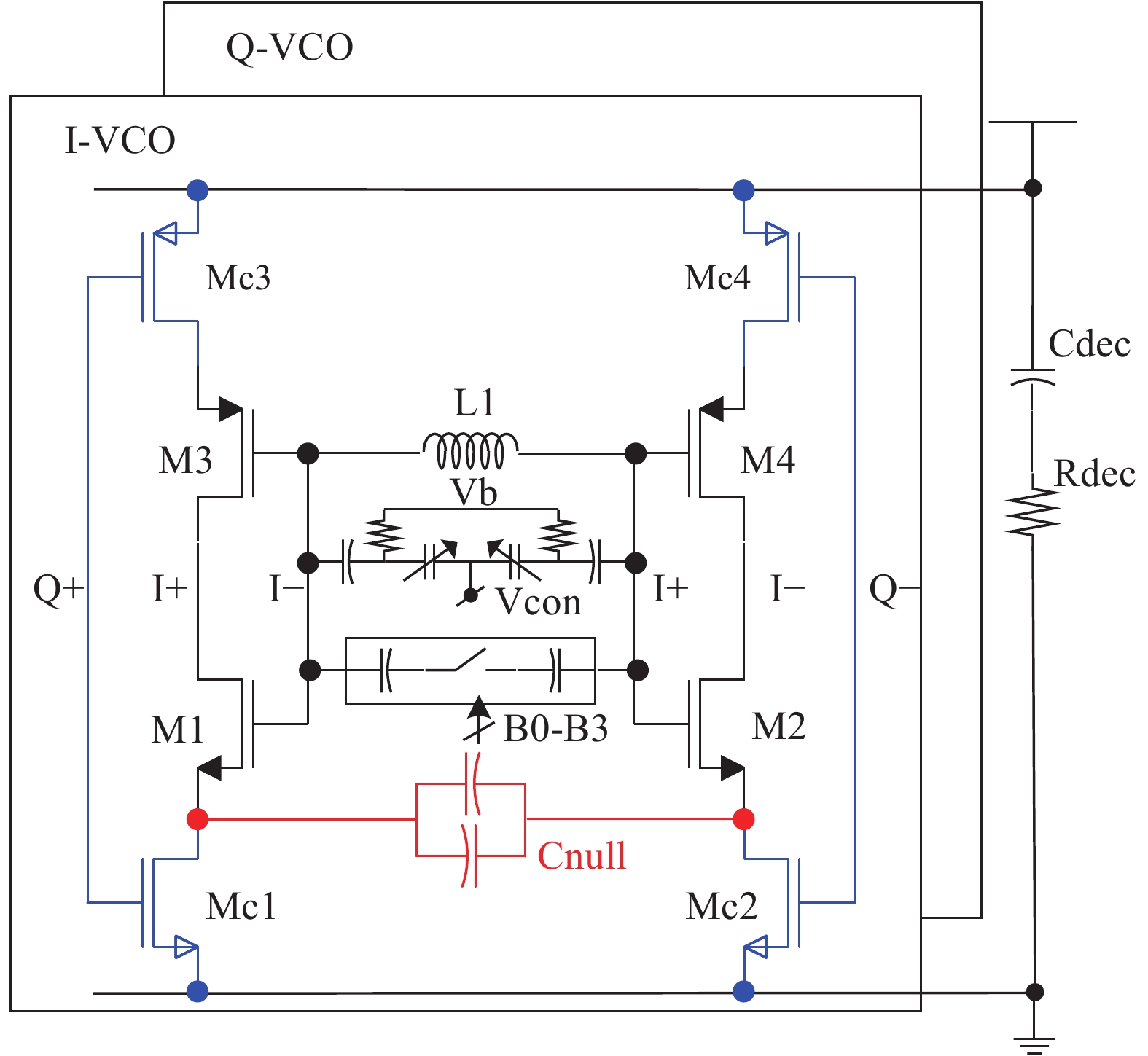

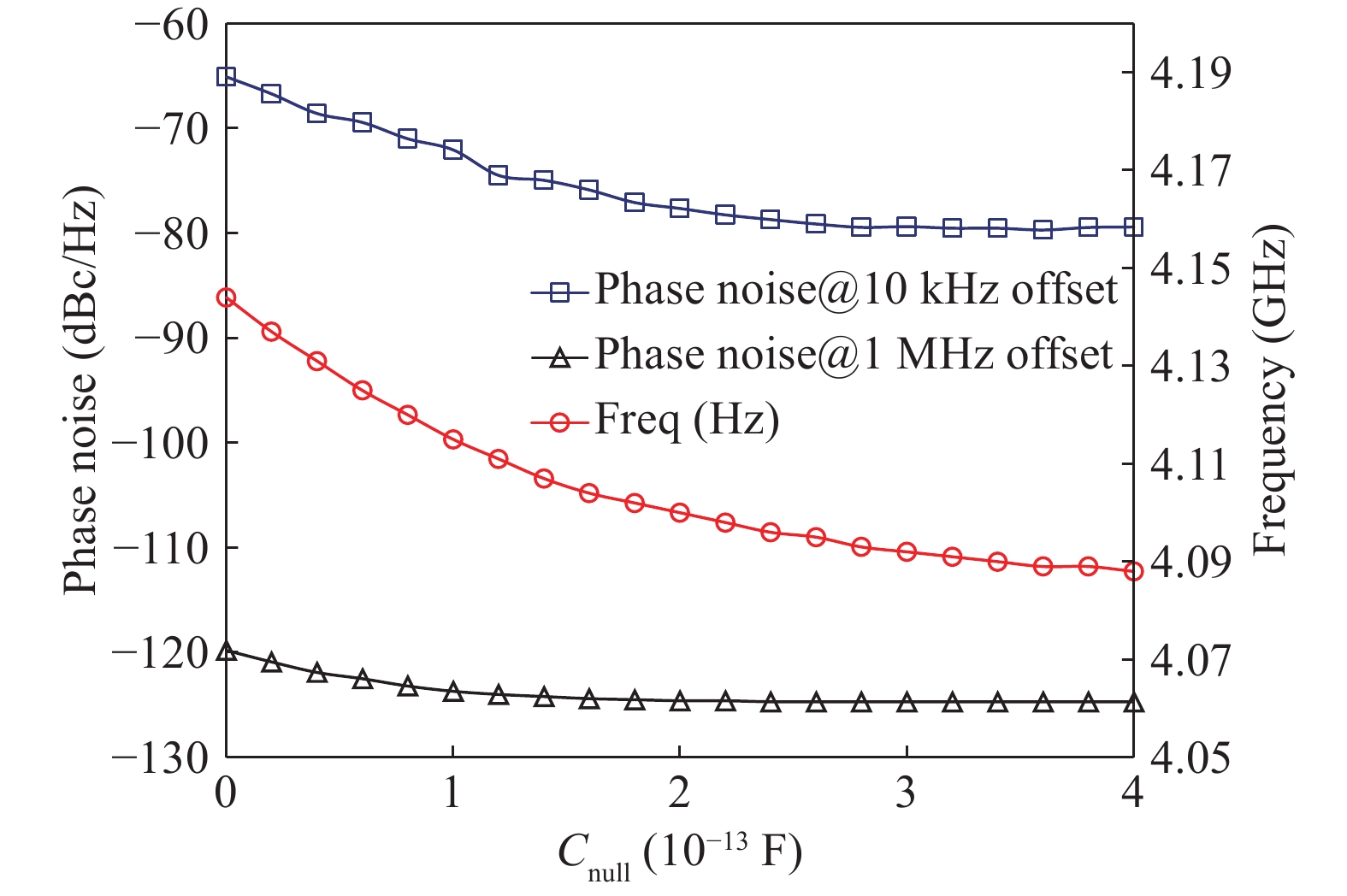

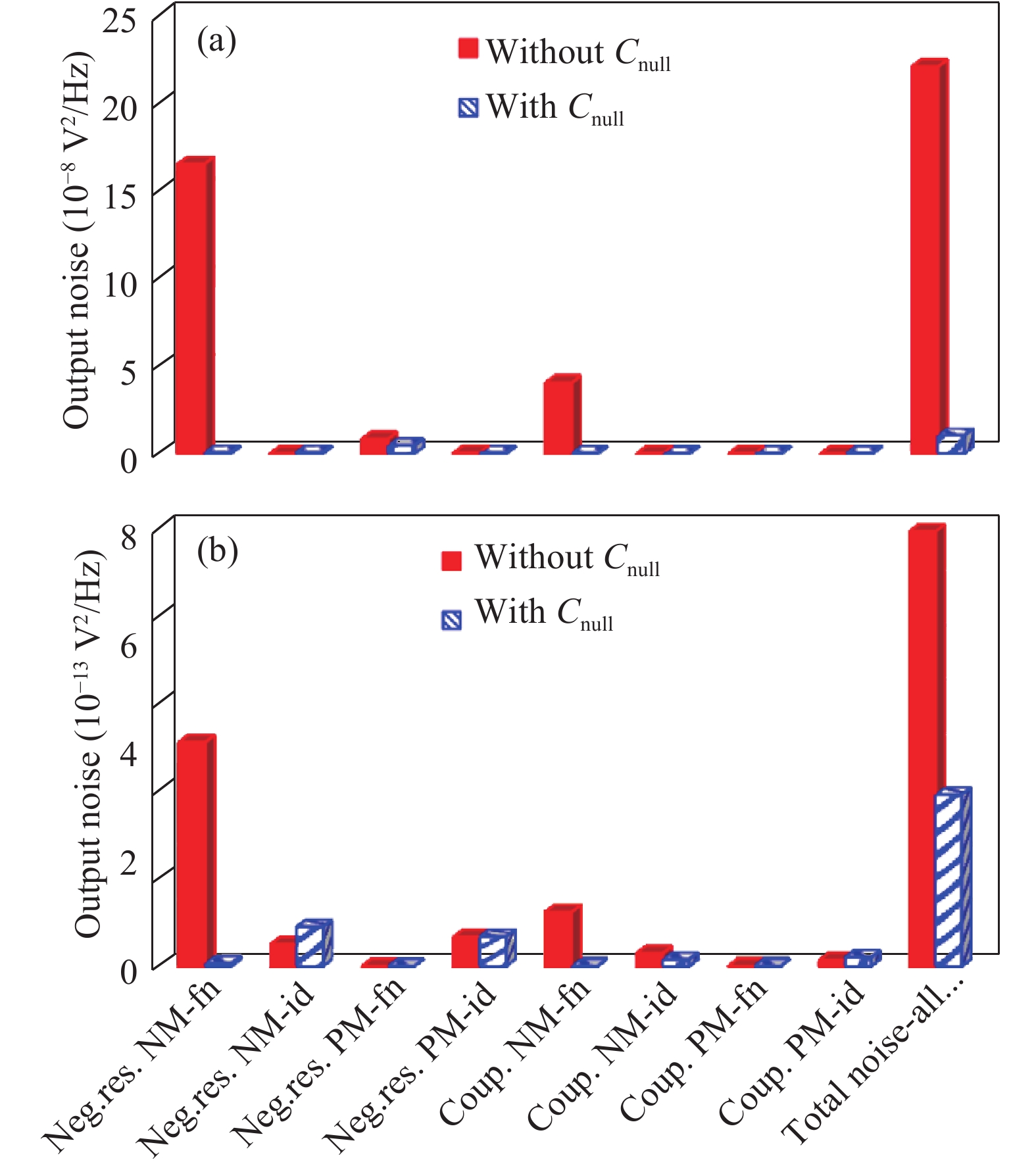

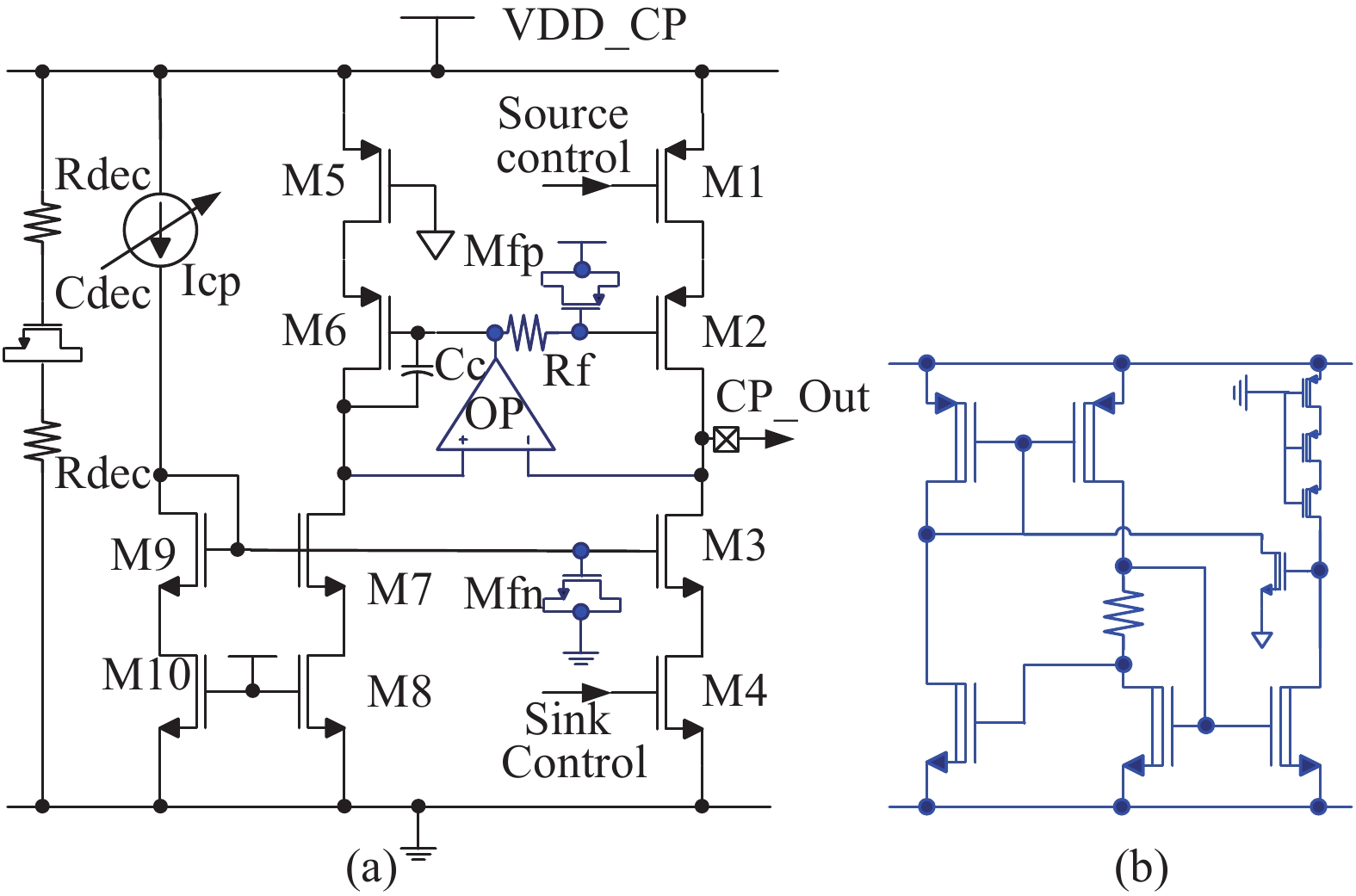

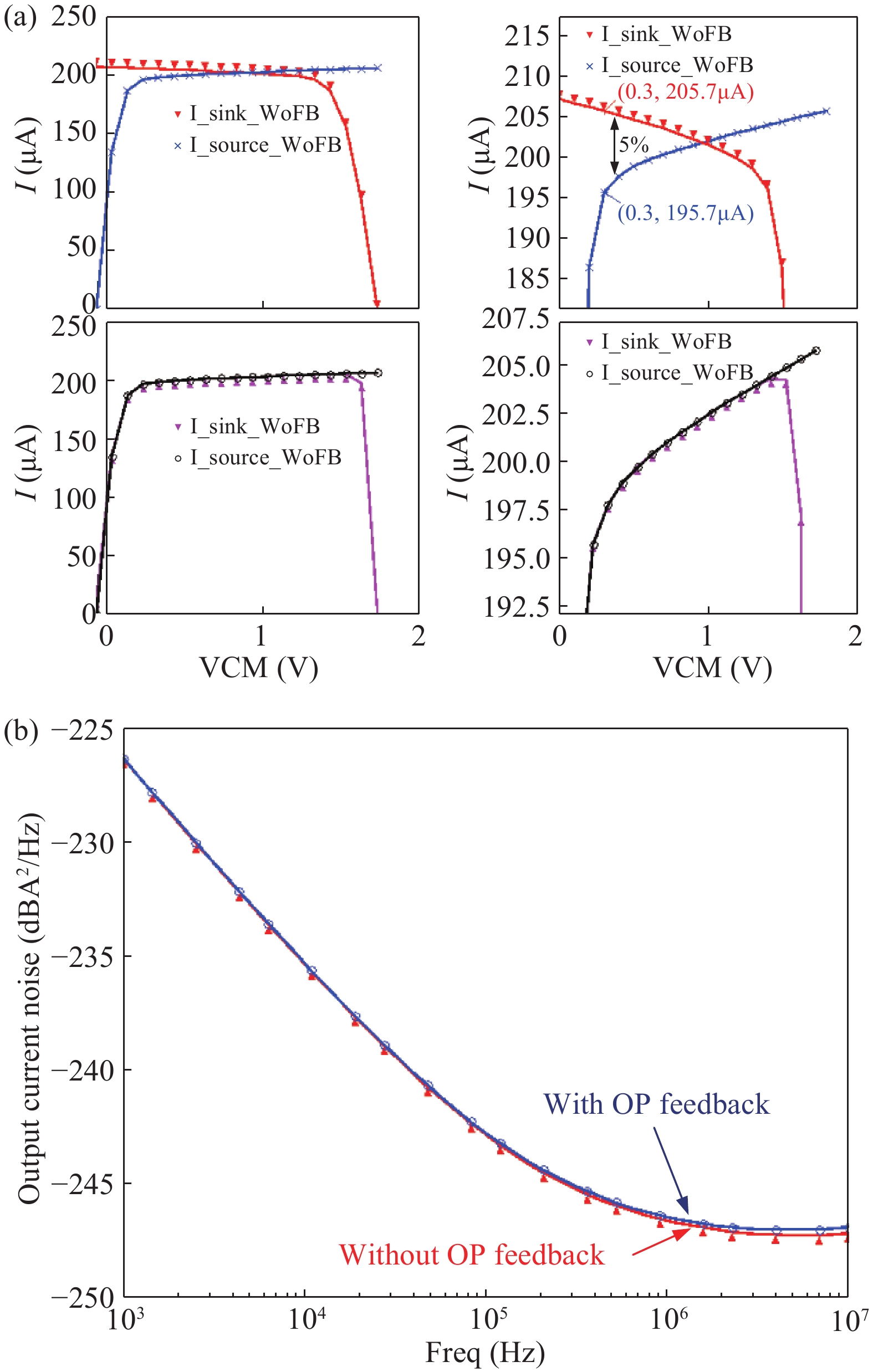

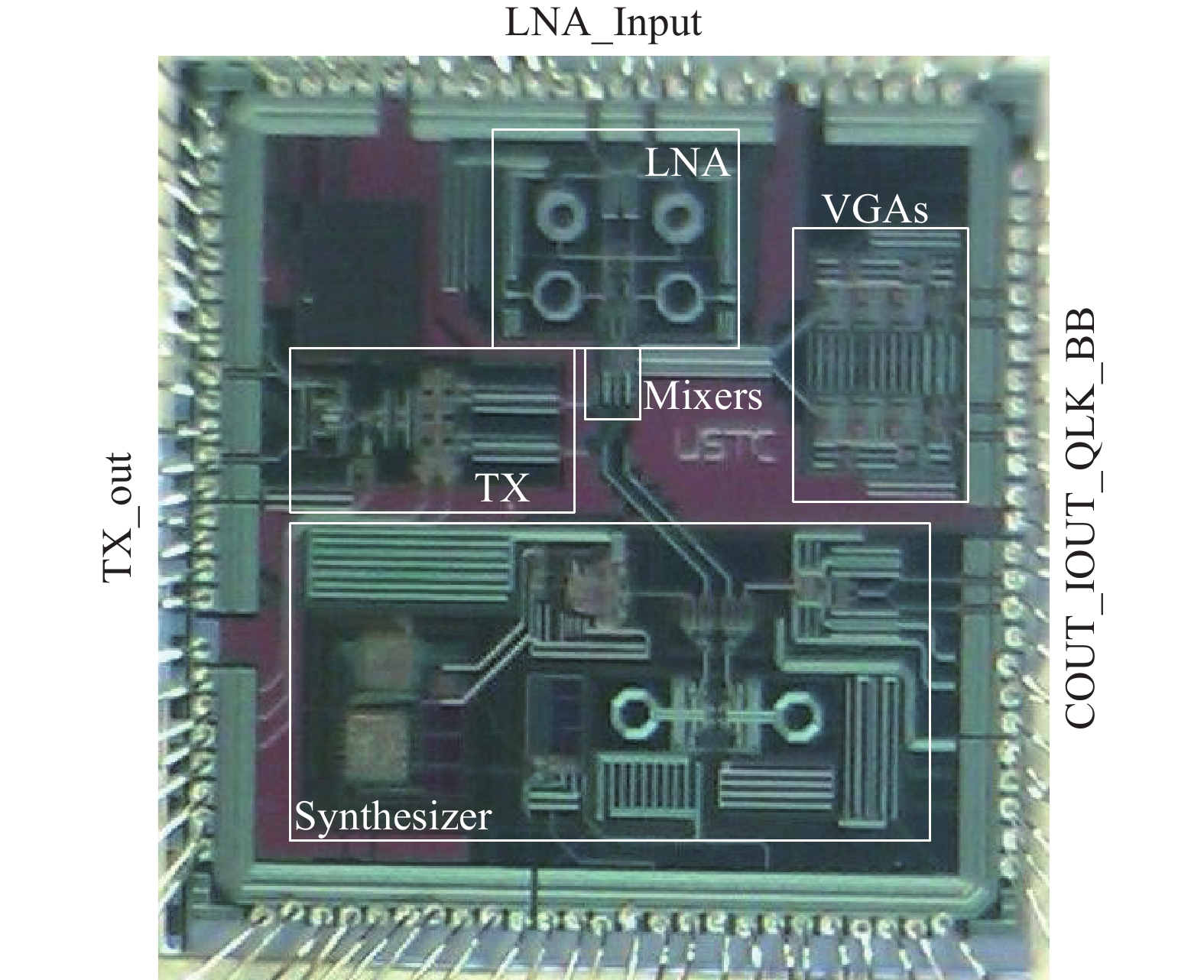

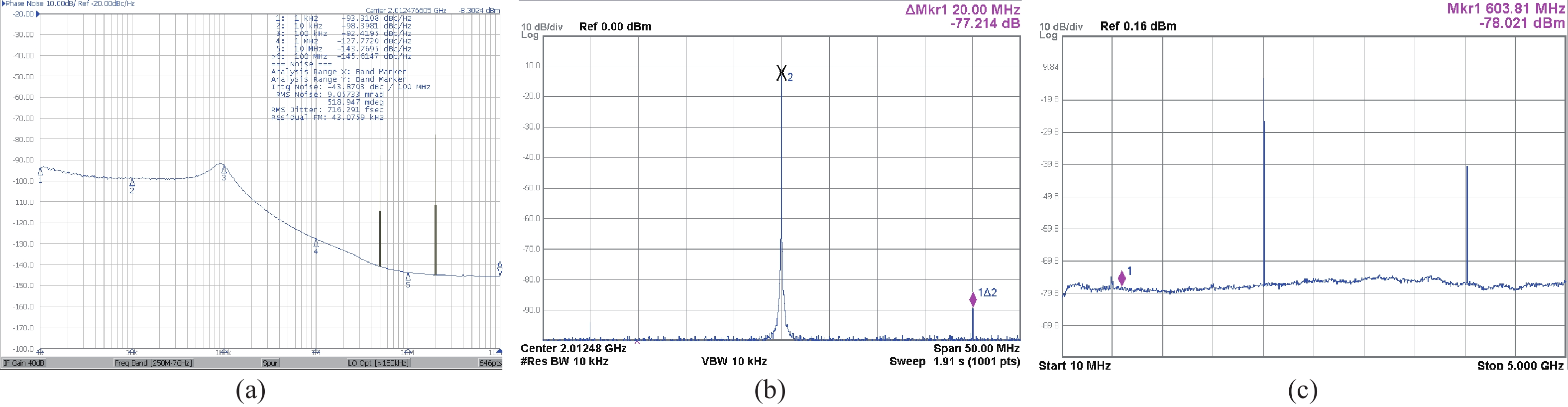

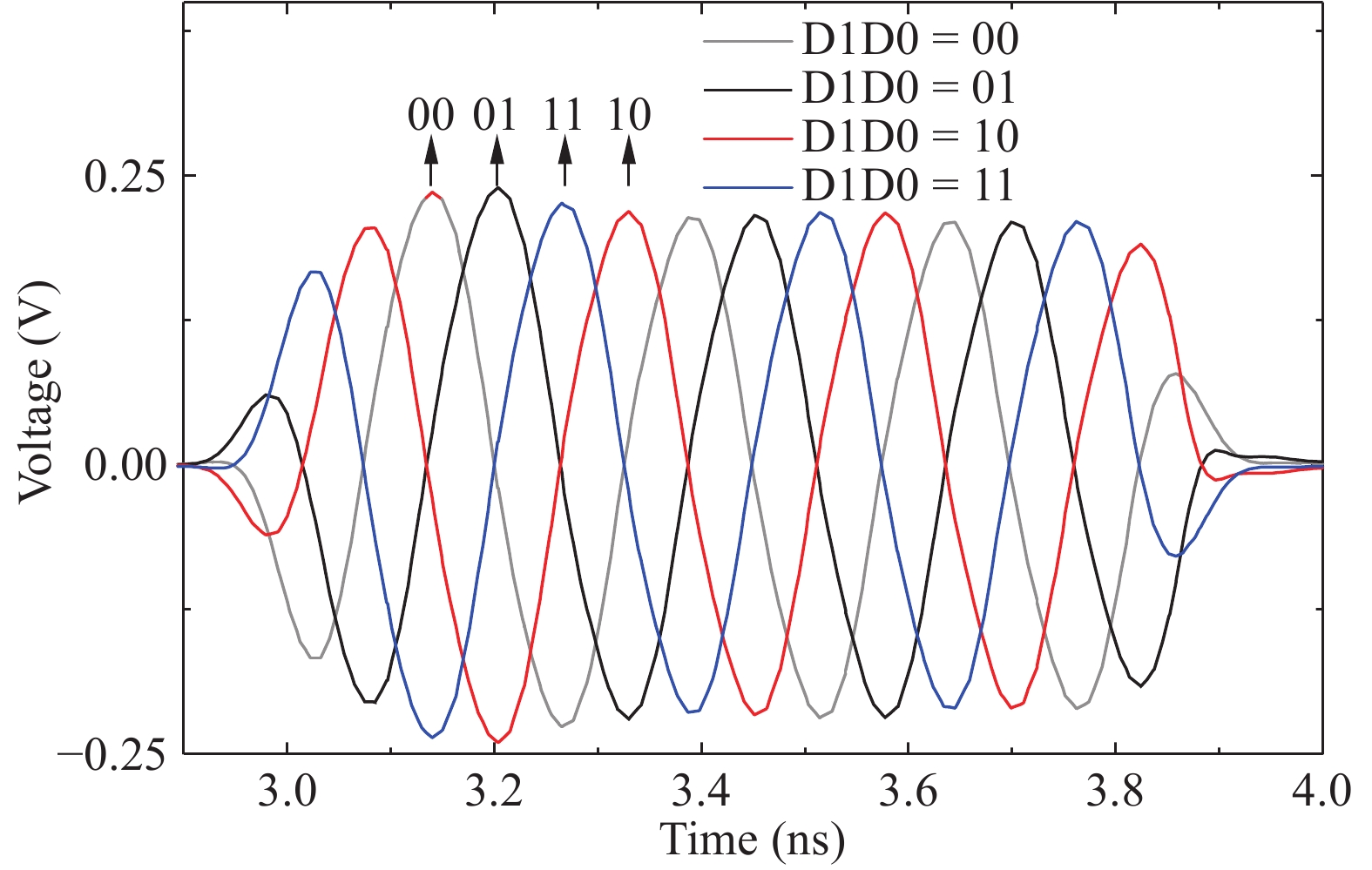

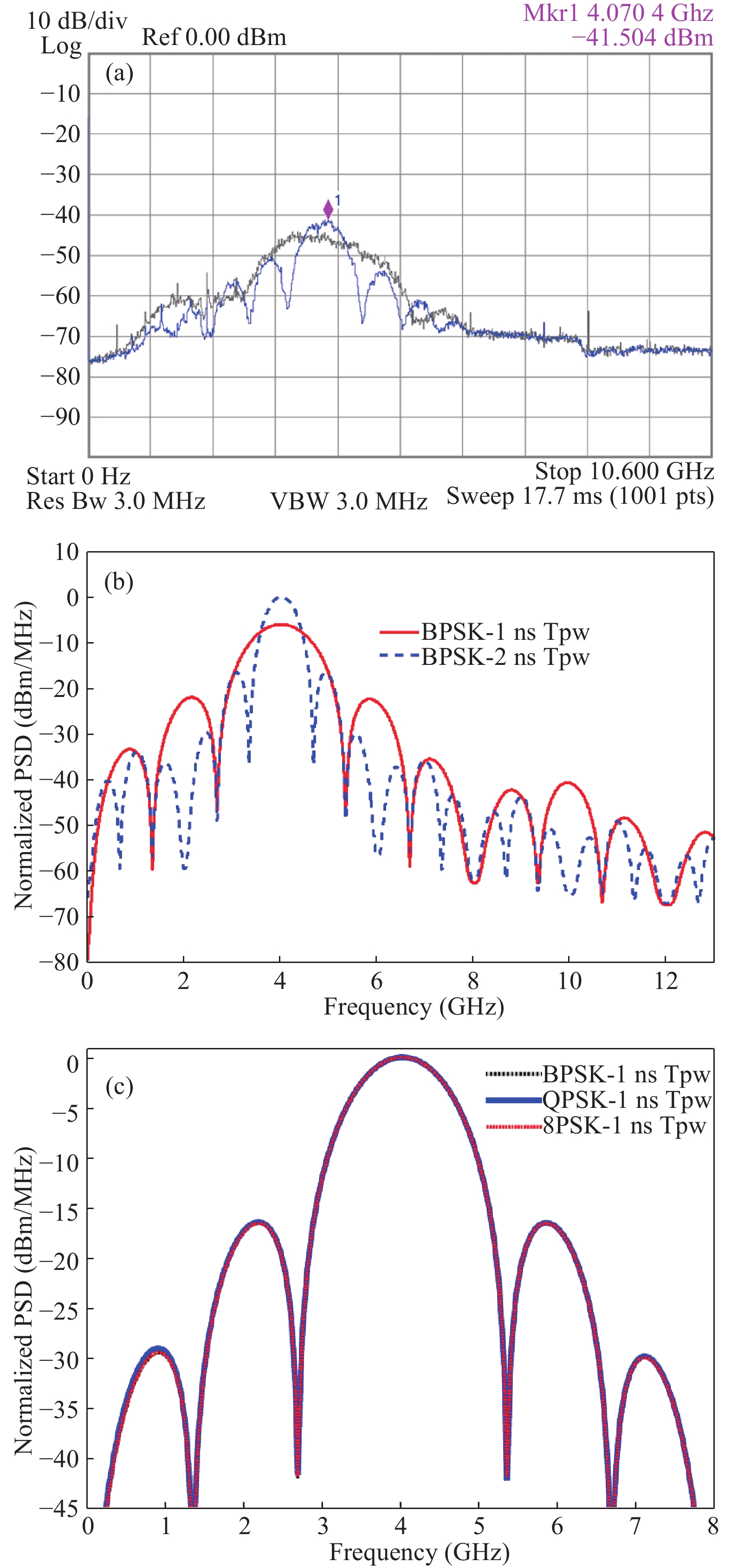

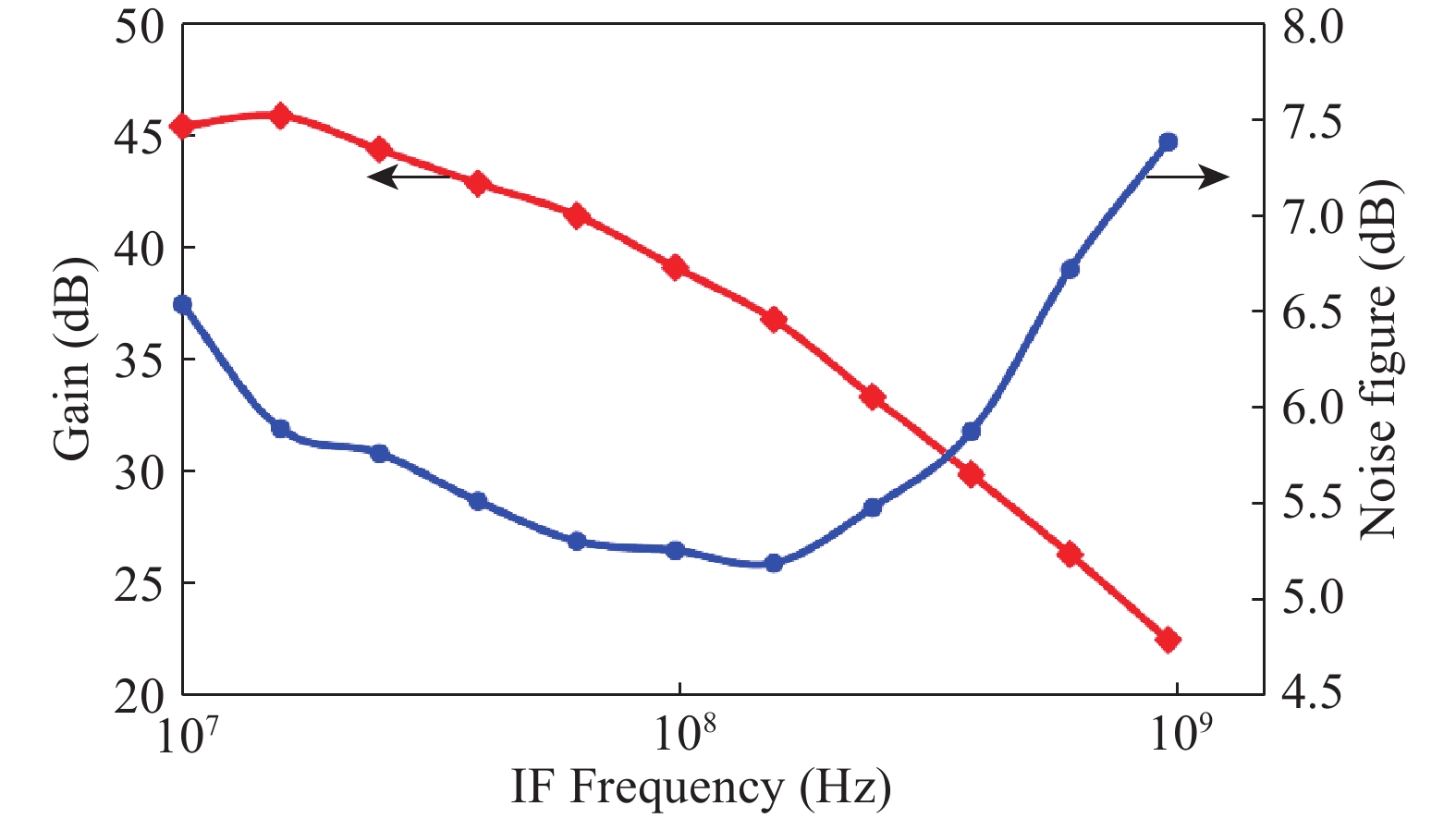

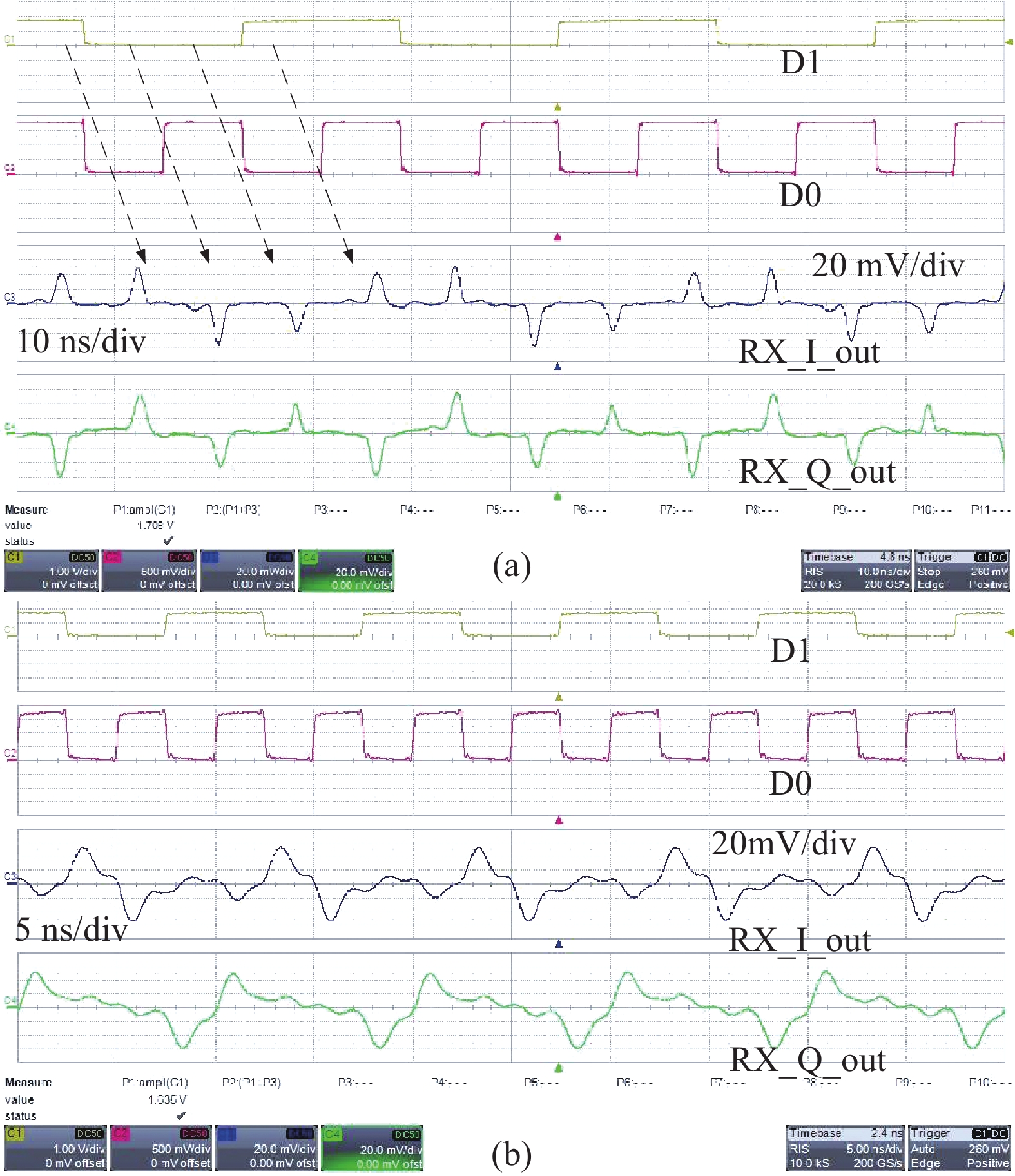

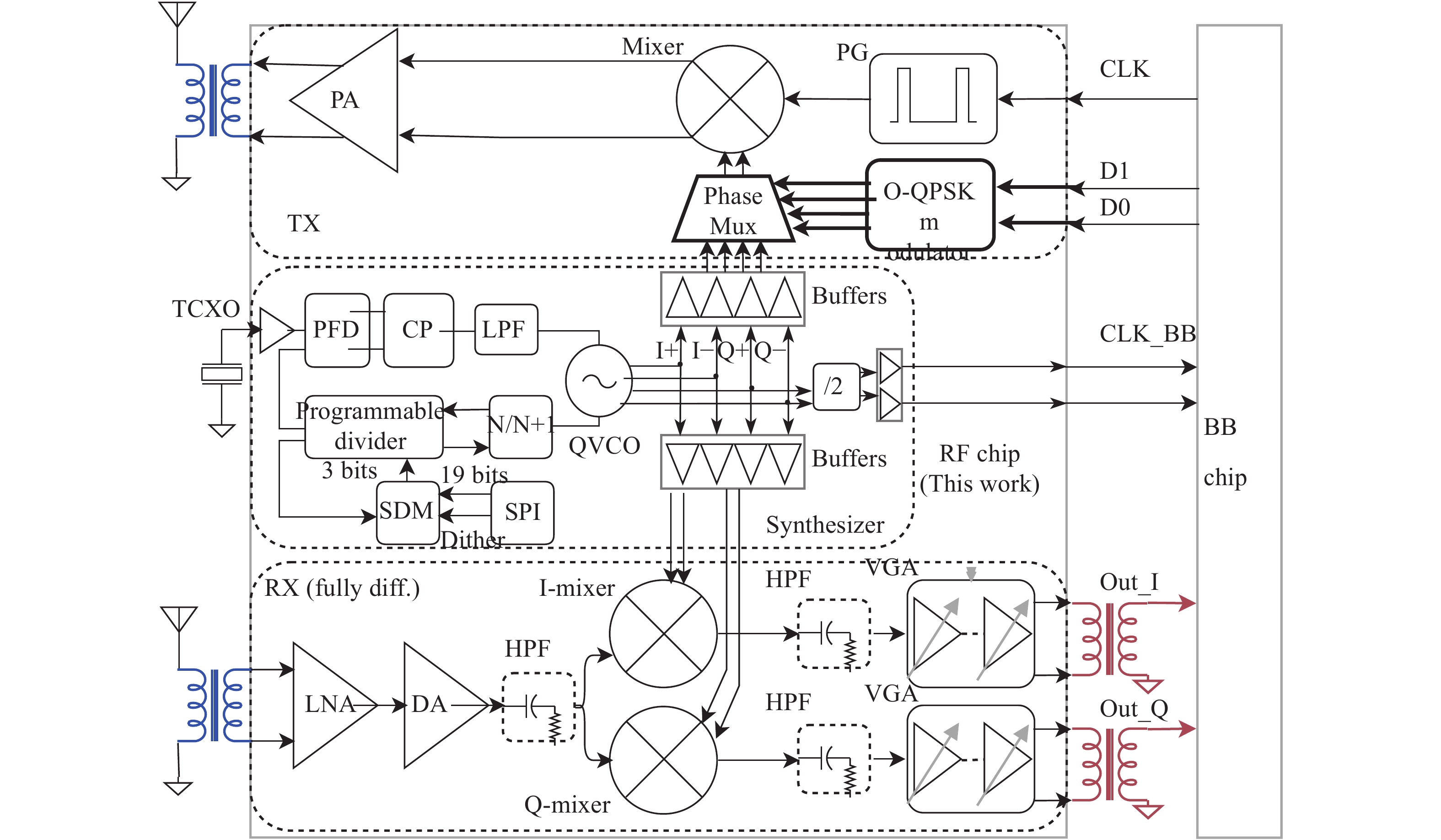

This paper explores an energy-efficient pulsed ultra-wideband (UWB) radio-frequency (RF) front-end chip fabricated in 0.18-μm CMOS technology, including a transmitter, receiver, and fractional synthesizer. The transmitter adopts a digital offset quadrature phase-shift keying (O-QPSK) modulator and passive direct-phase multiplexing technology, which are energy- and hardware-efficient, to enhance the data rate for a given spectrum. A passive mixer and a capacitor cross-coupled (CCC) source-follower driving amplifier (DA) are also designed for the transmitter to further reduce the low power consumption. For the receiver, a power-aware low-noise amplifier (LNA) and a quadrature mixer are applied. The LNA adopts a CCC boost common-gate amplifier as the input stage, and its current is reused for the second stage to save power. The mixer uses a shared amplification stage for the following passive IQ mixer. Phase noise suppression of the phase-locked loop (PLL) is achieved by utilizing an even-harmonics-nulled series-coupled quadrature oscillator (QVCO) and an in-band noise-aware charge pump (CP) design. The transceiver achieves a measured data rate of 0.8 Gbps with power consumption of 16 mW and 31.5 mW for the transmitter and the receiver, respectively. The optimized integrated phase noise of the PLL is 0.52° at 4.025 GHz.-

Keywords:

- IR-UWB,

- O-QPSK modulation,

- phase multiplexing,

- transmitter,

- receiver,

- fractional PLL

-

References

[1] IEEE Std., IEEE802.11ad http://standards.ieee.org/ develop/project/802.11ad.html[2] Steve LO, Sever I, Ssu-Pin P J, et al. A dual-antenna phased-array UWB transceiver in 0.18 μm CMOS. IEEE J Solid-State Circuits, 2006, 41(12): 2776 doi: 10.1109/JSSC.2006.884803[3] Werther O, Cavin M, Schneider A, et al. A fully integrated 14 band, 3.1 to 10.6 GHz 0.13 μm SiGe BiCMOS UWB RF transceiver. IEEE J Solid-State Circuits, 2008, 43(12): 2829 doi: 10.1109/JSSC.2008.2005744[4] Sandner C, Derksen S, Draxelmayr D, et al. A wimedia/mboa-compliant cmos rf transceiver for uwb. IEEE J Solid-State Circuits, 2006, 41(12): 2787 doi: 10.1109/JSSC.2006.884804[5] Leenaerts D, van de Beek R, Bergervoet J, et al. A 65 nm CMOS inductorless triple band group WiMedia UWB PHY. IEEE J Solid-State Circuits, 2009, 44(12): 3499 doi: 10.1109/JSSC.2009.2032588[6] Diao S, Zheng Y, Heng C H. A CMOS ultra low-power and highly efficient UWB-IR transmitter for WPAN applications. IEEE Trans Circuits Syst II, 2009, 56(3): 200 doi: 10.1109/TCSII.2009.2015369[7] Crepaldi M, Li C, Fernandes J R, et al. An ultra-wideband impulse-radio transceiver chipset using synchronized-OOK modulation. IEEE J Solid-State Circuits, 2011, 46(10): 2284 doi: 10.1109/JSSC.2011.2161214[8] Mercier P P, Daly D C, Chandrakasan A P. An energy-efficient all-digital UWB transmitter employing dual capacitively-coupled pulse-shaping drivers. IEEE J Solid-State Circuits, 2009, 44(6): 1679 doi: 10.1109/JSSC.2009.2020466[9] Smaini L, Tinella C, Hélal D, et al. Single-chip CMOS pulse generator for UWB systems. IEEE J Solid-State Circuits, 2006, 41(7): 1551 doi: 10.1109/JSSC.2006.873896[10] Xia L, Shao K, Chen H, et al. 0.15-nJ/b 3–5-GHz IR-UWB system with spectrum tunable transmitter and merged-correlator noncoherent receiver. IEEE Trans Microwave Theory Tech, 2011, 59(4): 1147 doi: 10.1109/TMTT.2011.2114193[11] Wentzloff D D, Chandrakasan A P. A 47pJ/pulse 3.1 to 5 GHz all-digital UWB transmitter in 90 nm CMOS. IEEE Solid-State Circuits Conference (ISSCC), 2007: 118[12] Zhou L, Chen Z, Wang C C, et al. A 2-Gb/s 130-nm CMOS RF-correlation-based IR-UWB transceiver front-end. IEEE Trans Microwave Theory Tech, 2011, 59(4): 1117 doi: 10.1109/TMTT.2011.2114190[13] Geng S, Liu D, Li Y, et al. A 13.3 mW 500 Mb/s IR-UWB transceiver with link margin enhancement technique for meter-range communications. IEEE J Solid-State Circuits, 2015, 50(3): 669 doi: 10.1109/JSSC.2015.2393815[14] Demirkan M, Spencer R R. A pulse-based ultra-wideband transmitter in 90-nm CMOS for WPANs. IEEE J Solid-State Circuits, 2008, 43(12): 2820 doi: 10.1109/JSSC.2008.2005703[15] Verhelst M, Dehaene W. System design of an ultra-low power, low data rate, pulsed UWB receiver in the 0–960 MHz band. IEEE International Conference on Communications (ICC), 2005(4): 2812[16] Ryckaert J, Verhelst M, Badaroglu M, et al. A CMOS ultra-wideband receiver for low data-rate communication. IEEE J Solid-State Circuits, 2007, 42(11): 2515 doi: 10.1109/JSSC.2007.907195[17] Yin H, Wang Z, Ke L, et al. Monobit digital receivers: design, performance, and application to impulse radio. IEEE Trans Commun, 2010, 58(6): 1695 doi: 10.1109/TCOMM.2010.06.080446[18] Singh J, Ponnuru S, Madhow U. Multi-gigabit communication: the ADC bottleneck. IEEE International Conference on Ultra-Wideband (ICUWB), 2009: 22[19] Liu Y H, Li C L, Lin T H. A 200-pJ/b MUX-based RF transmitter for implantable multichannel neural recording. IEEE Trans Microwave Theory Tech, 2009, 57(10): 2533 doi: 10.1109/TMTT.2009.2029955[20] Wang H, Sun L, Huang L, et al. Design of UWB circuits with inductive peaking technique. IEEE International Conference on Microwave and Millimeter Wave Technology (ICMMT), 2012(1): 1[21] Lee H D, Lee K A, Hong S. A wideband CMOS variable gain amplifier with an exponential gain control. IEEE Trans Microwave Theory Tech, 2007, 55(6): 1363 doi: 10.1109/TMTT.2007.896787[22] Li C, Lu H, Yutong Y, et al. High performance QVCO design with series coupling in CMOS technology. J Semicond, 2011, 32(11): 115004 doi: 10.1088/1674-4926/32/11/115004[23] Hajimiri A, Lee T H. Design issues in CMOS differential LC oscillators. IEEE J Solid-State Circuits, 1999, 34(5): 717 doi: 10.1109/4.760384[24] Ismail A, Abidi A A. CMOS differential LC oscillator with suppressed up-converted flicker noise. IEEE International Solid-State Circuits Conference (ISSCC), 2003: 98[25] Fanori L, Liscidini A, Castello R. Capacitive degeneration in LC-tank oscillator for DCO fine-frequency tuning. IEEE J Solid-State Circuits, 2010, 45(12): 2737 doi: 10.1109/JSSC.2010.2077190[26] Temporiti E, Albasini G, Bietti I, et al. A 700-KHz bandwidth ΣΔ fractional synthesizer with spurs compensation and linearization techniques for wcdma applications. IEEE J Solid-State Circuits, 2004, 39(9): 1446 doi: 10.1109/JSSC.2004.831598[27] Lee J S, Keel M S, Lim S I, et al. Charge pump with perfect current matching characteristics in phase-locked loops. Electronics Letters, 2000, 36(23): 1907 doi: 10.1049/el:20001358[28] Rhee W, Song B S, Ali A. A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order/spl Delta//spl Sigma/ modulator. IEEE J Solid-State Circuits, 2000, 35(10): 1453 doi: 10.1109/4.871322[29] Kim N S, Rabaey J M. A high data-rate energy-efficient triple-channel uwb-based cognitive radio. IEEE J Solid-State Circuits, 2016, 51(4): 809 doi: 10.1109/JSSC.2015.2512934[30] Medi A, Namgoong W. A high data-rate energy-efficient interference-tolerant fully integrated CMOS frequency channelized UWB transceiver for impulse radio. IEEE J Solid-State Circuits, 2008, 43(4): 974 doi: 10.1109/JSSC.2008.917513 -

Proportional views

DownLoad:

DownLoad: