| Citation: |

Yasin Asadi. Optical network-on-chip (ONoC) architectures: a detailed analysis of optical router designs[J]. Journal of Semiconductors, 2025, 46(3): 031401. doi: 10.1088/1674-4926/24060006

****

Y Asadi, Optical network-on-chip (ONoC) architectures: a detailed analysis of optical router designs[J]. J. Semicond., 2025, 46(3), 031401 doi: 10.1088/1674-4926/24060006

|

Optical network-on-chip (ONoC) architectures: a detailed analysis of optical router designs

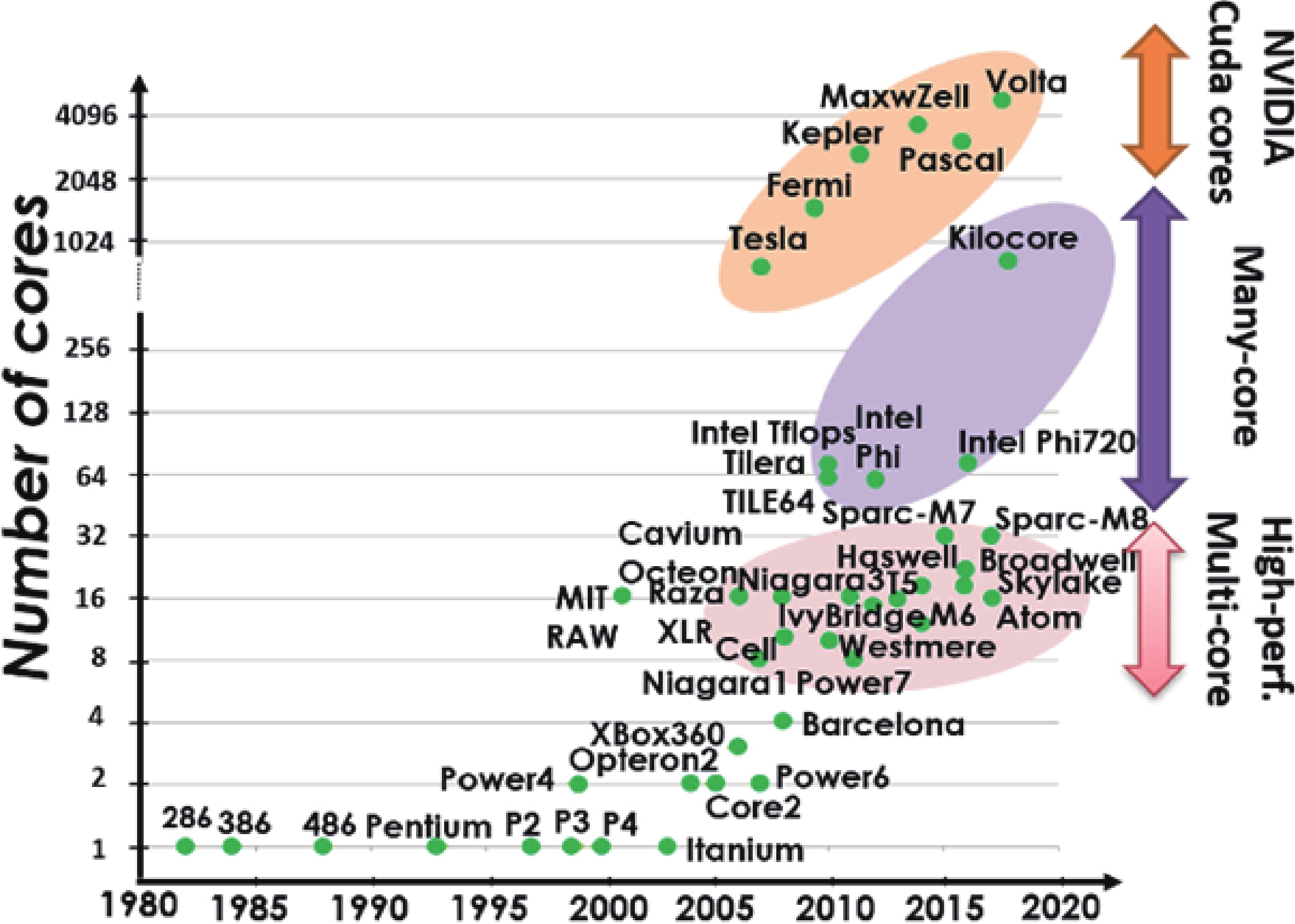

DOI: 10.1088/1674-4926/24060006

CSTR: 32376.14.1674-4926.24060006

More Information-

Abstract

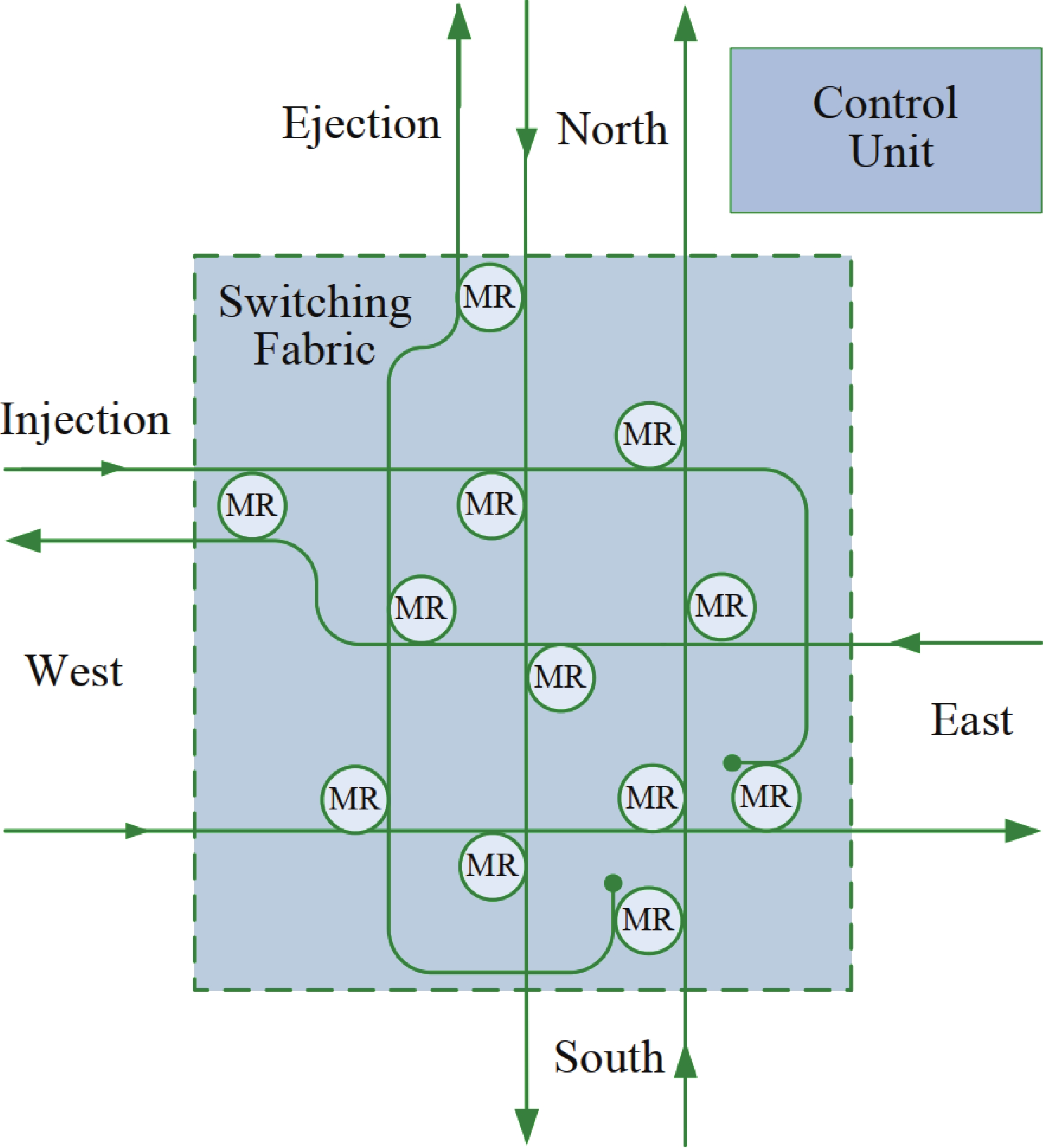

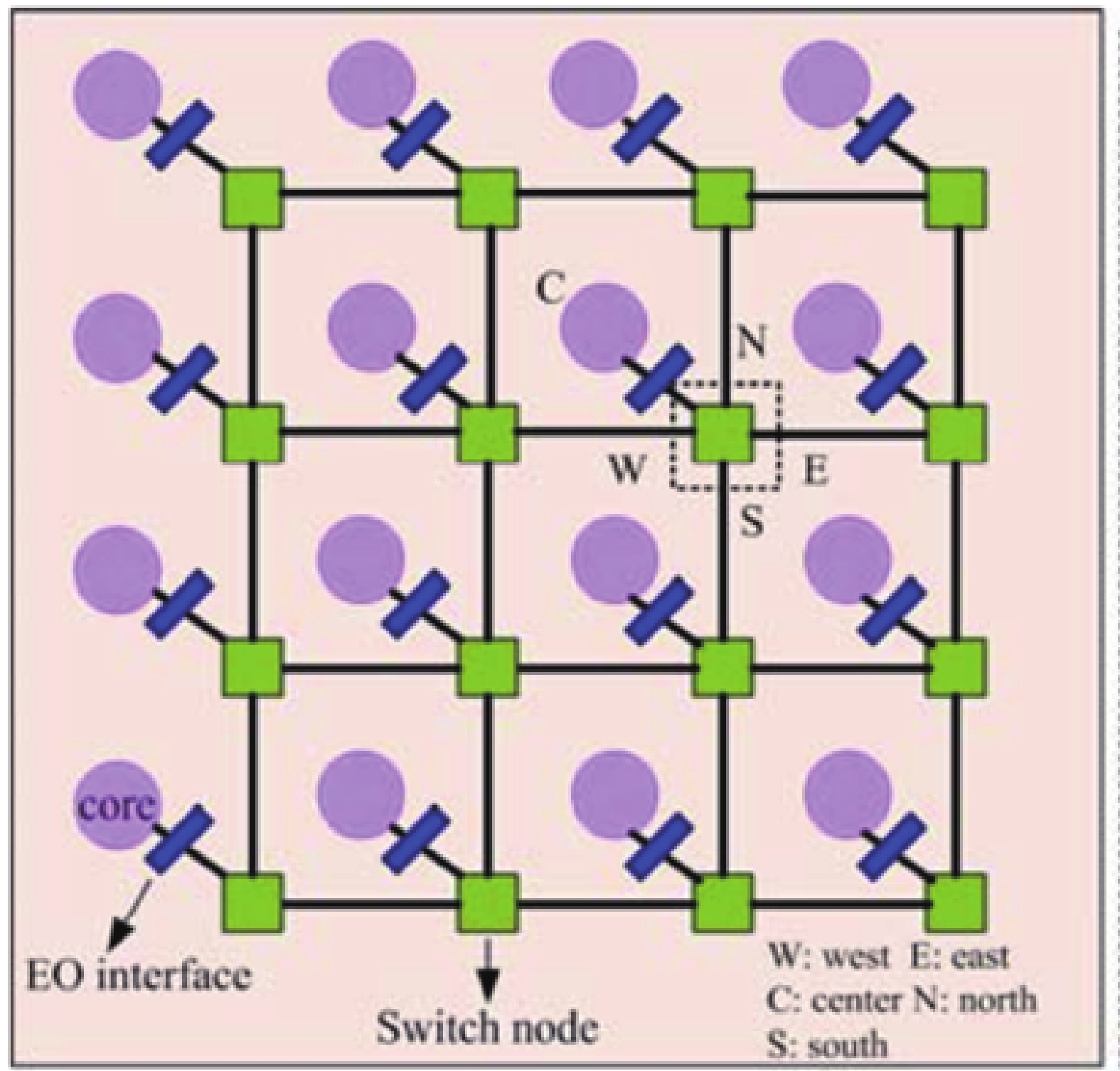

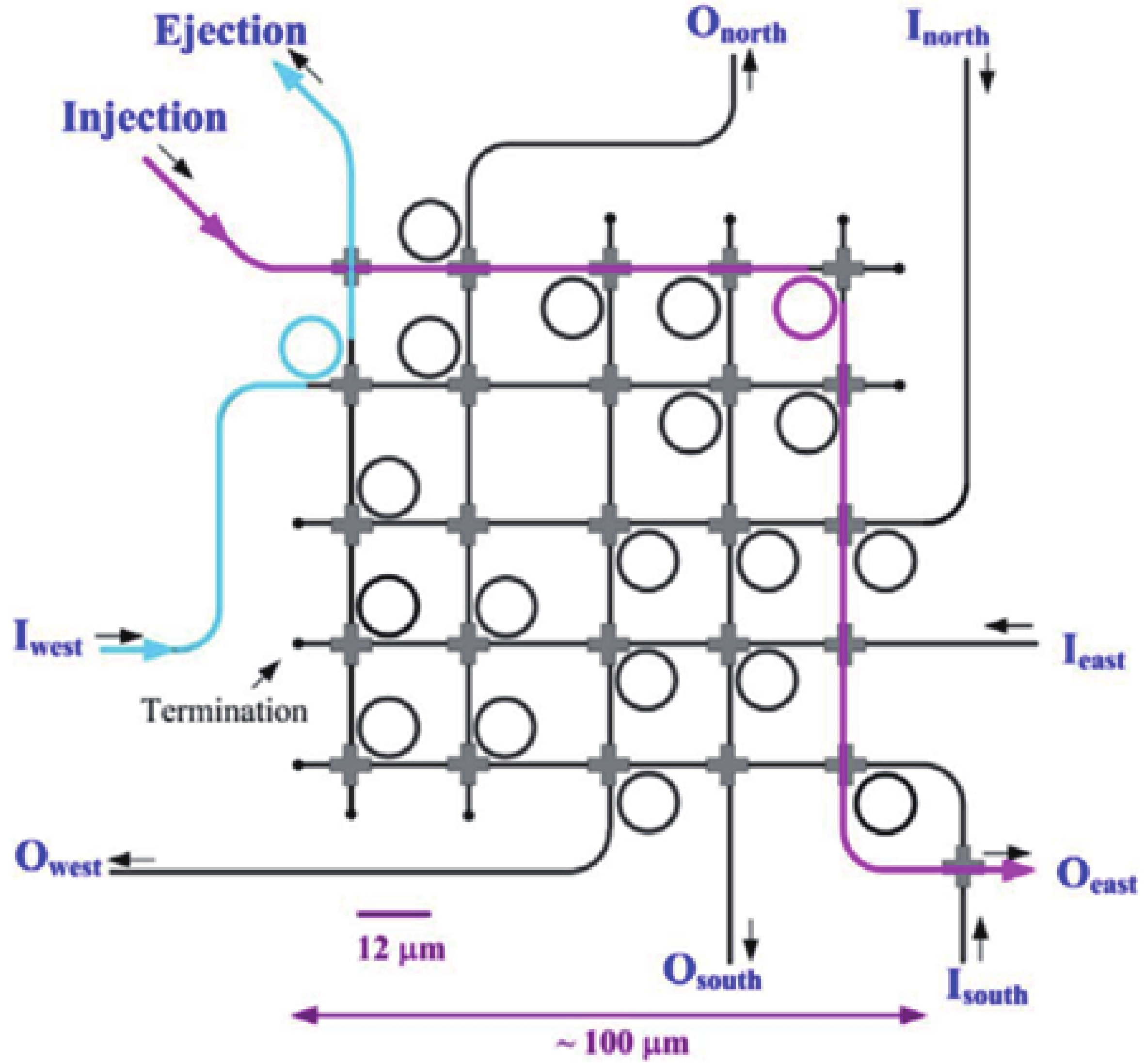

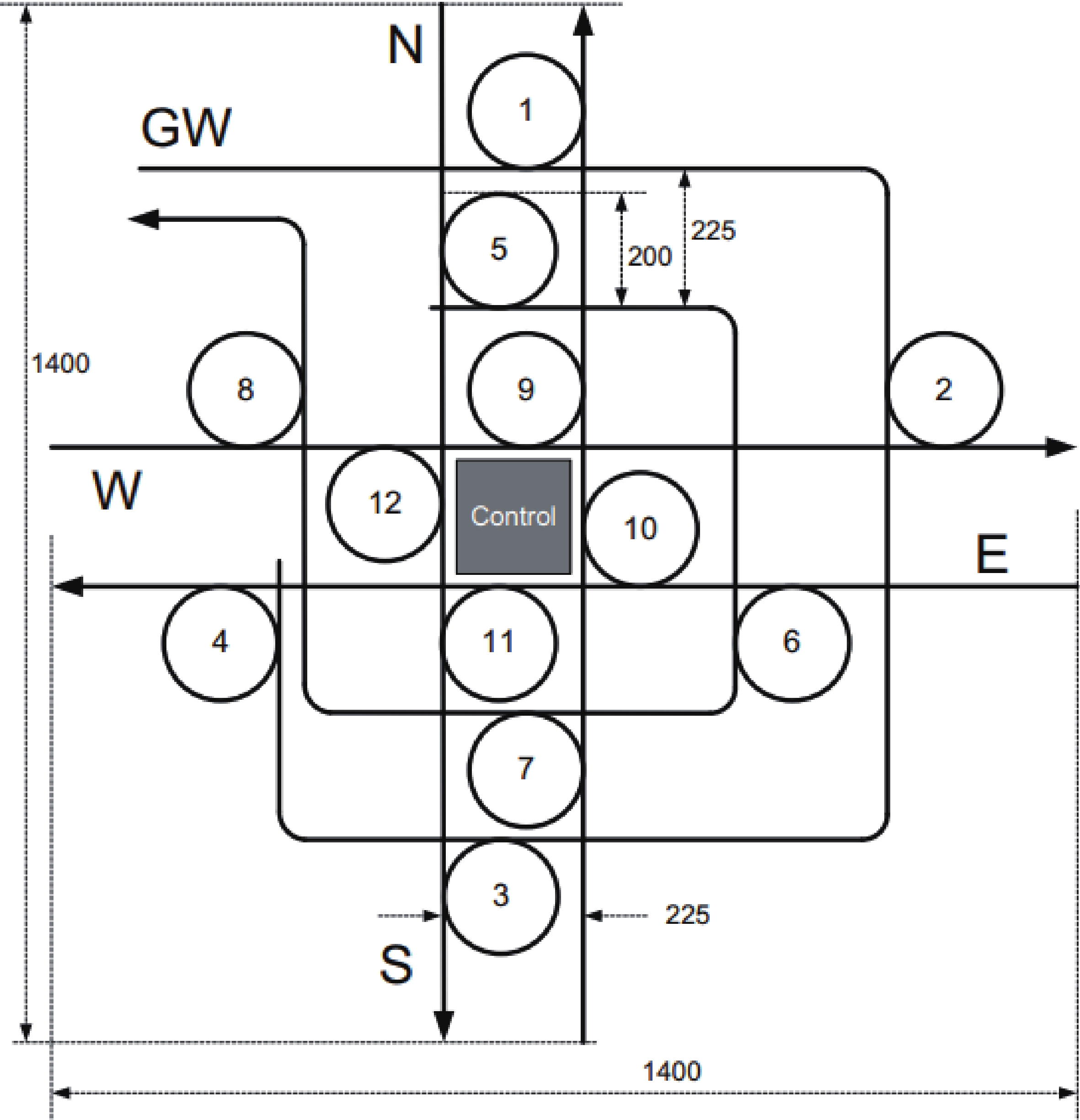

Optical network-on-chip (ONoC) systems have emerged as a promising solution to overcome limitations of traditional electronic interconnects. Efficient ONoC architectures rely on optical routers, enabling high-speed data transfer, efficient routing, and scalability. This paper presents a comprehensive survey analyzing optical router designs, specifically microring resonators (MRRs), Mach−Zehnder interferometers (MZIs), and hybrid architectures. Selected comparison criteria, chosen for their critical importance, significantly impact router functionality and performance. By emphasizing these criteria, valuable insights into the strengths and limitations of different designs are gained, facilitating informed decisions and advancements in optical networking. While other factors contribute to performance and efficiency, the chosen criteria consistently address fundamental elements, enabling meaningful evaluation. This work serves as a valuable resource for beginners, providing a solid foundation in understanding ONoC and optical routers. It also offers an in-depth survey for experts, laying the groundwork for further exploration. Additionally, the importance of considering design constraints and requirements when selecting an optimal router design is highlighted. Continued research and innovation will enable the development of efficient optical router solutions that meet the evolving needs of modern computing systems. This survey underscores the significance of ongoing advancements in the field and their potential impact on future technologies. -

References

[1] Fujikata J, Nishi K, Gomyo A, et al. LSI on-chip optical interconnection with Si nano-photonics. IEICE Trans Electron, 2008, 91(1), 131 doi: 10.1093/ietele/e91-c.2.131[2] Zydek D, Shlayan N, Regentova E, et al. Review of packet switching technologies for future NoC. 19th International Conference on Systems Engineering, 2008, 306 doi: 10.1109/ICSEng.2008.47[3] Chen K N, Kobrinsky M J, Barnett B C, et al. Comparisons of conventional, 3-D, optical, and RF interconnects for on-chip clock distribution. IEEE Trans Electron Devices, 2004, 51(2), 233 doi: 10.1109/TED.2003.821567[4] Haurylau M, Chen G, Chen H, et al. On-chip optical interconnect roadmap: Challenges and critical directions. IEEE J Select Topics Quantum Electron, 2006, 12(6), 1699 doi: 10.1109/JSTQE.2006.880615[5] Kapur P, Saraswat K C. Comparisons between electrical and optical interconnects for on-chip signaling. IEEE 2002 International Interconnect Technology Conference, 2002, 89 doi: 10.1109/IITC.2002.1014897[6] Joshi A, Batten C, Stojanović V, et al. Building manycore processor-to-DRAM networks using monolithic silicon photonics. High Performance Embedded Computing (HPEC) Workshop, 2008 doi: 10.1109/HOTI.2008.11[7] Bashir J, Peter E, Sarangi S R. A survey of on-chip optical interconnects. ACM Comput Surv, 2019, 51(1), 1 doi: 10.1145/3267934[8] Abadal S, Alarcón E, Cabellos-Aparicio A, et al. Graphene-enabled wireless communication for massive multicore architectures. IEEE Commun Mag, 2013, 51(5), 137 doi: 10.1109/MCOM.2013.6658665[9] García-Meca C, Lechago S, Brimont A, et al. On-chip wireless silicon photonics: From reconfigurable interconnects to lab-on-chip devices. Light Sci Appl, 2017, 6, e17053 doi: 10.1038/lsa.2017.53[10] Calò G, Musolino M, Trigona C. Design of reconfigurable on-chip wireless interconnections through optical phased arrays. Opt Express, 2021, 29, 31212 doi: 10.1364/OE.427633[11] Krishnamoorthy A V. Photonics-to-electronics integration for optical interconnects in the early 21st century. Optoelectron Lett, 2006, 2, 163 doi: 10.1007/BF03033536[12] Alexoudi T, Terzenidis N, Pitris S, et al. Optics in computing: From photonic network-on-chip to chip-to-chip interconnects and disintegrated architectures. J Lightwave Technol, 2018, 36(3), 363-379 doi: 10.1109/JLT.2018.2875995[13] Sikder M A I, Kodi A K, Kennedy M, et al. OWN: optical and wireless network-on-chip for Kilo-core architectures. Proceedings - 2015 IEEE 23rd Annual Symposium on High-Performance Interconnects, HOTI, 2015, 44 doi: 10.1109/HOTI.2015.14[14] Kurian G, Miller J E, Psota J, et al. ATAC: A 1000-core cache-coherent processor with on-chip optical network. Proceedings of the 19th International Conference on Parallel Architectures and Compilation Techniques, 2010, 477 doi: 10.1145/1854273.1854332[15] Bogaerts W, Selvaraja S K. Compact single-mode silicon hybrid rib/strip waveguide with adiabatic bends. IEEE Photonics J, 2011, 3, 422 doi: 10.1109/JPHOT.2011.2142931[16] Bogaerts W, Selvaraja S K, Dumon P, et al. Silicon-on-insulator spectral filters fabricated with CMOS technology. IEEE Journal on Selected Topics in Quantum Electronics, 2010, 16, 33 doi: 10.1109/JSTQE.2009.2039680[17] Vivien L, Osmond J, Fédéli J-M, et al. 42 GHz pin Germanium photodetector integrated in a silicon-on-insulator waveguide. Opt Express, 2009, 17, 6252 doi: 10.1364/oe.17.006252[18] Reed G T, Mashanovich G, Gardes F. Silicon optical modulators. Nat Photonics, 2008, 4, 518 doi: 10.1038/nphoton.2010.179[19] Selvaraja S K, Bogaerts W, Dumon P, et al. Subnanometer linewidth uniformity in silicon nanophotonic waveguide devices using CMOS fabrication technology. IEEE Journal on Selected Topics in Quantum Electronics, 2010, 16, 316 doi: 10.1109/JSTQE.2009.2026550[20] Mekis A, Gloeckner S, Masini G, et al. A grating-coupler-enabled CMOS photonics platform. IEEE Journal on Selected Topics in Quantum Electronics, 2011, 17, 597 doi: 10.1109/JSTQE.2010.2086049[21] Werner S, Navaridas J, Luja M M. A survey on optical network-on-chip architectures. ACM Comput Surv, 2017, 50 doi: 10.1145/3131346[22] Khriachtchev L. Silicon nanophotonics: basic principles, present status, and perspectives. CRC Press, 2016 doi: 10.1201/9781315364797[23] Samanta S, Banerji P, Ganguly P. Photonic waveguide components on silicon substrate: Modeling and experiments. 2020.[24] Lipson M. Guiding, modulating, and emitting light on silicon-challenges and opportunities. J Lightwave Technol, 2005, 23, 4222 doi: 10.1109/JLT.2005.858225[25] Manolatou C, Haus H A. High density integrated optics: Passive components for dense optical integration. Springer, 2002, 97 doi: 10.1007/978-1-4615-0855-7[26] Lee B G, Chen X, Biberman A, et al. Ultrahigh-bandwidth silicon photonic nanowire waveguides for on-chip networks. IEEE Photonics Technol Lett, 2008, 20, 398 doi: 10.1109/LPT.2008.916912[27] Bergman K, Carloni L P, Biberman A, et al. Photonic network-on-chip design. In: Integrated Circuits and Systems, vol. 68. New York, NY: Springer New York, 2014 doi: 10.1007/978-1-4419-9335-9[28] Bogaerts W, Dumon P, Van Thourhout D, et al. Low-loss, low-cross-talk crossings for silicon-on-insulator nanophotonic waveguides. Opt Lett, 2007, 32, 2801 doi: 10.1364/OL.32.002801[29] Xu F, Poon A W. Silicon cross-connect filters using microring resonator coupled multimode-interference-based waveguide crossings. Opt Express, 2008, 16, 8649 doi: 10.1364/OE.16.008649[30] Popovic M A, Ippen E P, Kartner F X. Low-loss Bloch waves in open structures and highly compact, efficient Si waveguide-crossing arrays. LEOS 2007-IEEE Lasers and Electro-Optics Society Annual Meeting Conference Proceedings, 2007, 56 doi: 10.1109/LEOS.2007.4382272[31] Shestopalov Y, Smirnov Y, Smolkin E. Optical waveguide theory. In: Springer Series in Optical Sciences, vol. 237. Singapore: Springer Singapore, 2022 doi: 10.1007/978-981-19-0584-1[32] Wu S, Mu X, Cheng L, et al. State-of-the-art and perspectives on silicon waveguide crossings: A review. Micromachines (Basel), 2020, 11, 1 doi: 10.3390/mi11030326[33] Molesky S, Lin Z, Piggott A Y, et al. Inverse design in nanophotonics. Nat Photonics, 2018, 12, 659 doi: 10.1038/s41566-018-0246-9[34] Sajedian I, Badloe T, Rho J. Finding the best design parameters for optical nanostructures using reinforcement learning, 2018[35] Kasper E, Yu J. silicon-based photonics. Jenny Stanford Publishing Pte. Ltd., 2021 doi: 10.1201/9781315156514[36] Rong H, Xu S, Kuo Y H, et al. Low-threshold continuous-wave Raman silicon laser. Nat Photonics, 2007, 1, 232 doi: 10.1038/nphoton.2007.29[37] Marcatili E A J. Bends in optical dielectric guides. Bell System Technical Journal, 1969, 48, 2103 doi: 10.1002/j.1538-7305.1969.tb01167.x[38] Chao C Y, Fung W, Guo L J. Polymer microring resonators for biochemical sensing applications. IEEE J Select Topics Quantum Electron, 2006, 12(1), 134 doi: 10.1109/JSTQE.2005.862945[39] Zhang X, Li L, Wang Y. Biodegradable polymers for photonics: From materials to devices. Adv Mater, 2022, 34(6), 2100356 doi: 10.3390/photonics8070235[40] Chen Q, Wang W, Liu Z. Recent developments in flexible photonic sensors based on biodegradable materials. Nat Commun, 2021, 12, 1185 doi: 10.1038/s41467-021-21352-8[41] Lira H L R, Manipatruni S, Lipson M. Broadband hitless silicon electro-optic switch for on-chip optical networks. Opt Express, 2009, 17, 22271 doi: 10.1364/OE.17.022271[42] Vlasov Y, Green W M J, Xia F. High-throughput silicon nanophotonic wavelength-insensitive switch for on-chip optical networks. Nat Photonics, 2008, 2, 242 doi: 10.1038/nphoton.2008.31[43] Xu Q, Manipatruni S, Schmidt B, et al. 12.5 Gbit/s carrier-injection-based silicon microring modulators. Opt Express, 2007, 15, 430 doi: 10.1364/OE.15.000430[44] Watts M R, Trotter D C, Young R W, et al. Ultralow power silicon microdisk modulators and switches. 2008 5th IEEE International Conference on Group IV Photonics, 2008, 4 doi: 10.1109/GROUP4.2008.4638077[45] Xu X, Zheng X, He F, et al. Observation of third-order nonlinearities in graphene oxide film at telecommunication wavelengths. Sci Rep, 2017, 7, 9646 doi: 10.1038/s41598-017-09583-6[46] Biberman A, Bergman K. Optical interconnection networks for high-performance computing systems. Reports on Progress in Physics, 2012, 75, 46402 doi: 10.1088/0034-4885/75/4/046402[47] Little B E, Chu S T, Pan W, et al. Microring resonator arrays for VLSI photonics. IEEE Photonics Technol Lett, 2000, 12, 323 doi: 10.1109/68.826928[48] Shacham A, Bergman K, Carloni L P. On the design of a photonic network-on-chip. Proceedings-NOCS 2007: First International Symposium on Networks-on-Chip, 2007, 53 doi: 10.1109/NOCS.2007.35[49] Shacham A, Lee B G, Biberman A, et al. Photonic NoC for DMA communications in chip multiprocessors. Proceedings-15th Annual IEEE Symposium on High-Performance Interconnects, HOT Interconnects, 2007, 29 doi: 10.1109/HOTI.2007.9[50] Chang S J, Ni C Y, Wang Z, et al. A compact and low power consumption optical switch based on microrings. IEEE Photonics Technol Lett, 2008, 20, 1021 doi: 10.1109/LPT.2008.923763[51] Gu H, Xu J, Wang Z, et al. A novel optical mesh network-on-chip for gigascale systems-on-chip. IEEE Asia-Pacific Conference on Circuits and Systems, 2008, 1728 doi: 10.1109/APCCAS.2008.4746373[52] Poon A W, Xu F, Luo X, et al. Cascaded active silicon microresonator array cross-connect circuits for WDM networks-on-chip. Silicon Photonics III, 2008, 6898, 689812 doi: 10.1117/12.765090[53] Poon A W, Luo X, Xu F, et al. Cascaded microresonator-based matrix switch for silicon on-chip optical interconnection. Proceedings of the IEEE, 2009, 97, 1216 doi: 10.1109/JPROC.2009.2014884[54] Hendry G, Chan J, Kamil S, et al. Silicon nanophotonic network-on-chip using TDM arbitration. Proceedings-18th IEEE Symposium on High Performance Interconnects, HOTI, 2010, 88 doi: 10.1109/HOTI.2010.12[55] Ji R, Yang L, Zhang L, et al. Microring-resonator-based four-port optical router for photonic networks-on-chip. Opt Express, 2011, 19, 18945 doi: 10.1364/OE.19.018945[56] Yang L, Ji R, Zhang L, et al. Optical routers for photonic networks-on-chip. Optics InfoBase Conference Papers, 2011, 1 doi: 10.1117/12.902768[57] Min R, Ji R, Chen Q, et al. A universal method for constructing N-port nonblocking optical router for photonic networks-on-chip. J Lightwave Technol, 2012, 30, 3736 doi: 10.1109/JLT.2012.2227945[58] Shabani H, Roohi A, Reza A, et al. Loss-aware switch design and non-blocking detection algorithm for intra-chip scale photonic interconnection networks. IEEE Trans Comput, 2016, 65, 1789 doi: 10.1109/TC.2015.2458866[59] Gu H, Mo K H, Xu J, et al. A low-power low-cost optical router for optical networks-on-chip in multiprocessor systems-on-chip. Proceedings of the 2009 IEEE Computer Society Annual Symposium on VLSI, ISVLSI, 2009, 19 doi: 10.1109/ISVLSI.2009.19[60] Tan X, Yang M, Zhang L, et al. A generic optical router design for photonic network-on-chips. J Lightwave Technol, 2012, 30, 368 doi: 10.1109/JLT.2011.2178019[61] Kalange O A, Ladniya B B, Kothari R R, et al. Design and analysis of five-port optical router for optical NoC. Proceedings of the International Conference on Inventive Research in Computing Applications, ICIRCA, 2018, 42 doi: 10.1109/ICIRCA.2018.8597198[62] Thirumaran S, Dhanabalan S S, Sannasi I G, et al. Design and analysis of photonic crystal ring resonator based 6 × 6 wavelength router for photonic integrated circuits. IET Optoelectronics, 2021, 15, 40 doi: 10.1049/ote2.12014[63] Fadhel M, Gu H, Wei W, et al. DORR: A DOR-based non-blocking optical router for 3D photonic network-on-chips. IEICE Trans Inf Syst, 2021, E104.D, 688 doi: 10.1587/transinf.2020EDP7122[64] Ji R, Yang L, Zhang L, et al. Five-port optical router for photonic networks-on-chip. Opt Express, 2011, 19, 20258 doi: 10.1364/OE.19.020258[65] Fan G F, Orobtchouk R, Fédéli J M, et al. Highly integrated optical 8 × 8 lambda-router in silicon-on-insulator technology: comparison between the ring and racetrack configuration. Silicon Photonics and Photonic Integrated Circuits II, 2010, 7719, 77190F doi: 10.1117/12.853812[66] Gu H, Xu J, Wang Z, et al. ODOR: A microresonator-based high-performance low-cost router for optical networks-on-chip. Embedded Systems Week 2008-Proceedings of the 6th IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis, CODES+ISSS, 2008, 203 doi: 10.1145/1450135.1450181[67] Chaudhari B S, Patil S S. Optimized designs of low loss non-blocking optical router for ONoC applications. Int J Inf Technol (Singapore), 2020, 12, 91 doi: 10.1007/s41870-019-00298-7[68] Huang L, Wang K, Qi S, et al. Panzer: A 6 × 6 photonic router for optical network-on-chip. IEICE Electronics Express, 2016, 13, 1 doi: 10.1587/elex.13.20160719[69] Tang C, Gu H, Wang K, et al. Waffle: A new photonic plasmonic router for optical network-on-chip. IEICE Trans Inf Syst, 2018, E101. D, 2401 doi: 10.1587/transinf.2018EDL8085[70] Shanmuga Sundar D, Sathyadevaki R, Sridarshini T, et al. Photonic crystal based routers for photonic integrated on-chip networks: a brief analysis. Opt Quantum Electron, 2018, 50, 1 doi: 10.1007/s11082-017-1266-2[71] Asadinia S, Mehrabi M, Yaghoubi E, et al. Surix: Non-blocking and low insertion loss microring resonator-based optical router for photonic network on chip. J Supercomputing, 2021, 77, 4438 doi: 10.1007/s11227-020-03442-4[72] Briere M, Awwal A A S, Abouzied A A, et al. Design and analysis of a five-port optical router based on 3 × 3 and 2 × 2 add-drop optical filters. In: Proceedings of the 2015 IEEE International Symposium on Nanoelectronic and Information Systems, iNIS 2015, 2015, 141 doi: 10.1155/2021/5371330[73] Yu Z, Zhang Q, Jin X, et al. Microring resonator-based optical router for photonic networks-on-chip. Quantum Elec (Woodbury), 2016, 46, 655 doi: 10.1070/QEL15964[74] Jadhav NB, Chaudhari BS. Optimized 6x6 optical router for three-dimensional optical networks-on-chip. J Phys Conf Ser, 2022, 2325(1), 012008 doi: 10.1088/1742-6596/2325/1/012008[75] Yaghoubi E, Reshadi M, Hosseinzadeh M. Mach–Zehnder-based optical router design for photonic networks-on-chip. Opt Eng, 2015, 54(3), 035102 doi: 10.1117/1.OE.54.3.035102[76] Yang M, Green WMJ, Assefa S, et al. Non-blocking 4x4 electro-optic silicon switch for on-chip photonic networks. Opt Express, 2010, 19(1), 47 doi: 10.1364/OE.19.000047[77] Li X, Xiao X, Xu H, et al. Mach–Zehnder-based five-port silicon router for optical interconnects. Opt Lett, 2013, 38(10), 1703 doi: 10.1364/OL.38.001703[78] Geng M, Tang Z, Chang K, et al. N-port strictly non-blocking optical router based on Mach−Zehnder optical switch for photonic networks-on-chip. Opt Commun, 2017, 383, 472 doi: 10.1016/j.optcom.2016.09.023[79] Hop T X, Nuong D T, Linh H D T, et al. Design of silicon TE0/TE1 mode router using Mach−Zehnder and multimode interferometers. J Sci Technol: Issue on Information and Communications Technology, 2021, 19, 22 doi: 10.31130/ict-ud.2021.128[80] Geng M, Tang Z, Chang K, et al. N-port non-Blocking Optical Router For Network-on-chip. Su2A.135, 2017 doi: 10.1364/ACPC.2017.Su2A.135[81] Yang L, Xia Y, Zhang F, et al. Reconfigurable nonblocking 4-port silicon thermo-optic optical router based on Mach–Zehnder optical switches. Opt Lett, 2015, 40, 1235 doi: 10.1364/OL.40.001402[82] Jia H, Zhou T, Zhao Y, et al. Six-port optical switch for cluster-mesh photonic network-on-chip. Nanophotonics, 2018, 7, 116 doi: 10.1515/nanoph-2017-0116[83] Chen Q, Zhang F, Ji R, et al. A universal method for constructing N-port non-blocking optical router based on 2 × 2 optical switch. Prog Electromagn Res Symp, 2014, 22, 357 doi: 10.1364/OE.22.012614[84] Yahya M R, Wu N, Yan G, et al. RoR: A low insertion loss design of rearrangeable hybrid photonic-plasmonic 6 × 6 non-blocking router for ONoCs. IEICE Electronics Express, 2019, 16, 1 doi: 10.1587/elex.16.20190346[85] Shacham A, Bergman K, Carloni L P, et al. Photonic networks-on-chip for future generations of chip multiprocessors. IEEE Trans Comput, 2008, 57, 1246 doi: 10.1109/TC.2008.78[86] Batten C, Joshi A, Stojanovic V, et al. Designing chip-level nanophotonic interconnection networks. IEEE J Emerg Sel Top Circuits Syst, 2012, 2, 137 doi: 10.1109/JETCAS.2012.2193932[87] Gu H, Xu J, Zhang W, et al. A low-loss non-blocking optical router for optical networks-on-chip. IEEE Photon Technol Lett, 2010, 22, 1290[88] Zhou L, Liu W, Zhang X, et al. Accelerating fully connected neural networks on optical networks-on-chip. IEEE Trans Very Large Scale Integr VLSI Syst, 2020, 28, 1 doi: 10.48550/arXiv.2109.14878[89] Liu Z, Liu X, Xiao Z, et al. Integrated nanophotonic wavelength router based on an intelligent algorithm. Optica, 2019, 6(10), 1373 doi: 10.1364/OPTICA.6.001367[90] Chen J, Xiao W, Li X, et al. A routing optimization method for software-defined optical transport networks based on ensembles and reinforcement learning. Sensors, 2022, 22(21), 8139 doi: 10.3390/s22218139[91] Sankaran GC, Sivalingam KM. A survey of hybrid optical data center network architectures. Photonic Netw Commun, 2017, 33, 101 doi: 10.1007/s11107-016-0643-2[92] Xiang L, Cheng Y, Yu X, et al. High-performance thermal management system for high-power LEDs based on double-nozzle spray cooling. Appl Therm Eng, 2023, 231, 121005 doi: 10.1016/j.applthermaleng.2023.121005[93] Winzer P, Neilson DT, Chraplyvy A R. Fiber-optic transmission and networking: the previous 20 and the next 20 years. Opt Express, 2018, 26(18), 24190 doi: 10.1364/OE.26.024190[94] Sharma K, Sehgal V K. Modern architecture for photonic networks-on-chip. J Supercomput, 2020, 76, 9901 doi: 10.1007/s11227-020-03220-2[95] Asadi B, Zia S M, Al-Khafaji H M R, et al. Network-on-chip and photonic network-on-chip basic concepts: A survey. J Electron Test, 2023, 39, 11 doi: 10.1007/s10836-023-06046-x[96] Do N, Truong D, Nguyen D, et al. Self-controlling photonic-on-chip networks with deep reinforcement learning. Sci Rep, 2021, 11, 23151 doi: 10.1038/s41598-021-02583-7 -

Proportional views

Yasin Asadi is a Computer Engineer, Reviewer, Lecturer, and Researcher with a Bachelor of Science and Master of Science in Computer Engineering from Islamic Azad University, Tehran, Iran. His research interests include Artificial Intelligence (AI), Machine Learning (ML), Data Science, Data Engineering, Data Analysis and Network-on-Chip (NoC), and photonic NoC systems. Asadi investigates multidisciplinary applications of ML in computer engineering to advance scientific knowledge and develop innovative engineering solutions that benefit society. He is a professional member of the Association for Computing Machinery (ACM), IEEE Computer Society, Computer Science Teachers Association (CSTA), and the International Association of Engineers (IAENG).

Yasin Asadi is a Computer Engineer, Reviewer, Lecturer, and Researcher with a Bachelor of Science and Master of Science in Computer Engineering from Islamic Azad University, Tehran, Iran. His research interests include Artificial Intelligence (AI), Machine Learning (ML), Data Science, Data Engineering, Data Analysis and Network-on-Chip (NoC), and photonic NoC systems. Asadi investigates multidisciplinary applications of ML in computer engineering to advance scientific knowledge and develop innovative engineering solutions that benefit society. He is a professional member of the Association for Computing Machinery (ACM), IEEE Computer Society, Computer Science Teachers Association (CSTA), and the International Association of Engineers (IAENG).

DownLoad:

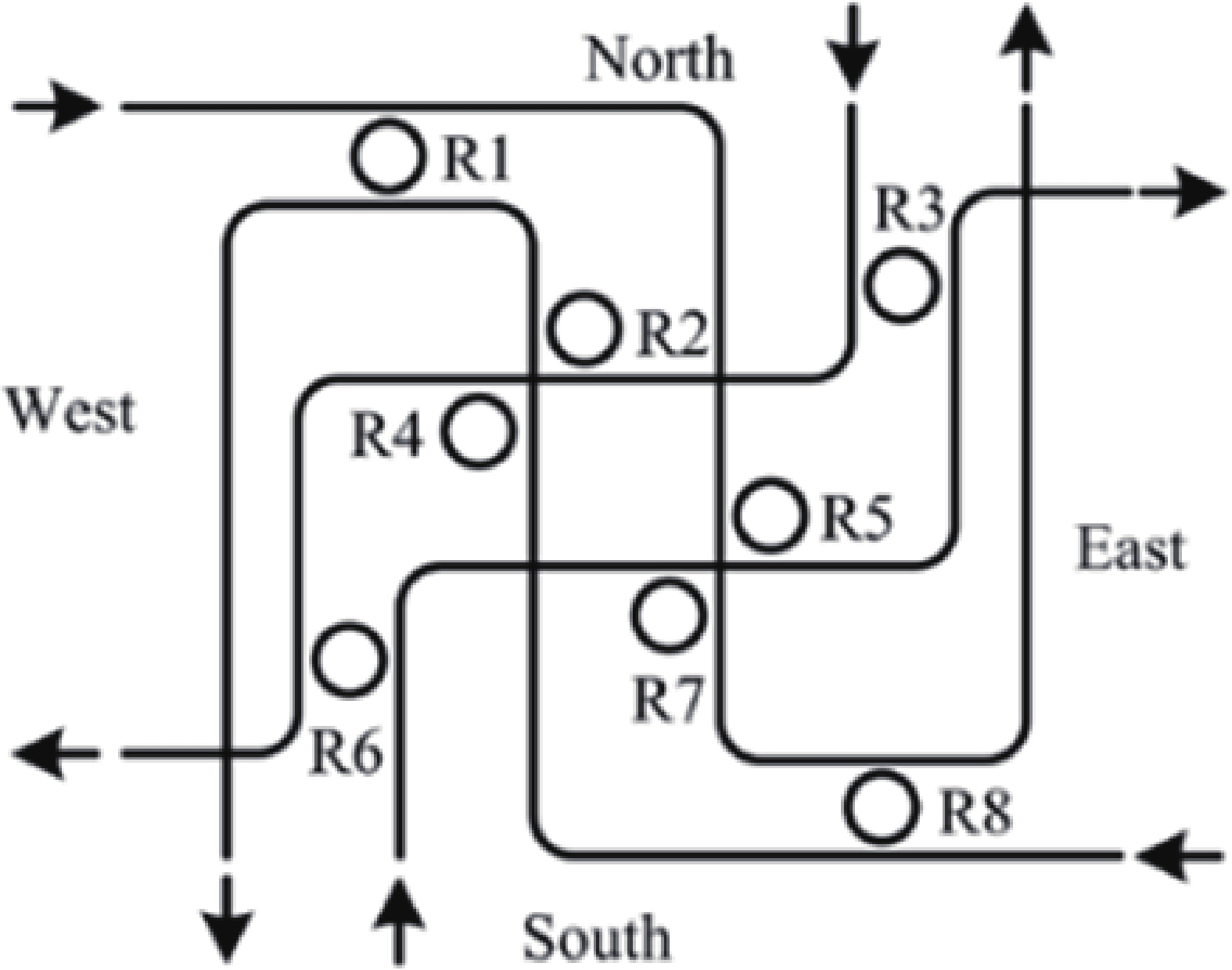

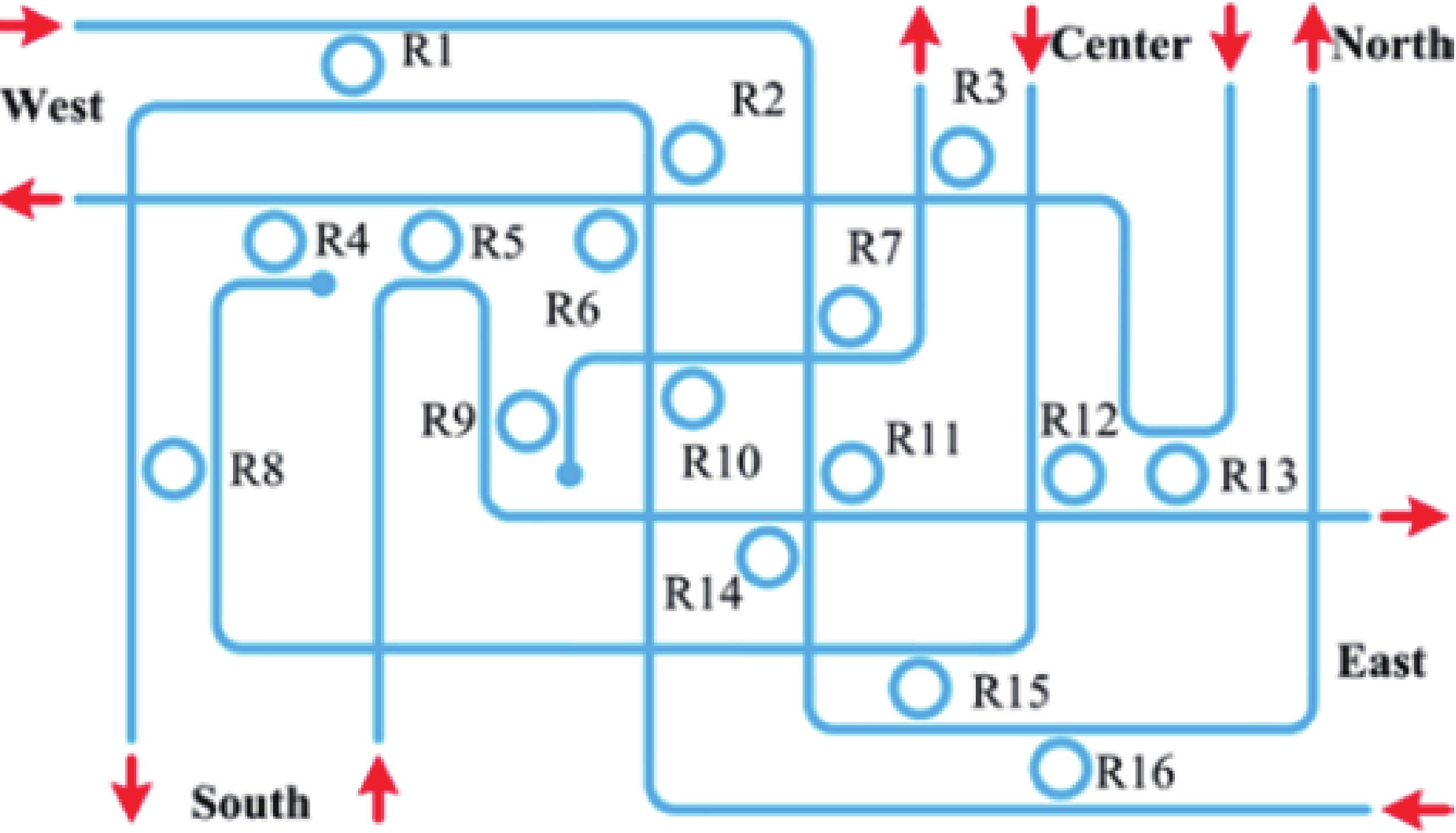

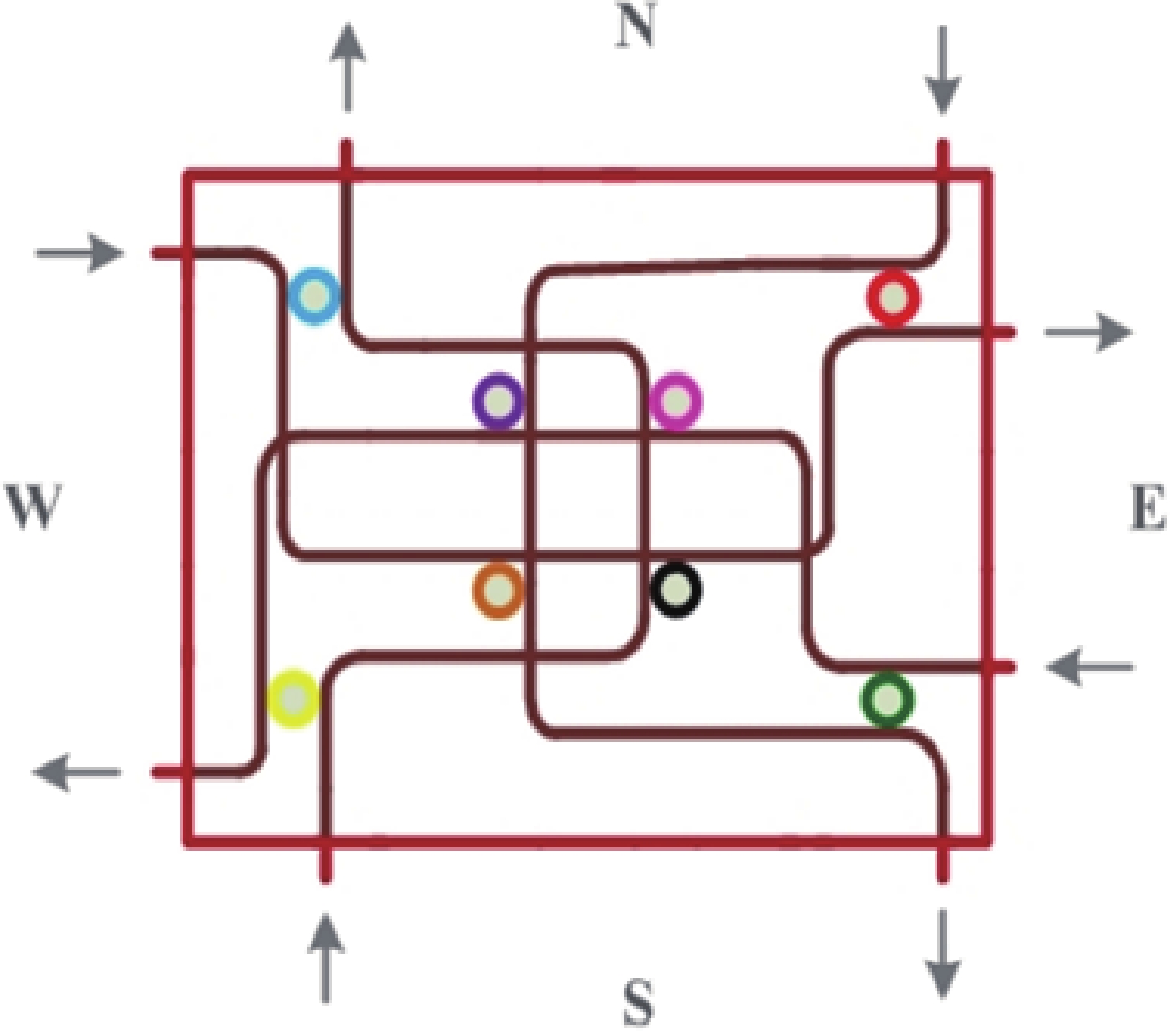

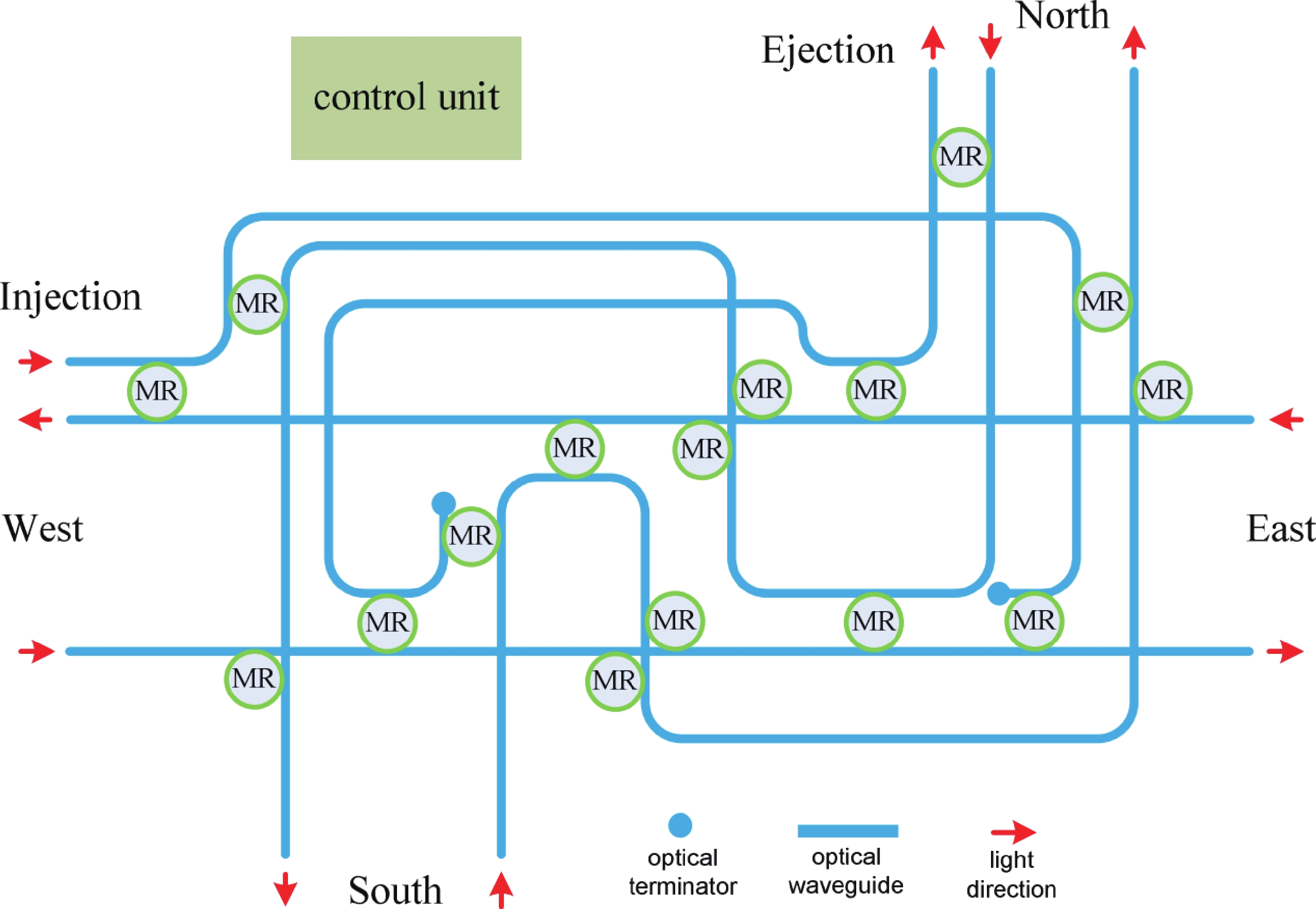

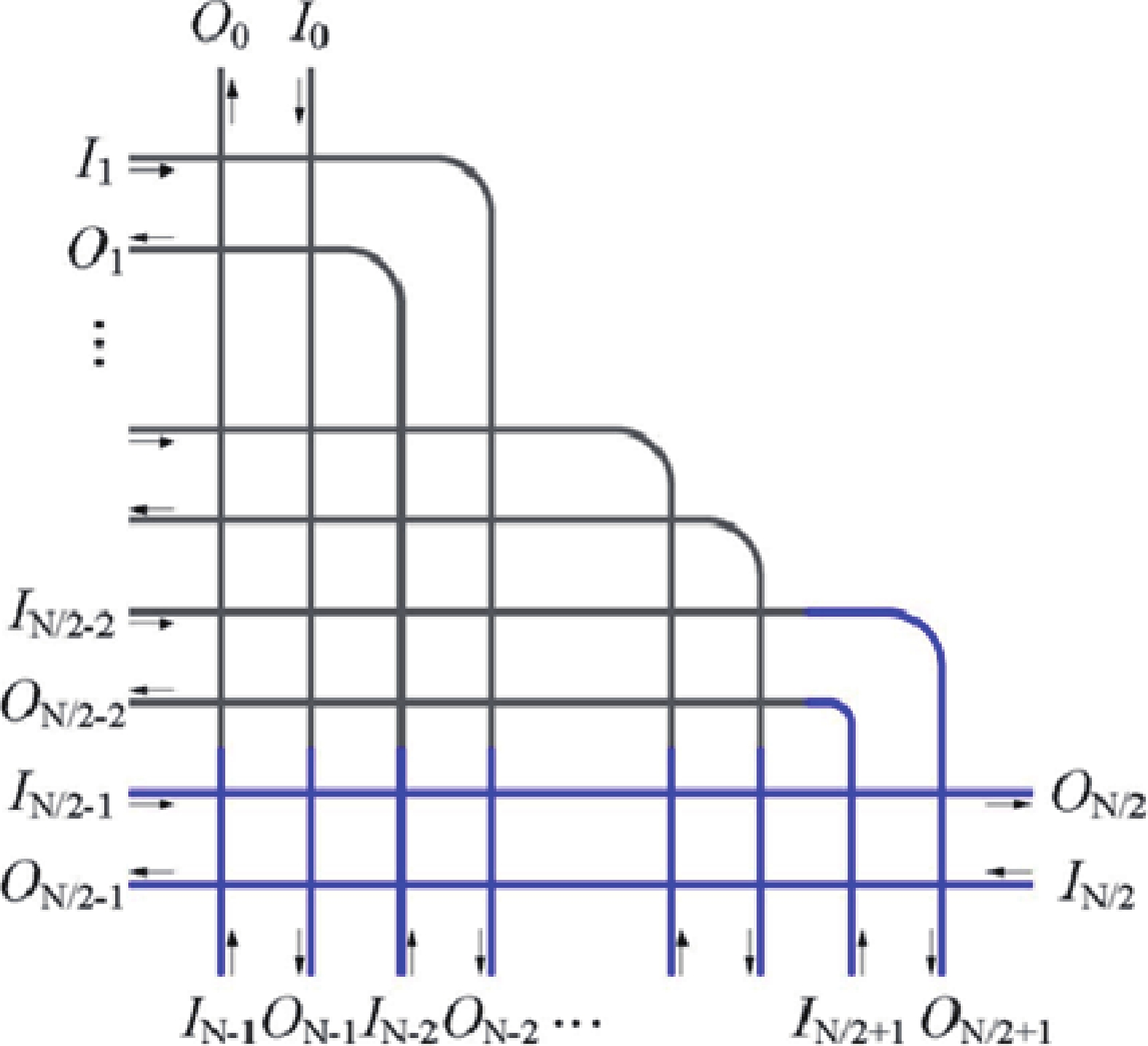

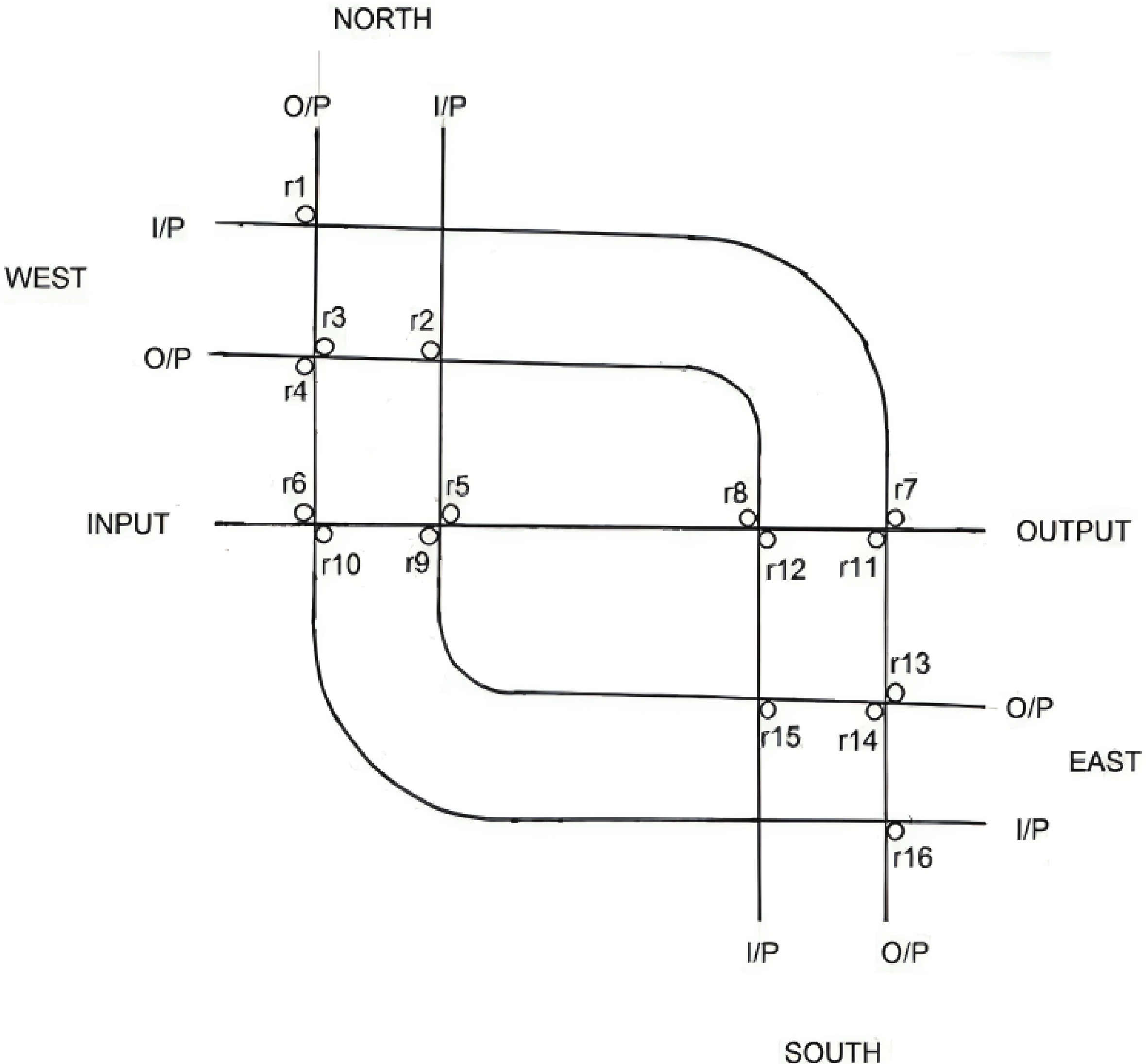

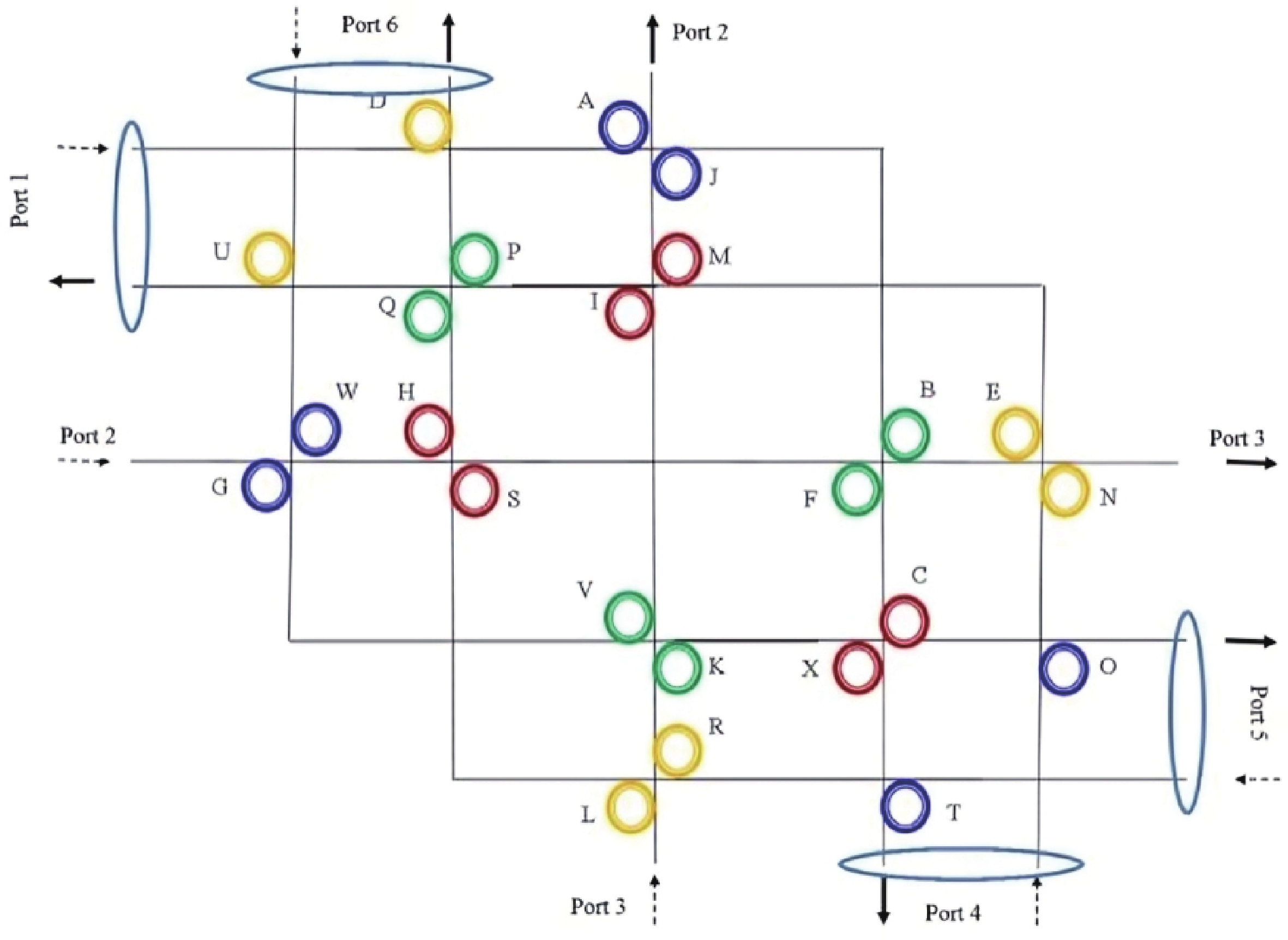

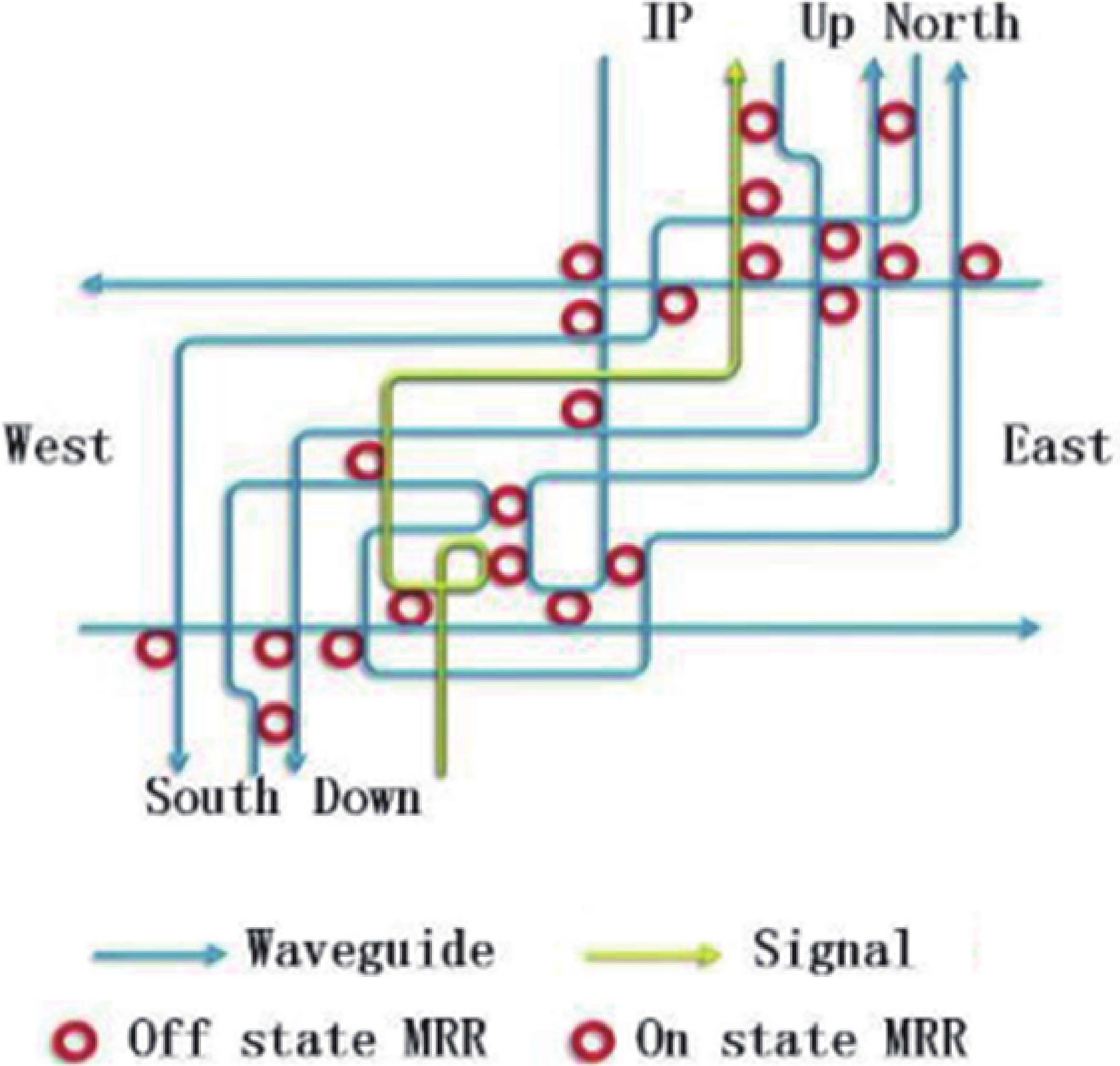

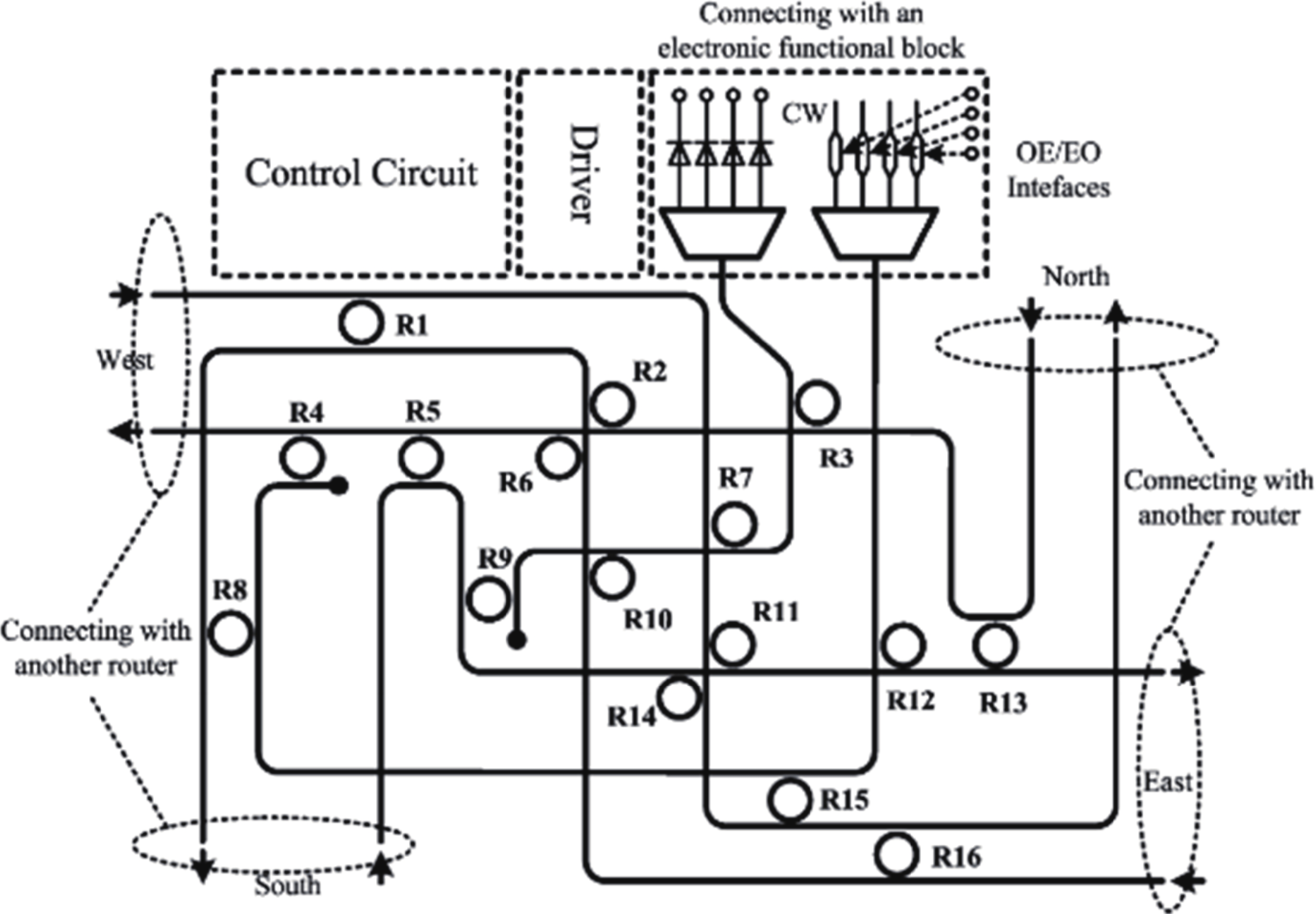

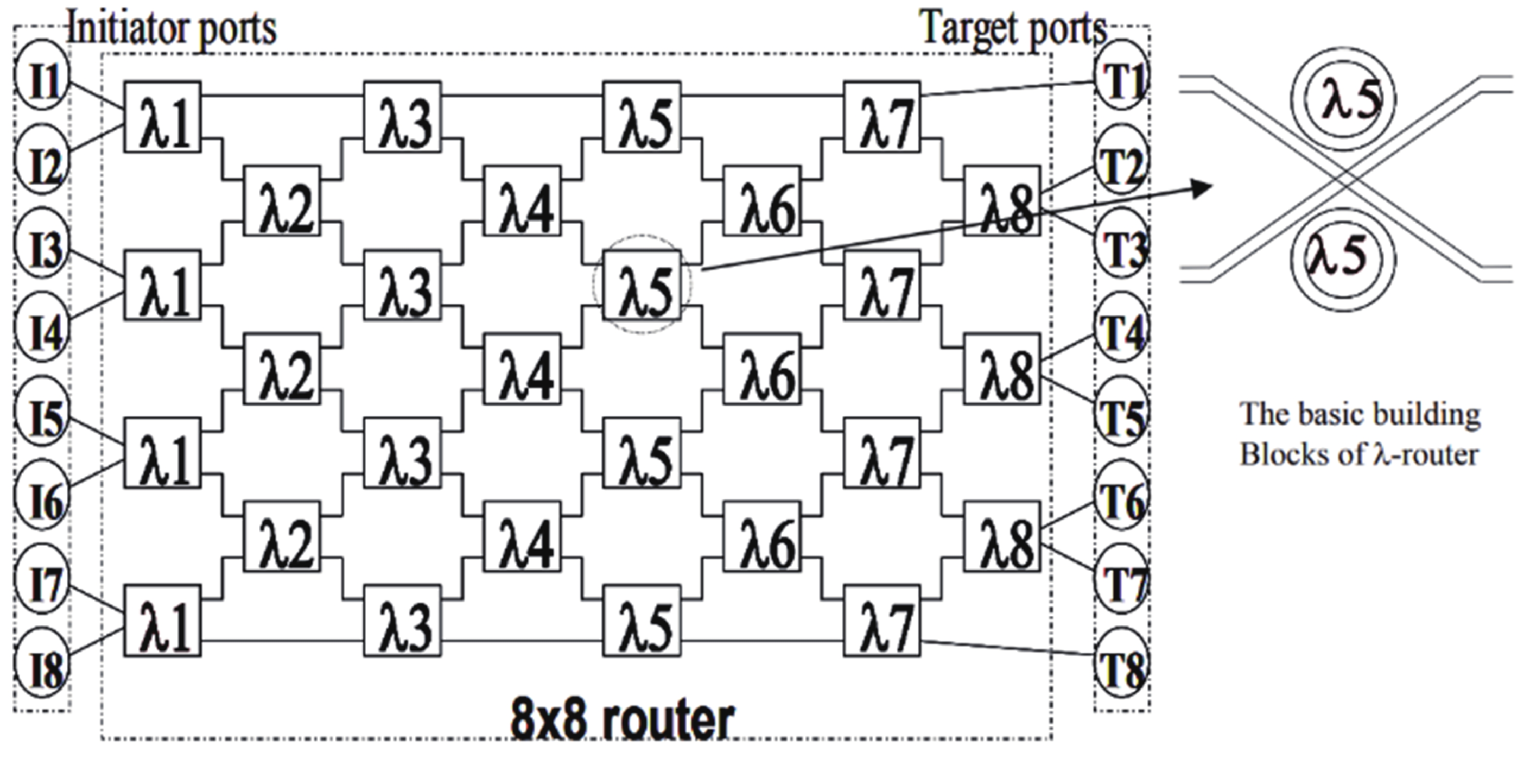

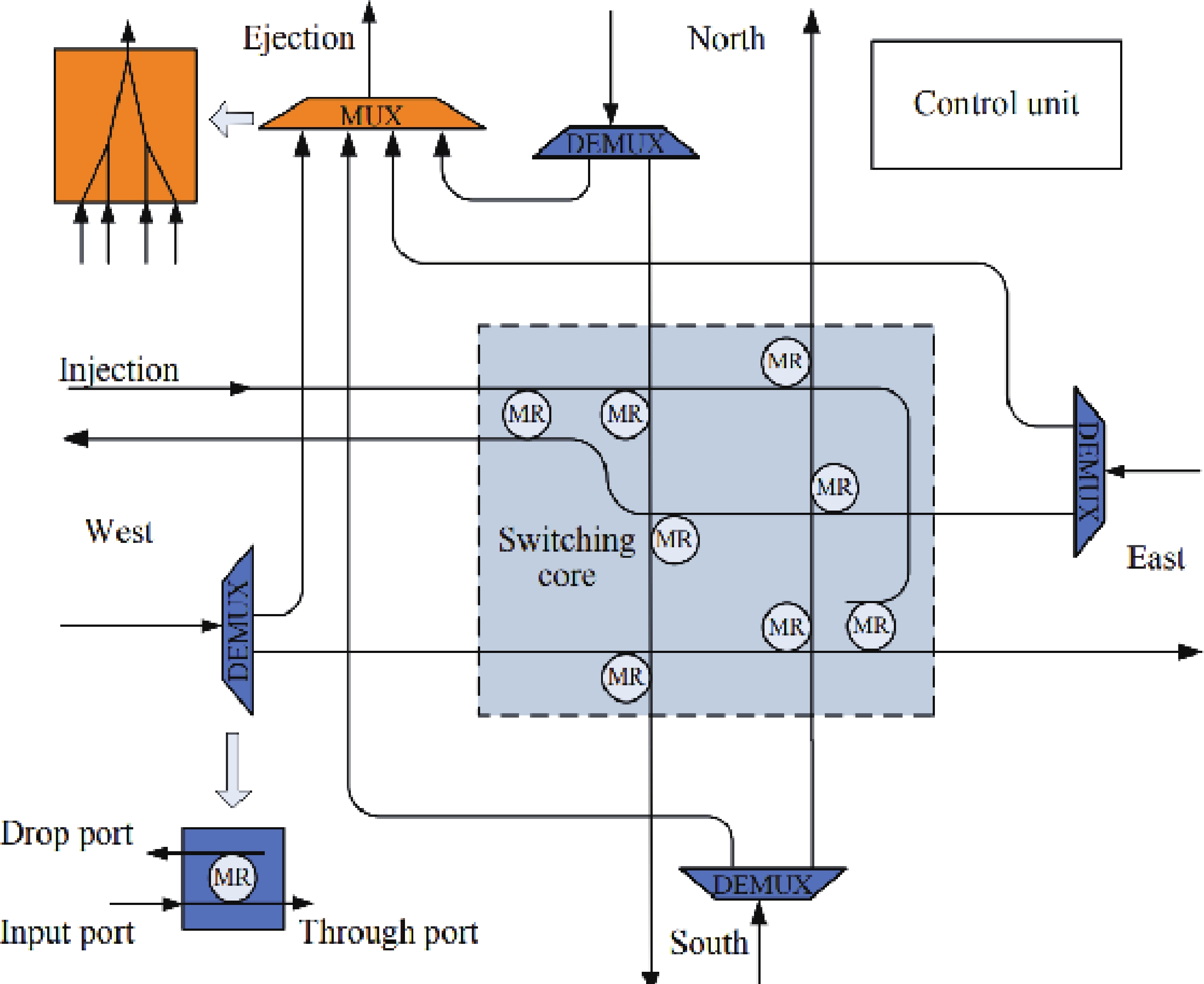

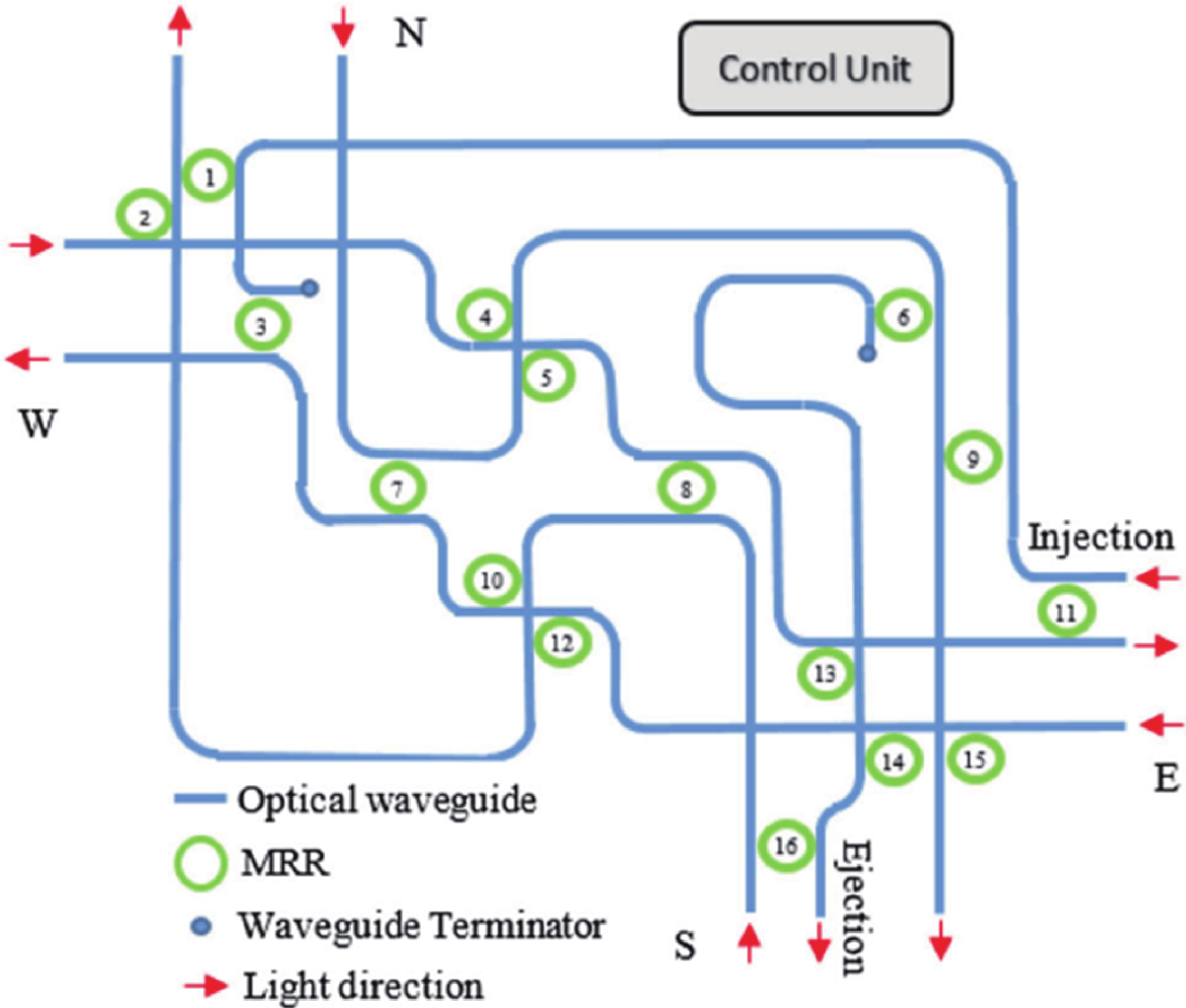

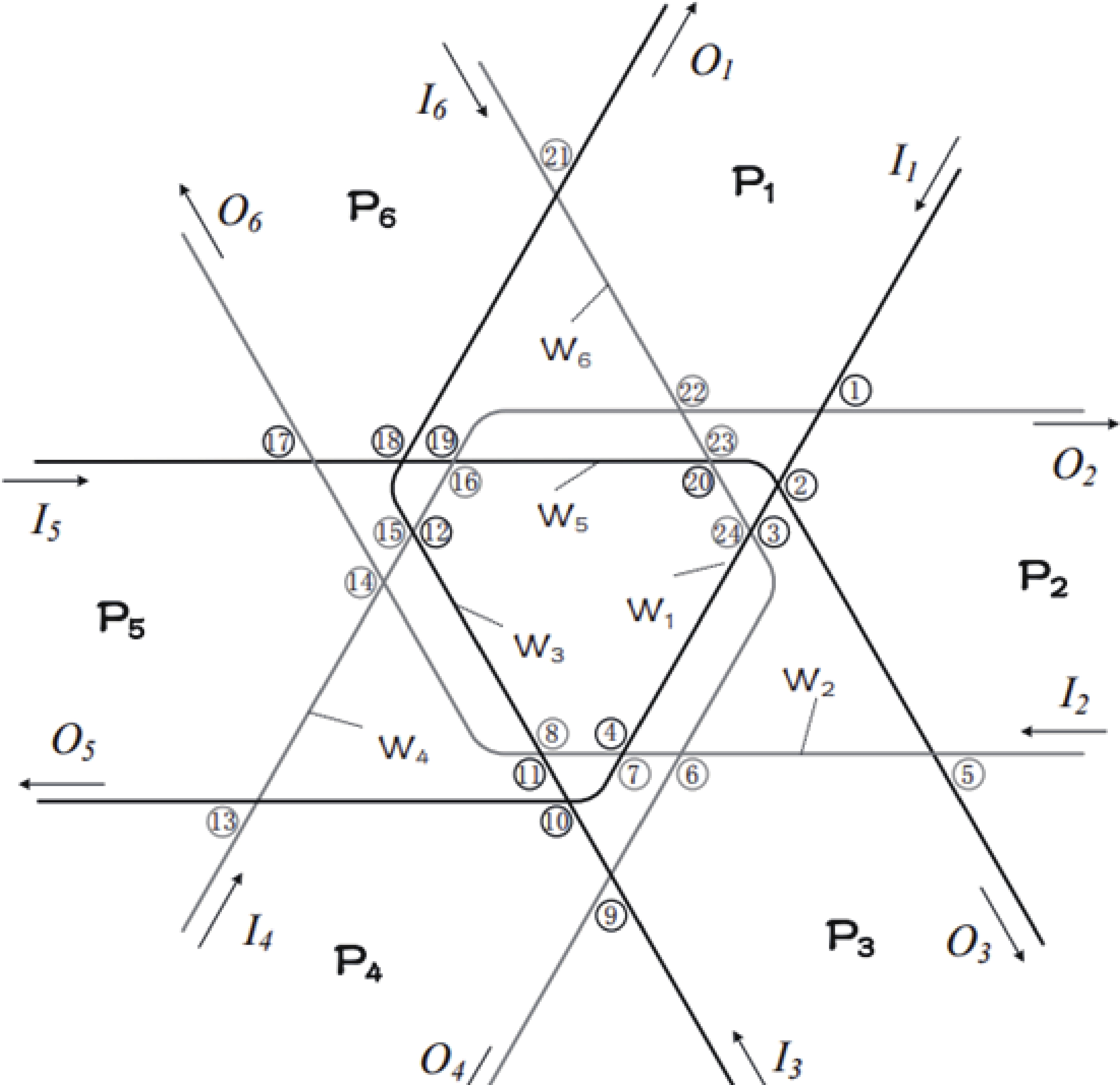

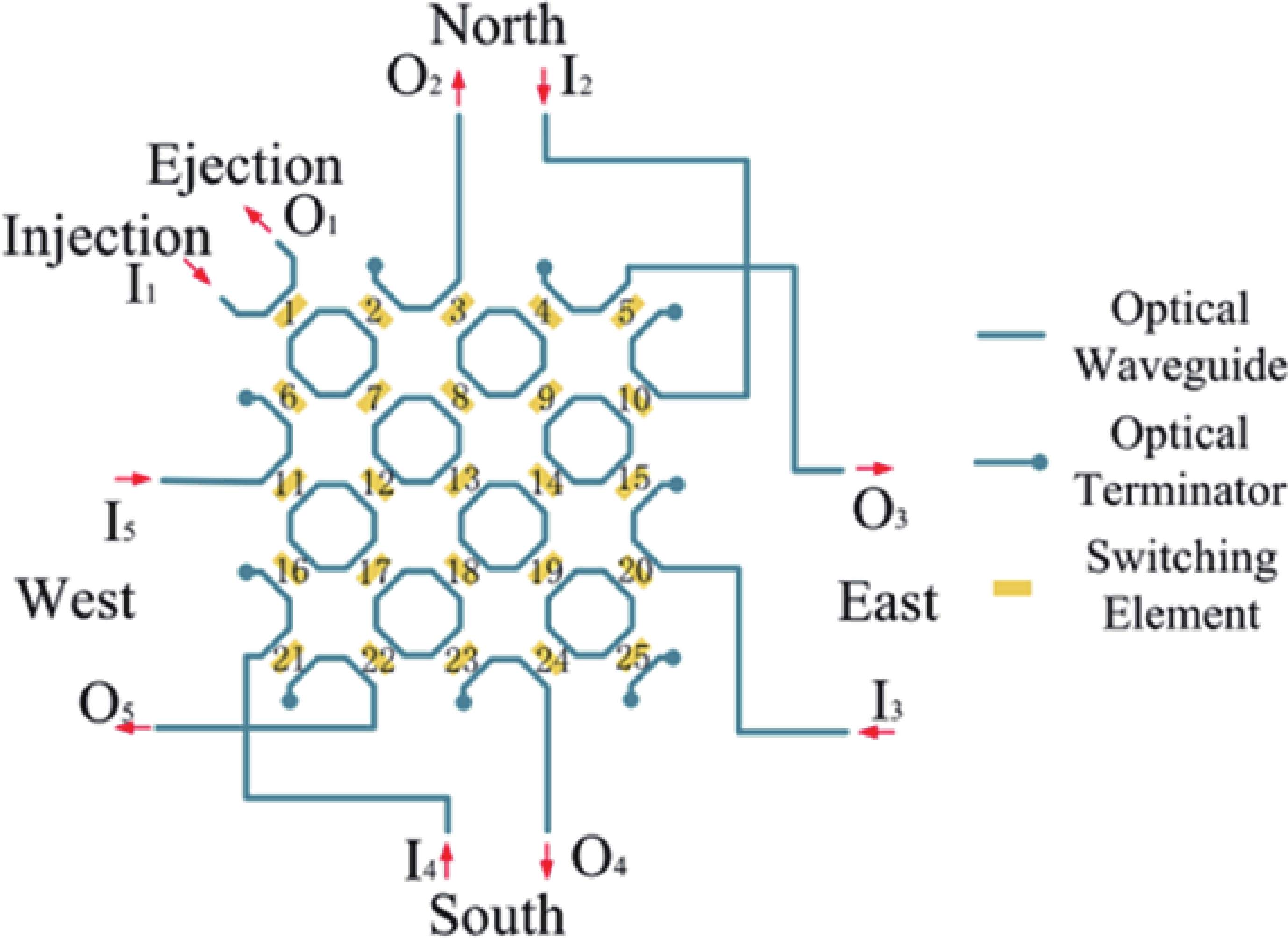

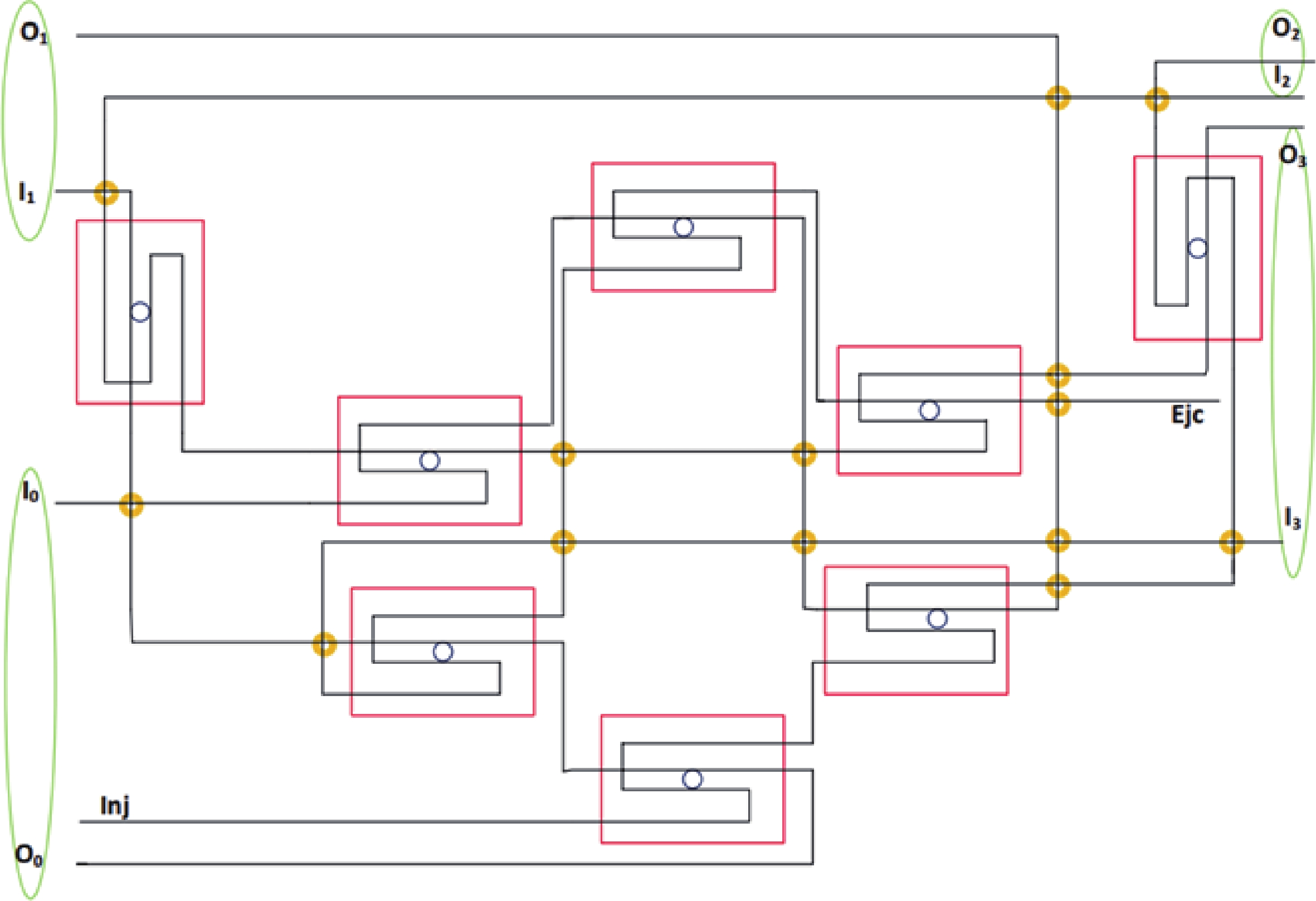

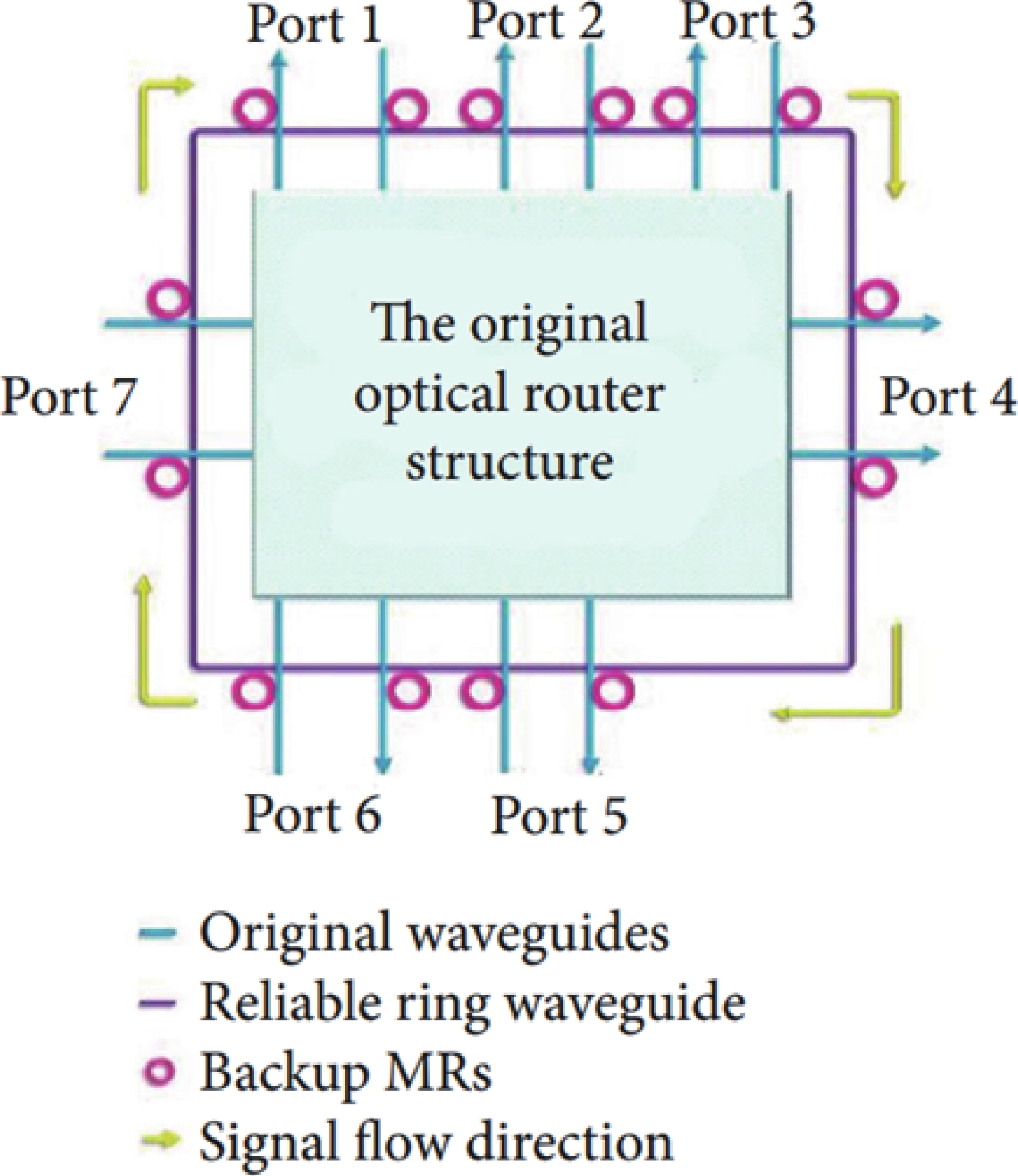

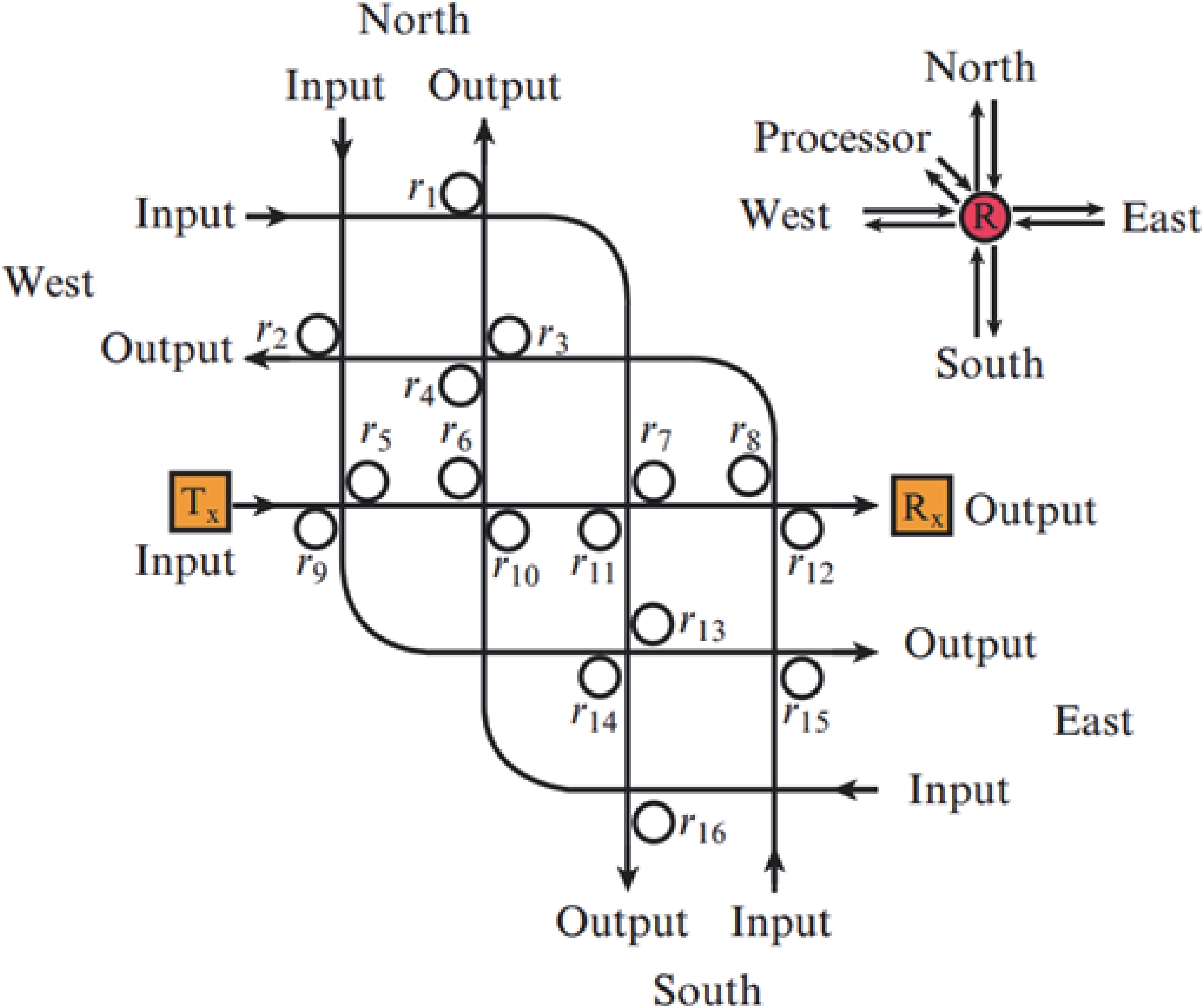

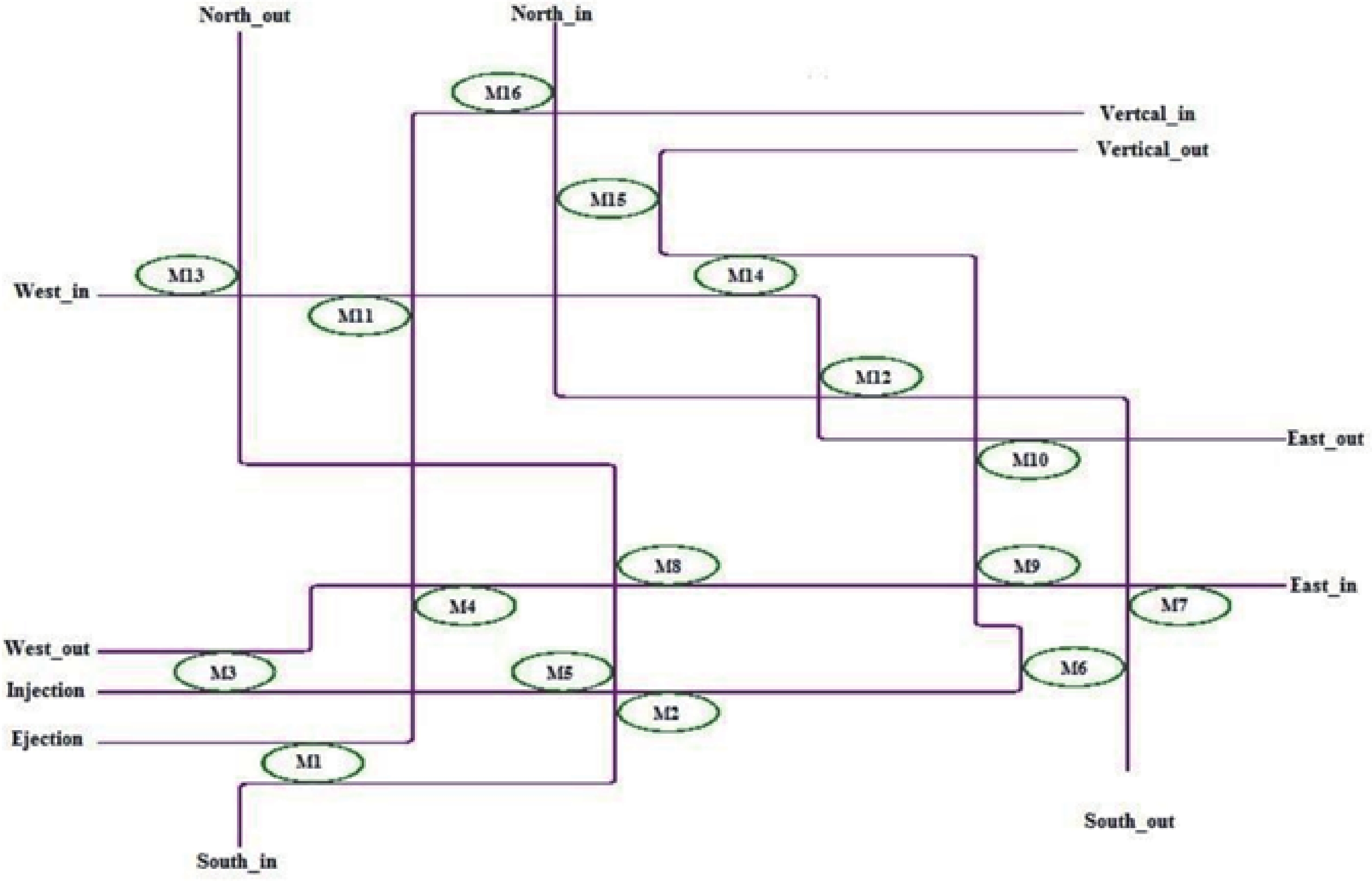

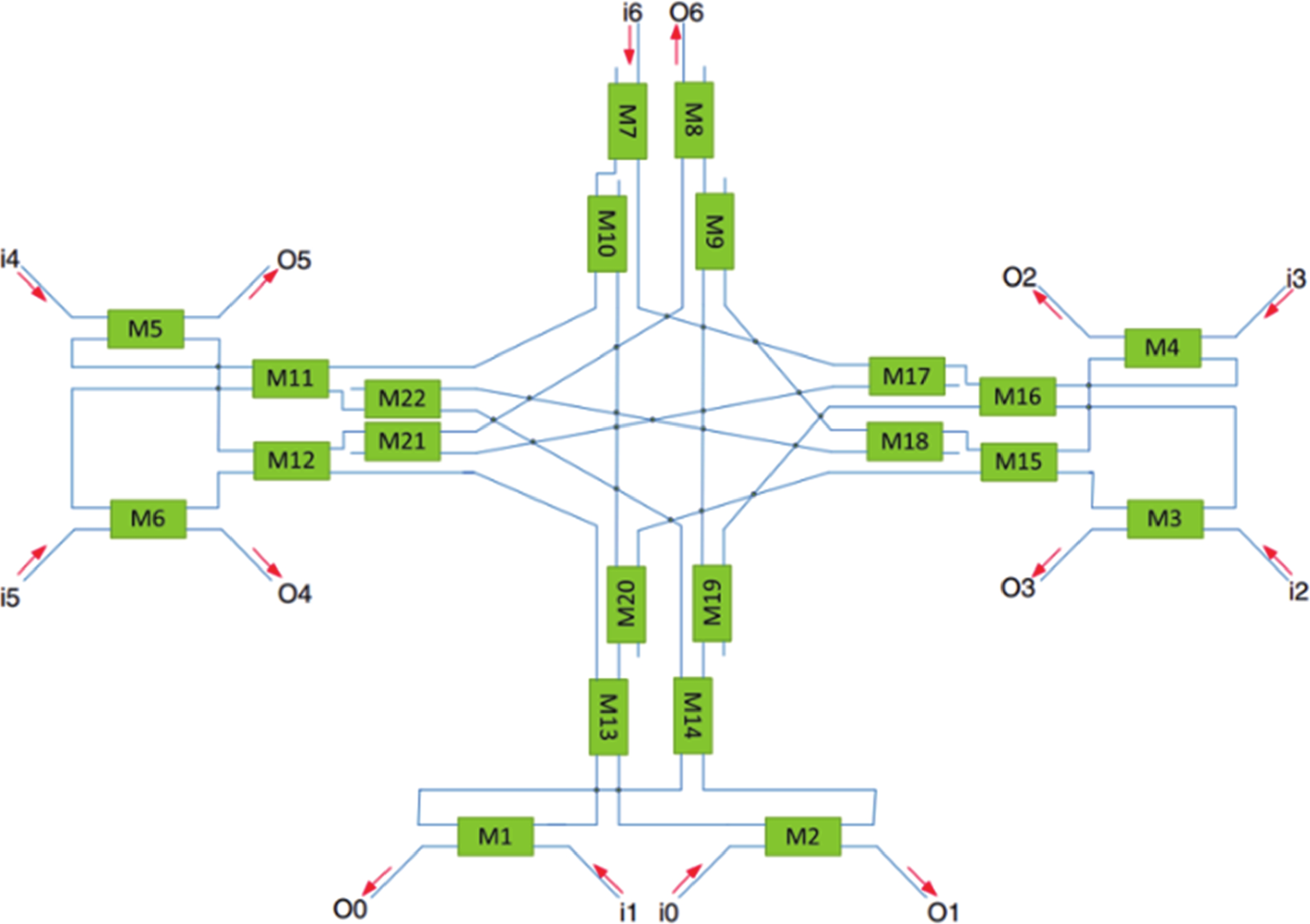

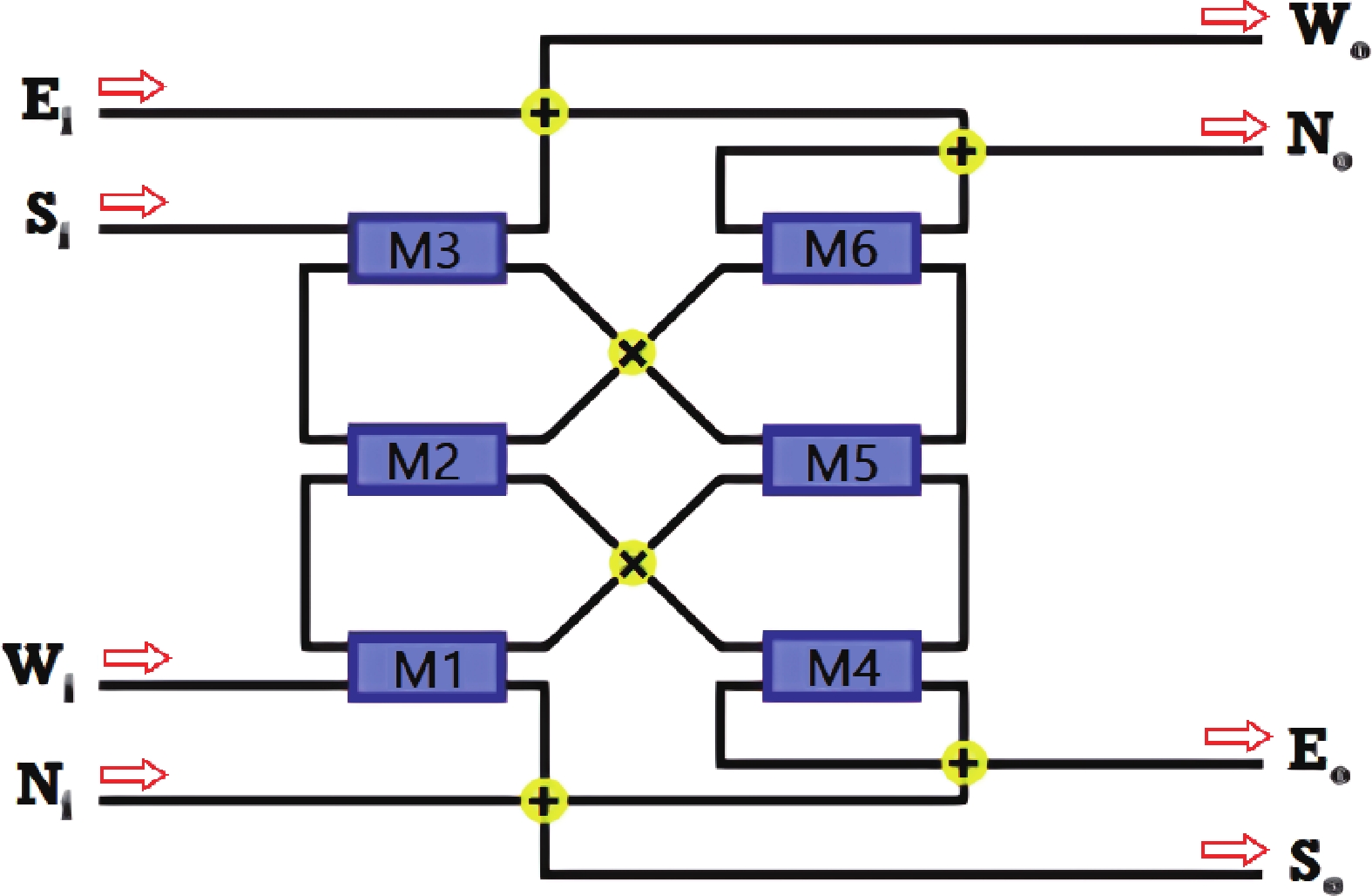

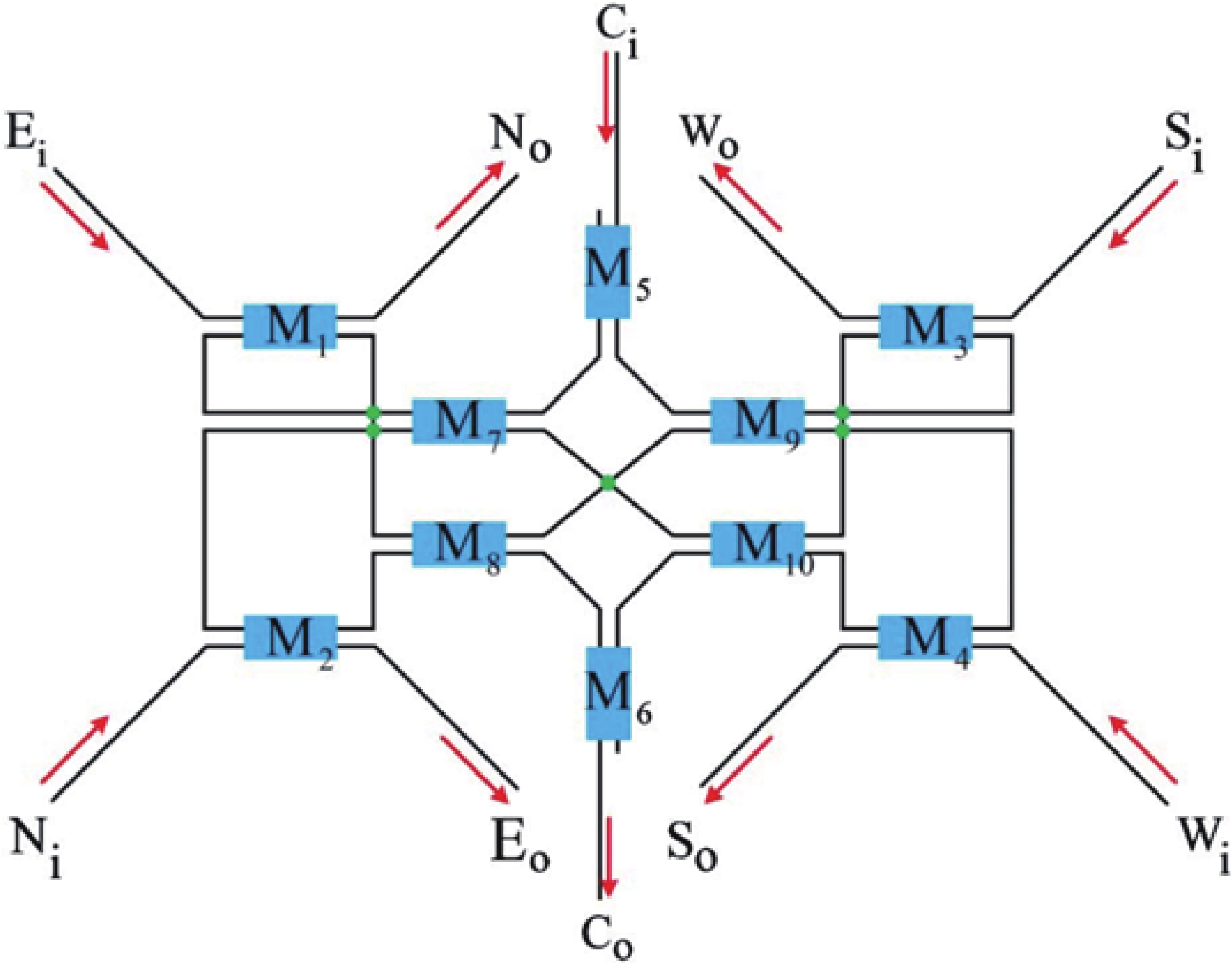

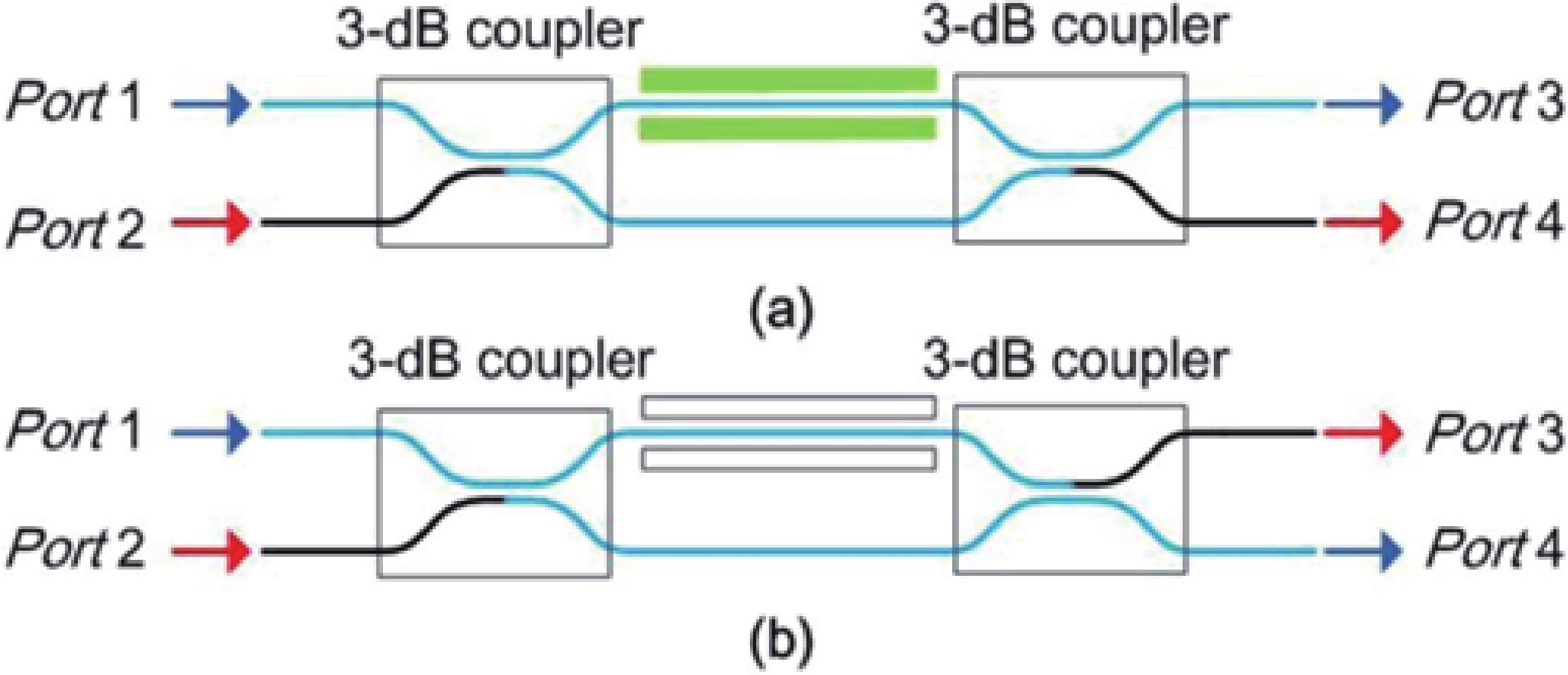

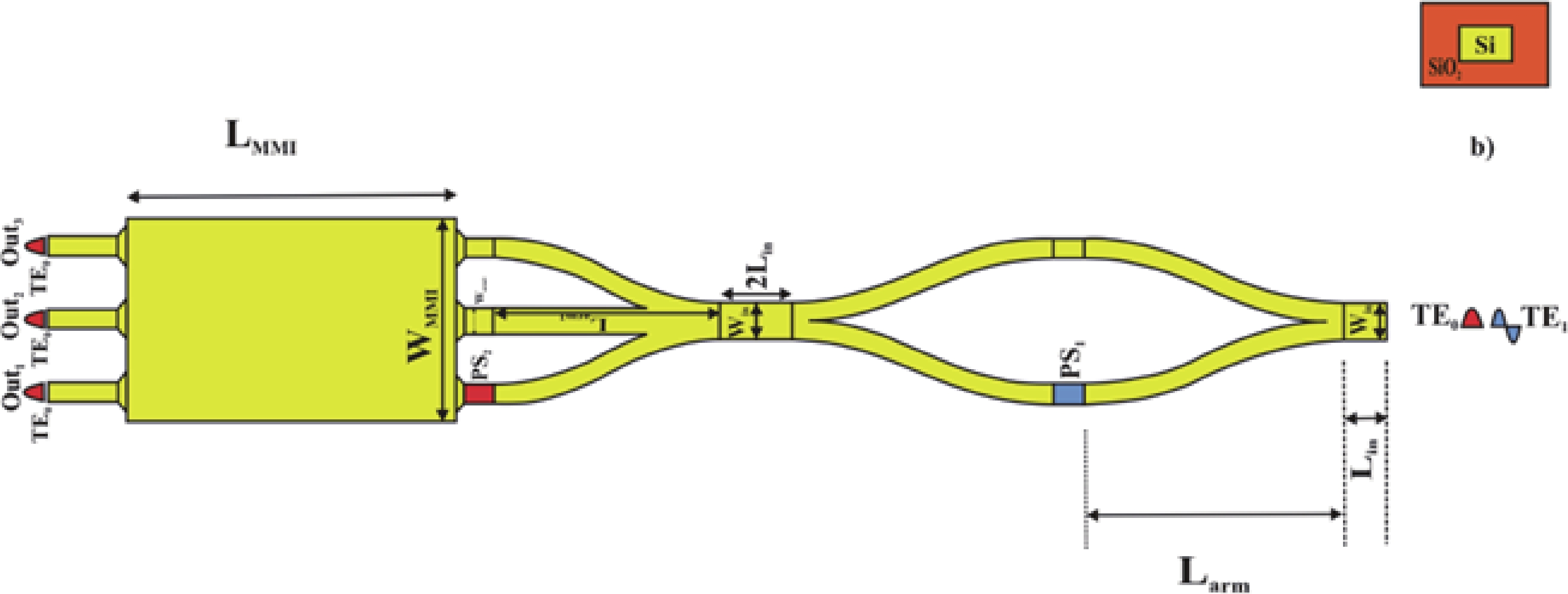

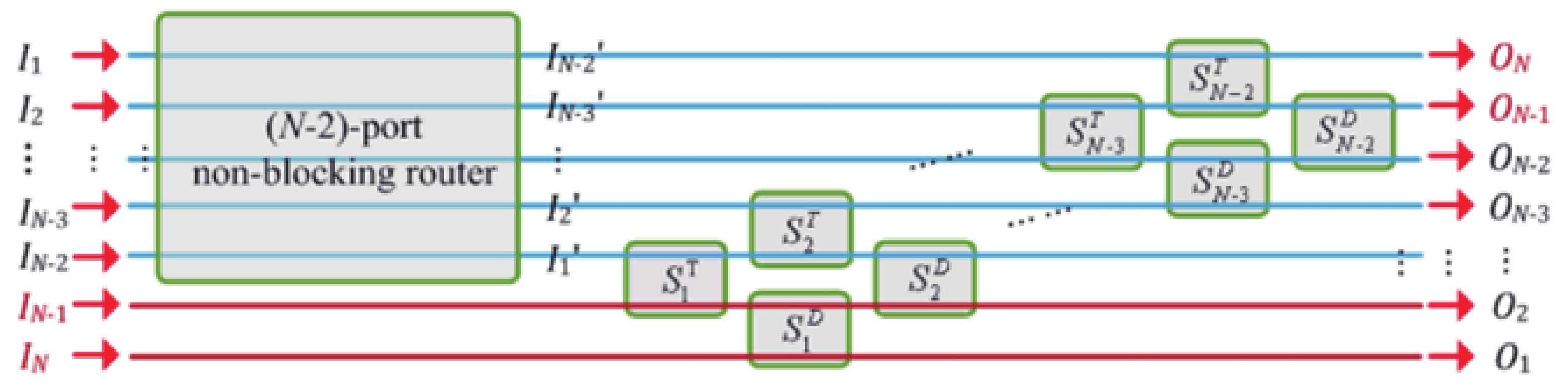

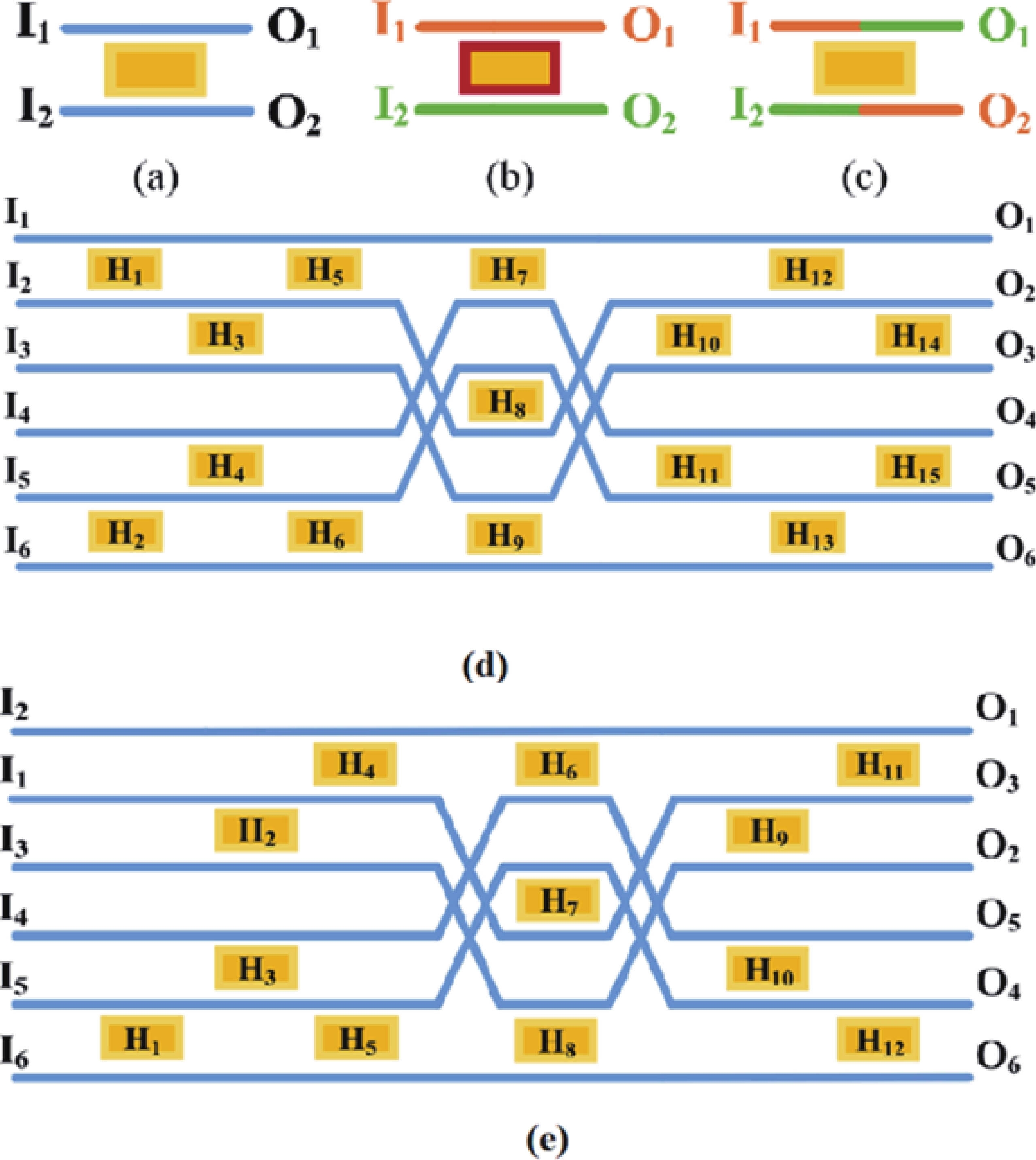

DownLoad: