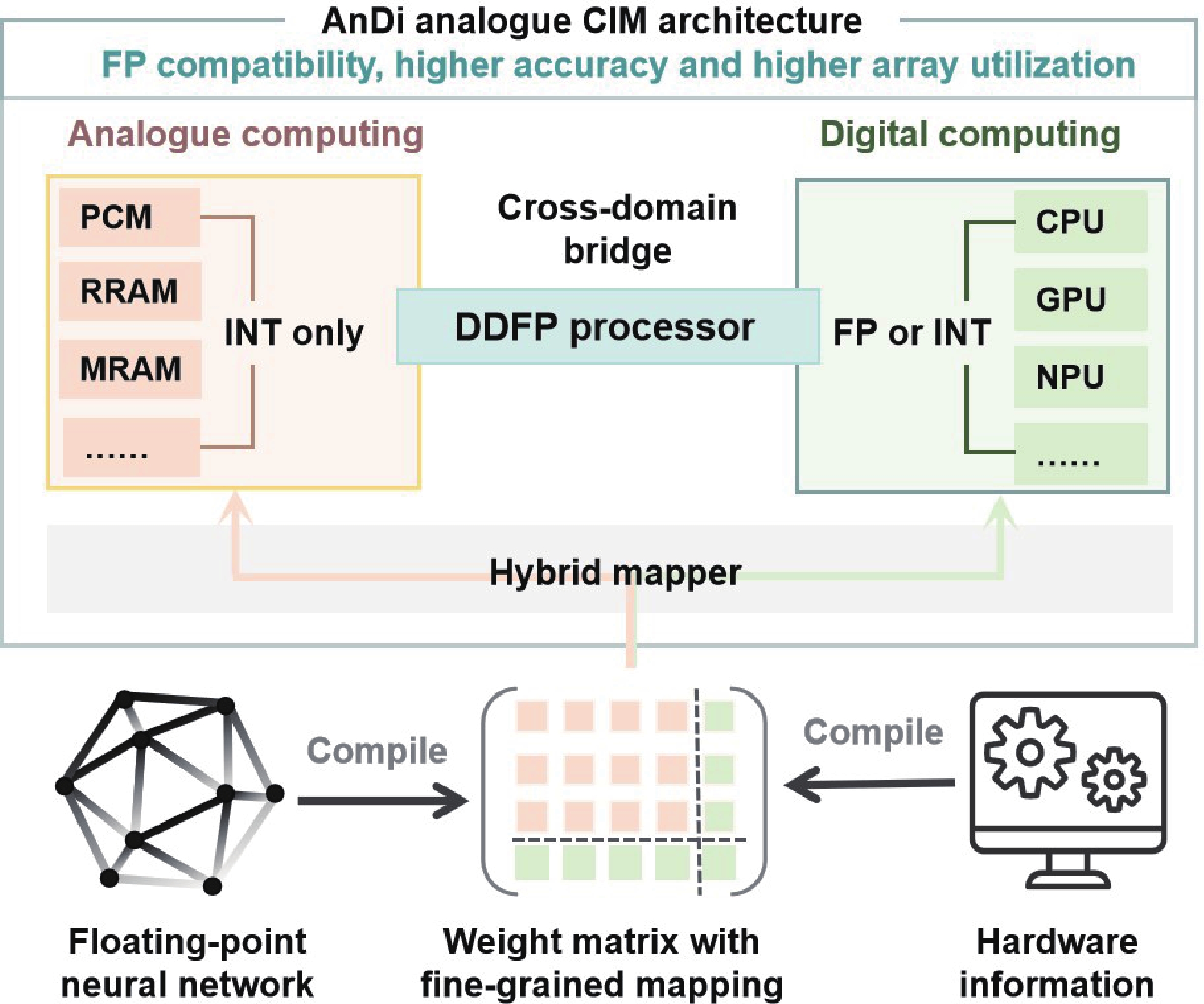

Fig. 1.

(Color online) The AnDi architecture based on a DDFP processor is designed to seamlessly integrate data from both the analogue and digital domains, enabling FP computation[5]. With this architecture, the hybrid mapper has the capability to dynamically allocate matrix multiplication tasks across these domains with fine-grained control at the single row and column level, tailored to the specific requirements of the task. The system outperforms a purely analogue CIM system in terms of floating-point compatibility, precision, and the efficient use of spatial array resources.

| Citation: |

Liang Chu, Wenjun Li. A leap forward in compute-in-memory system for neural network inference[J]. Journal of Semiconductors, 2025, 46(4): 040401. doi: 10.1088/1674-4926/25020028

****

L Chu and W J Li, A leap forward in compute-in-memory system for neural network inference[J]. J. Semicond., 2025, 46(4), 040401 doi: 10.1088/1674-4926/25020028

|

A leap forward in compute-in-memory system for neural network inference

DOI: 10.1088/1674-4926/25020028

CSTR: 32376.14.1674-4926.25020028

More Information-

References

[1] Yao P, Wu H Q, Gao B, et al. Fully hardware-implemented memristor convolutional neural network. Nature, 2020, 577(7792), 641 doi: 10.1038/s41586-020-1942-4[2] Lanza M, Sebastian A, Lu W D, et al. Memristive technologies for data storage, computation, encryption, and radio-frequency communication. Science, 2022, 376(6597), eabj9979 doi: 10.1126/science.abj9979[3] Pi S, Li C, Jiang H, et al. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. Nat Nanotechnol, 2019, 14(1), 35 doi: 10.1038/s41565-018-0302-0[4] Verma N, Jia H Y, Valavi H, et al. In-memory computing: Advances and prospects. IEEE Solid State Circuits Mag, 2019, 11(3), 43 doi: 10.1109/MSSC.2019.2922889[5] Wang Z, Yu R H, Jia Z P, et al. A dual-domain compute-in-memory system for general neural network inference. Nat Electron, 2025 doi: 10.1038/s41928-024-01315-9[6] Park J S, Park C, Kwon S, et al. A multi-mode 8k-MAC HW-utilization-aware neural processing unit with a unified multi-precision datapath in 4-nm flagship mobile SoC. IEEE J Solid State Circuits, 2023, 58(1), 189 doi: 10.1109/JSSC.2022.3205713[7] Chen J, Li J C, Li Y, et al. Multiply accumulate operations in memristor crossbar arrays for analog computing. J Semicond, 2021, 42(1), 013104 doi: 10.1088/1674-4926/42/1/013104[8] Gong J Q, Ji S L, Li J T, et al. Three-dimensional/one-dimensional perovskite heterostructures for stable tri-state synaptic memristors. Sci China Mater, 2024, 67(9), 2848 doi: 10.1007/s40843-024-2981-7[9] De Camaret C, Bourgeois G, Antonelli R, et al. Effects of carbon lateral implantation in Ge-rich GeSbTe phase-change memory. IEEE Electron Device Lett, 2025, 46(3), 385 doi: 10.1109/LED.2025.3531547[10] Chen J G, Wen Z X, Yang F, et al. Refreshable memristor via dynamic allocation of Ferro-ionic phase for neural reuse. Nat Commun, 2025, 16(1), 702 doi: 10.1038/s41467-024-55701-0 -

Proportional views

Liang Chu is a Professor at Hangzhou Dianzi University. He received his Ph.D. of condensed matter physics from Huazhong University of Science and Technology in 2014. From 2014 to 2022, he worked in Nanjing University of Posts and Telecommunications. His research interest focuses on perovskite photovoltaic and synaptic memristors.

Liang Chu is a Professor at Hangzhou Dianzi University. He received his Ph.D. of condensed matter physics from Huazhong University of Science and Technology in 2014. From 2014 to 2022, he worked in Nanjing University of Posts and Telecommunications. His research interest focuses on perovskite photovoltaic and synaptic memristors. Wenjun Li is a Professor and Vice President at Hangzhou Dianzi University, the Director of Zhejiang Province Integrated Circuit and Intelligent Hardware Collaborative Innovation Center, and a Board Member on Education Working Committee of the China Institute of Electronics. He received his Ph.D. in 2004 from Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences. His current research focuses on integrated circuit design, intelligent computing, and hardware systems.

Wenjun Li is a Professor and Vice President at Hangzhou Dianzi University, the Director of Zhejiang Province Integrated Circuit and Intelligent Hardware Collaborative Innovation Center, and a Board Member on Education Working Committee of the China Institute of Electronics. He received his Ph.D. in 2004 from Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences. His current research focuses on integrated circuit design, intelligent computing, and hardware systems.

DownLoad:

DownLoad: