| Citation: |

Hongwei Pan, Siyang Liu, Weifeng Sun. A novel latch-up free SCR-LDMOS with high holding voltage for a power-rail ESD clamp[J]. Journal of Semiconductors, 2013, 34(1): 014007. doi: 10.1088/1674-4926/34/1/014007

****

H W Pan, S Y Liu, W F Sun. A novel latch-up free SCR-LDMOS with high holding voltage for a power-rail ESD clamp[J]. J. Semicond., 2013, 34(1): 014007. doi: 10.1088/1674-4926/34/1/014007.

|

A novel latch-up free SCR-LDMOS with high holding voltage for a power-rail ESD clamp

DOI: 10.1088/1674-4926/34/1/014007

More Information

-

Abstract

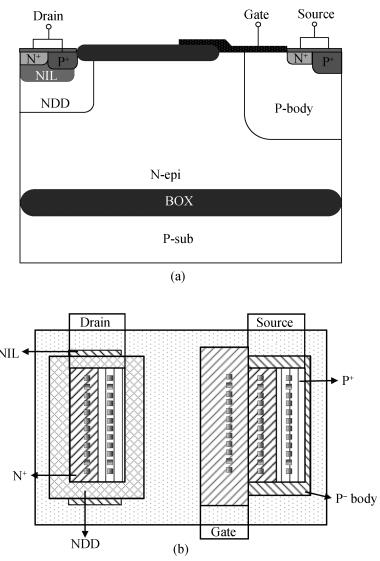

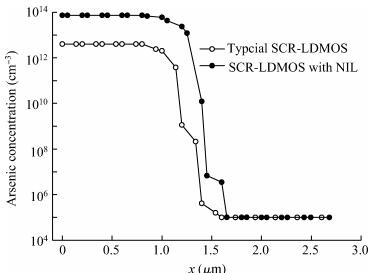

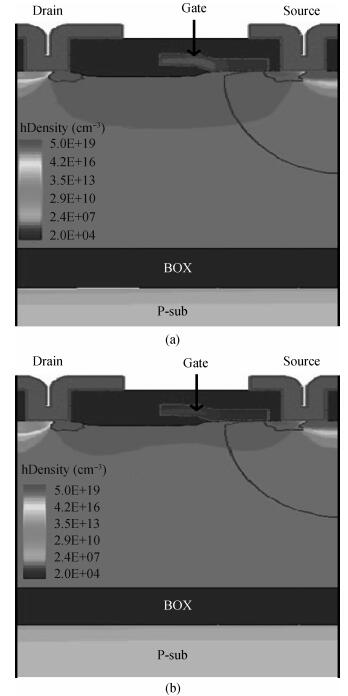

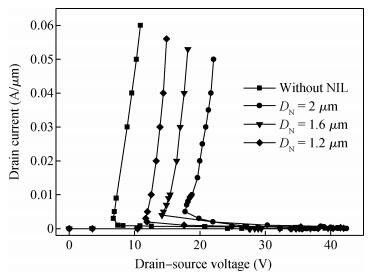

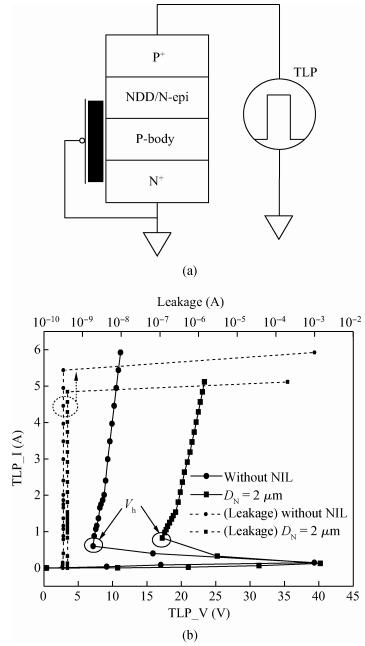

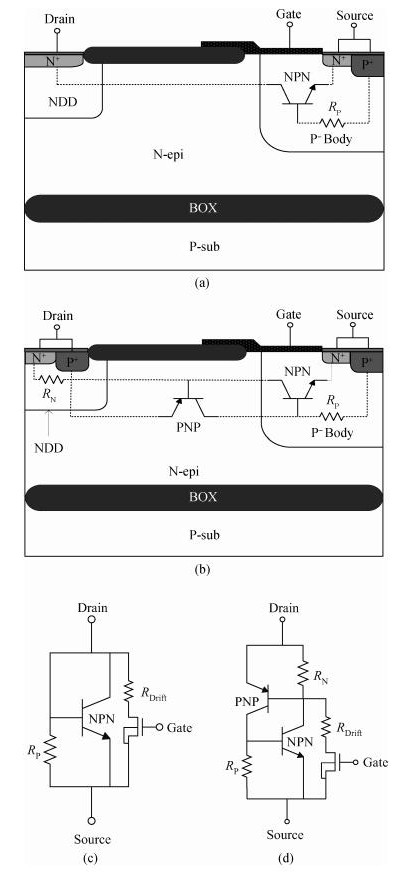

The low snapback holding voltage of the SCR-LDMOS device makes it susceptible to latch-up failure, when used in power-rail ESD (electro-static discharge) clamp circuits. In order to eliminate latch-up risk, this work presents a novel SCR-LDMOS structure with an N-type implantation layer to achieve a 17 V holding voltage and a 5.2 A second breakdown current. The device has been validated using TLP measurement analysis and is applied to a power-rail ESD clamp in half-bridge driver ICs.-

Keywords:

- ESD protection,

- ESD robustness,

- SCR-LDMOS,

- latch-up,

- holding voltage

-

References

[1] Vashchenko V A, Concannon A, Beekter M, et al. High holding voltage cascaded LVTSCR structures for 5.5 V tolerant ESD protection clamps. IEEE Trans Device Mater Reliab, 2004, 4(2):273 doi: 10.1109/TDMR.2004.826584[2] Miao M, Dong S, Li M, et al. Trigger voltage walk-in effect of ESD protection device in HVCMOS. IEEE International Conference on Solid-State and Integrated Circuit Technology, 2010[3] Vashchenko V A, Concannon A, Beek M T, et al. Comparison of ESD protection capability of lateral BJT, SCR and bidirectional SCR for high-voltage BiCMOS circuits. IEEE Bipolar/BiCMOS Circuits and Technology Meeting, 2002[4] Keppens B, Mergens M P J, Cong S T, et al. ESD protection solutions for high voltage technologies. Electrical Overstress/Electrostatic Discharge Symposium, 2004[5] Pendharkar S, Teggatz R, Devore J, et al. SCR-LDMOS——a novel LDMOS device with ESD robustness. International Symposium on Power Semiconductor Devices and ICs, 2000[6] Liu Z, Liou J J, Vinson J. Novel silicon-controlled rectifier (SCR) for high-voltage electrostatic discharge (ESD) applications. IEEE Electron Device Lett, 2008, 29(7):753 doi: 10.1109/LED.2008.923711[7] Meneghesso G, Tazzoli A, Marino F A, et al. Development of a new high holding voltage SCR-based ESD protection structure. IEEE International Reliability Physics Symposium, 2008[8] Chen W Y, Ker M D. Improving safe operating area of nLDMOS array with embedded silicon controlled rectifier for ESD protection in a 24-V BCD process. IEEE Trans Electron Devices, 2011, 58(9):2944 doi: 10.1109/TED.2011.2159861[9] Ker M D, Lin K H. The impact of low-holding-voltage issue in high-voltage CMOS technology and the design of latch-free power-rail ESD clamp circuit for LCD driver ICs. IEEE J Solid-State Circuits, 2005, 40(8):1751 doi: 10.1109/JSSC.2005.852046[10] Gendron A, Salamero C. Area-efficient, reduced and no-snapback PNP-based ESD protection in advanced smart power technology. Electrical Overstress/Electrostatic Discharge Symposium, 2006[11] Lin K H, Ker M D. Design on latchup-free power-rail ESD clamp circuit in high-voltage CMOS ICs. Electrical Overstress/Electrostatic Discharge Symposium, 2004 -

Proportional views

DownLoad:

DownLoad: