| Citation: |

Long Cheng, Yu Zhu, Kai Zhu, Chixiao Chen, Junyan Ren. Robust design of a 500-MS/s 10-bit triple-channel current-steering DAC in 40 nm CMOS[J]. Journal of Semiconductors, 2013, 34(10): 105007. doi: 10.1088/1674-4926/34/10/105007

****

L Cheng, Y Zhu, K Zhu, C X Chen, J Y Ren. Robust design of a 500-MS/s 10-bit triple-channel current-steering DAC in 40 nm CMOS[J]. J. Semicond., 2013, 34(10): 105007. doi: 10.1088/1674-4926/34/10/105007.

|

Robust design of a 500-MS/s 10-bit triple-channel current-steering DAC in 40 nm CMOS

DOI: 10.1088/1674-4926/34/10/105007

More Information

-

Abstract

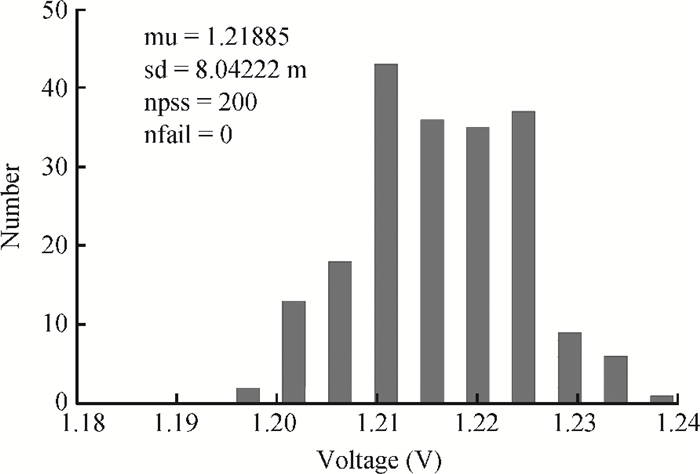

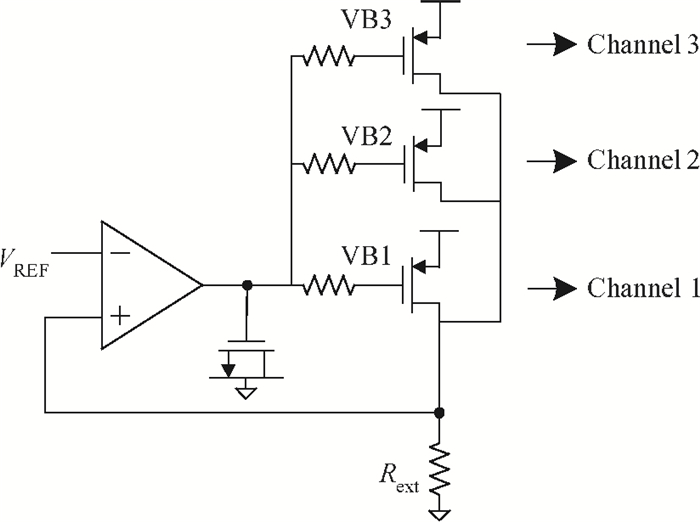

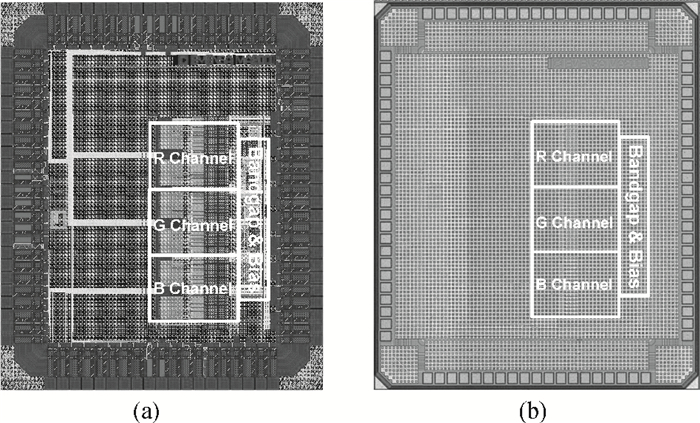

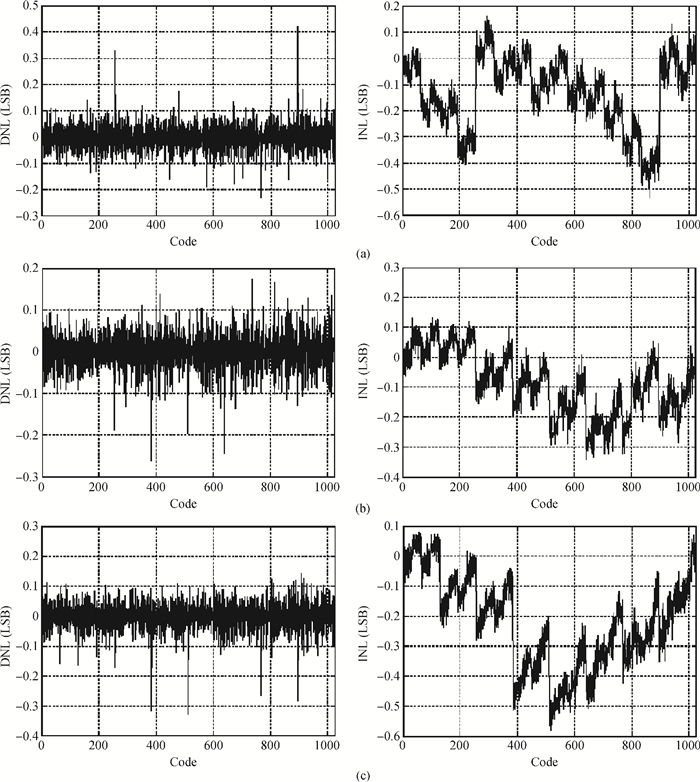

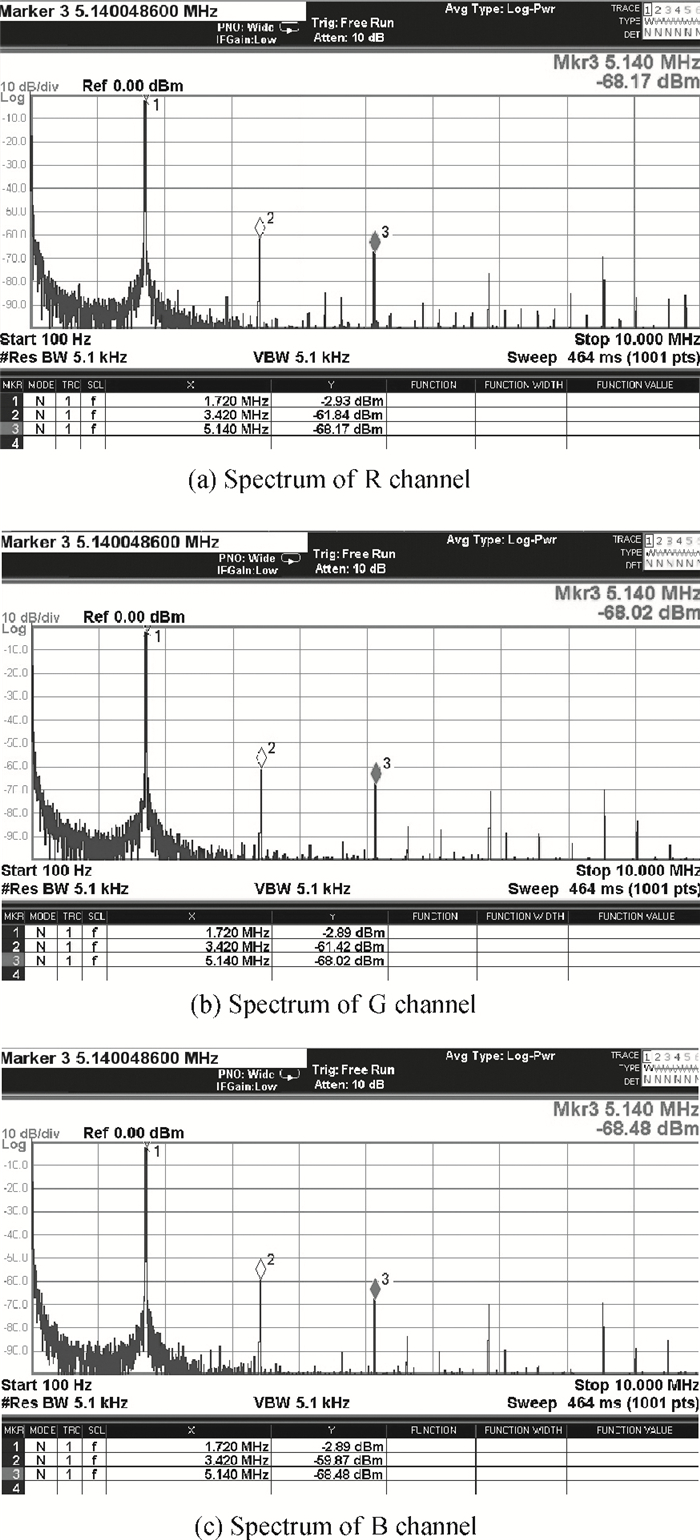

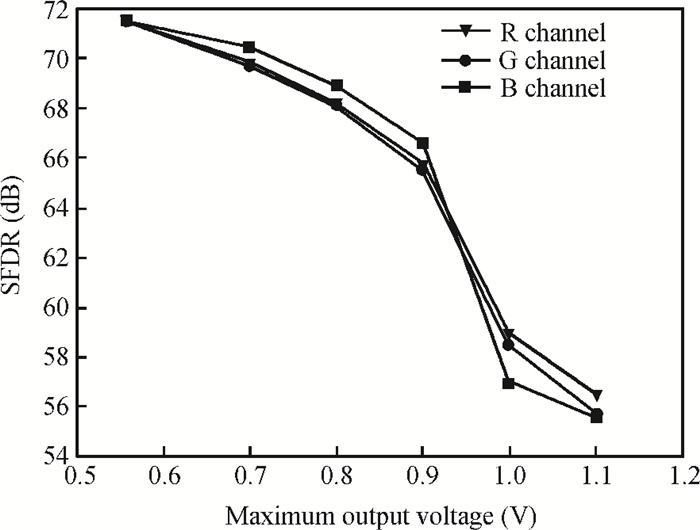

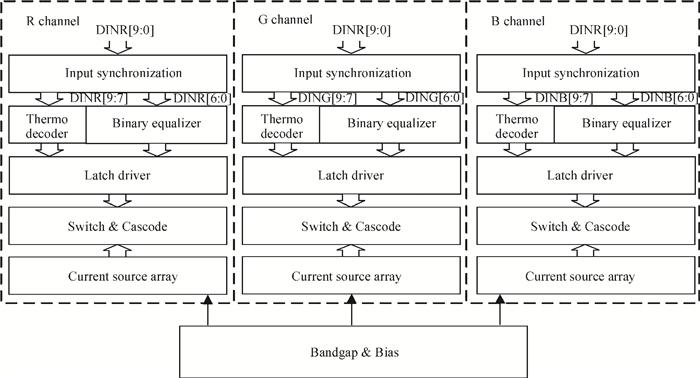

A 500-MS/s 10-bit triple-channel current-steering DAC in 40 nm 1P8M CMOS advanced technology is proposed. The central symmetry random walk scheme is applied for current source arrays to avoid mismatching effects in nano-CMOS design. The high-speed latch drivers can be self-adaptively connected to switches in different voltage domains. The experimental data shows that the maximum DNL and INL are 0.42 LSB and 0.58 LSB. The measured SFDR at 1.7 MHz output signal is 58.91 dB, 58.53 dB and 56.98 dB for R/G/B channels, respectively. The DAC has good static and dynamic performance despite the single-ended output. The average rising time and falling time of three channels are 0.674 ns and 0.807 ns. The analog/digital power supply is 3.3 V/1.1 V. This triple-channel DAC occupies 0.5656 mm2.-

Keywords:

- DAC,

- triple-channel,

- digital-to-analog,

- high speed,

- 40 nm CMOS,

- video DAC

-

References

[1] Cheng Y. Design for manufacturing (DFM) in nano-CMOS era.IEEE International Nanoelectronics Conference, 2008:524 http://ieeexplore.ieee.org/document/4585541/[2] Bastos J, Marques A M, Steyaert M S J, et al. A 12-bit intrinsic accuracy high-speed CMOS DAC. IEEE J Solid-State Circuits, 1998, 33(12):1959 doi: 10.1109/4.735536[3] Plas G, Vandenbussche J, Sansen W, et al. A 14-bit intrinsic accuracy Q2 random walk CMOS DAC. IEEE J Solid-State Circuits, 1999, 34(12):1708 doi: 10.1109/4.808896[4] Luschas S, Lee H S. Output impedance requirements for DACs. IEEE ISCAS, 2003:861 http://ieeexplore.ieee.org/document/1205700/?arnumber=1205700[5] Chen T, Gielen G G E. The analysis and improvement of a current-steering DACs dynamic SFDR-I:the cell-dependent delay differences. IEEE Trans Circuits Syst Ⅰ, 2006, 53(1):3 http://ieeexplore.ieee.org/document/01576881/[6] Cheng L, Lin Y, Ye F, et al. Output-dependent delay cancellation technique for high-accuracy current-steering DACs. IEEE ISCAS, 2012:2729 http://ieeexplore.ieee.org/document/6271872/[7] Palmers P, Steyaert M S J. A 10-bit 1.6-GS/s 27-mW current-steering D/A converter with 550-MHz 54-dB SFDR bandwidth in 130-nm CMOS. IEEE Trans Circuits Syst Ⅰ, 2010, 57(11):2870 doi: 10.1109/TCSI.2010.2052491[8] Mercer D A. Low-power approaches to high-speed current-steering digital-to-analog converters in 0.18-μm CMOS. IEEE J Solid-State Circuits, 2007, 42(8):1688 doi: 10.1109/JSSC.2007.900279[9] Tesch B J, Pratt P M, Bacrania K, et al. A 14-b, 125 MSPS digital-to-analog converter and bandgap voltage reference in 0.5μm CMOS. IEEE ISCAS, 1999:452[10] Lewyn L L, Ytterdal T, Wulff C, et al. Analog circuit design in nanoscale CMOS technologies. Proc IEEE, 97(10):1687 doi: 10.1109/JPROC.2009.2024663[11] Analog Device. Data Sheet: ADV7123 CMOS, 330 MHz, triple 10-bit high speed video DAC. 2010[12] Chou W S, Yang S C, Hsueh F L, et al. A low-cost triple-channel 10-bit 250 MHz DAC IP in 65 nm CMOS process. IEEE ISCAS, 2007:3594[13] Zhao Q, Li R, Qiu D, et al. A 14-bit 1-GS/s DAC with a programmable interpolation filter in 65 nm CMOS. Journal of Semiconductors, 2013, 34(2):025004 doi: 10.1088/1674-4926/34/2/025004 -

Proportional views

DownLoad:

DownLoad: