| Citation: |

Jin Wu, Jianwu Chen, Danyu Wu, Lei Zhou, Fan Jiang, Zhi Jin, Xinyu Liu. A 4 GHz 32 bit direct digital frequency synthesizer based on a novel architecture[J]. Journal of Semiconductors, 2013, 34(11): 115007. doi: 10.1088/1674-4926/34/11/115007

****

J Wu, J W Chen, D Y Wu, L Zhou, F Jiang, Z Jin, X Y Liu. A 4 GHz 32 bit direct digital frequency synthesizer based on a novel architecture[J]. J. Semicond., 2013, 34(11): 115007. doi: 10.1088/1674-4926/34/11/115007.

|

A 4 GHz 32 bit direct digital frequency synthesizer based on a novel architecture

DOI: 10.1088/1674-4926/34/11/115007

More Information

-

Abstract

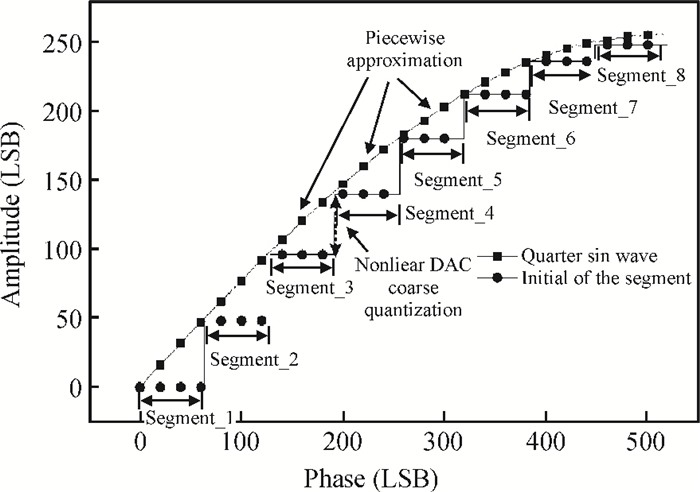

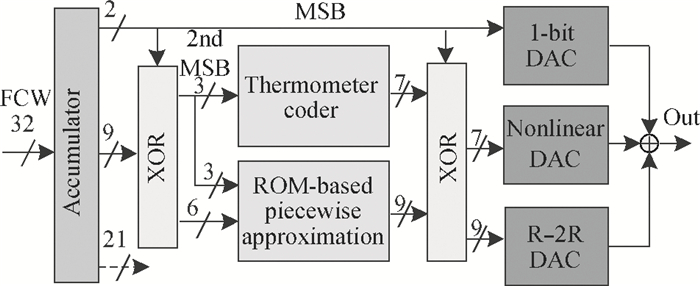

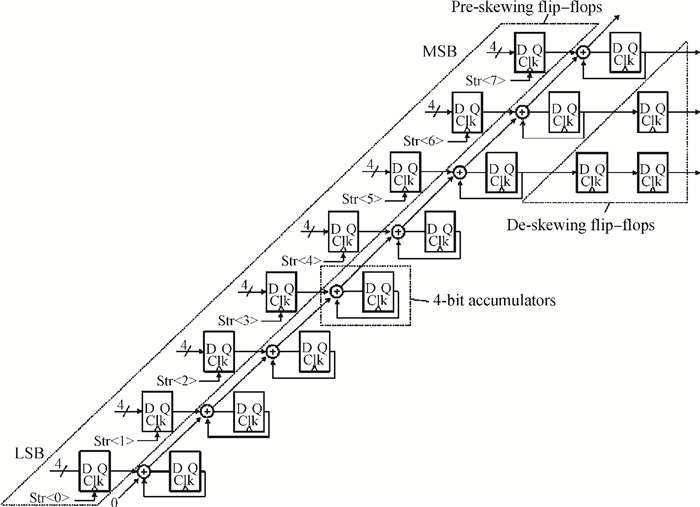

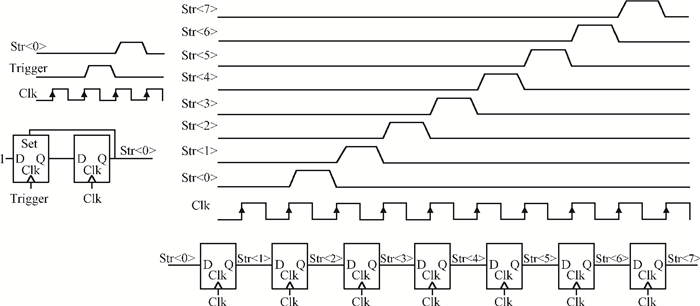

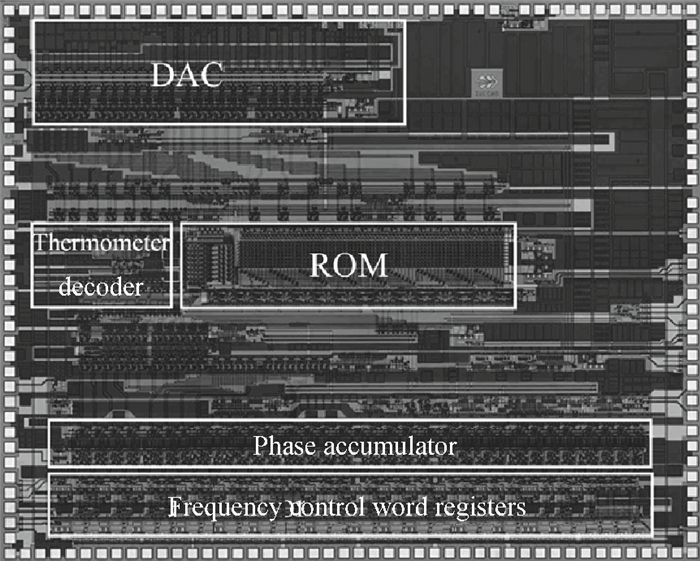

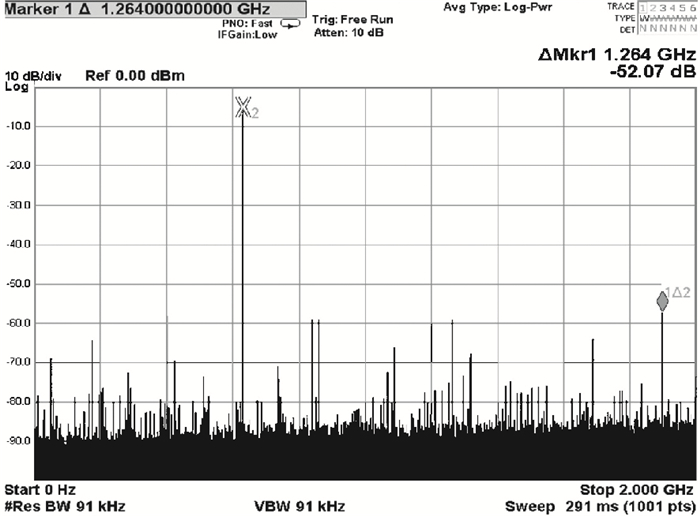

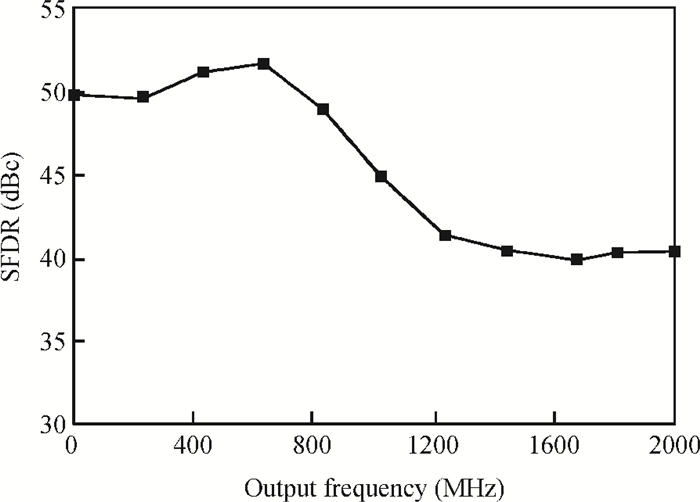

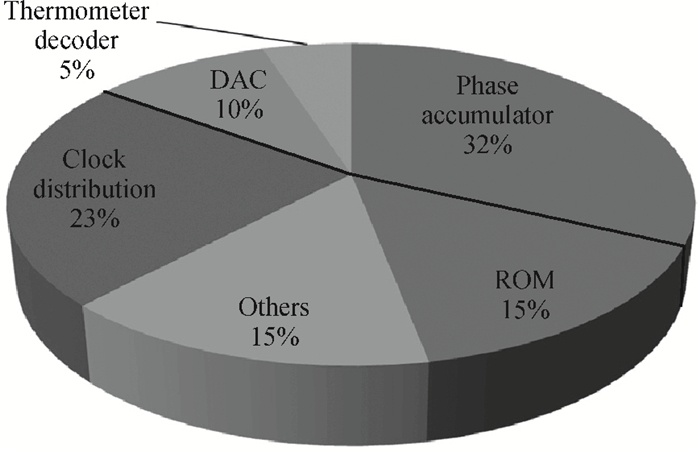

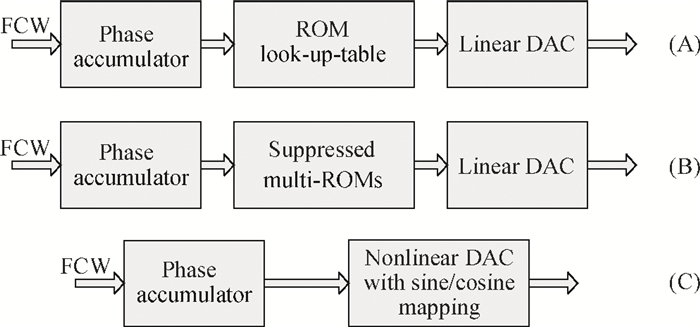

This paper presents a novel direct digital frequency synthesizer (DDFS) architecture based on nonlinear DAC coarse quantization and the ROM-based piecewise approximation method, which has the advantages of high speed, low power and low hardware resources. By subdividing the sinusoid into a collection of phase segments, the same initial value of each segment is realized by a nonlinear DAC. The ROM is decomposed with a coarse ROM and fine ROM using the piecewise approximation method. Then, the coarse ROM stores the offsets between the initial value of the common segment and the initial value of each line in the same segment. Meanwhile, the fine ROM stores the differences between the line values and the initial value of each line. A ROM compression ratio of 32 can be achieved in the case of 11 bit phase and 9 bit amplitude. Based on the above method, a prototype chip was fabricated using 1.4 μm GaAs HBT technology. The measurement shows an average spurious-free dynamic range (SFDR) of 45 dBc, with the worst SFDR only 40.07 dBc at a 4.0 GHz clock. The chip area is 4.6×3.7 mm2 and it consumes 7 W from a -4.9 V power supply. -

References

[1] Yang B D, Choi J H, Han S H, et al. An 800-MHz low-power direct digital frequency synthesizer with an on-chip D/A converter. IEEE J Solid-State Circuits, 2004, 39(5):761 doi: 10.1109/JSSC.2004.826323[2] Turner S E, Chan R T, Feng J T. ROM-based direct digital synthesizer at 24 GHz clock frequency in InP DHBT technology. IEEE Microw Wireless Compon Lett, 2008, 18(8):566 doi: 10.1109/LMWC.2008.2001025[3] Turner S E, Kotecki D E. Direct digital synthesizer with sinusoidal-weighted DAC at 32-GHz clock frequency in InP DHBT technology. IEEE J Solid-State Circuits, 2006, 41(10):2284 doi: 10.1109/JSSC.2006.881552[4] Geng X, Dai F F, Irwin J D, et al. An 11-bit 8.6 GHz direct digital synthesizer MMIC with 10-bit segmented sinusoidal-weighted DAC. IEEE J Solid-State Circuits, 2010, 45(2):300 doi: 10.1109/JSSC.2009.2037542[5] Baek K H, Merlo E, Choe M J, et al. A 1.7 GHz 3 V direct digital frequency synthesizer with an on-chip DAC in 0.35μm SiGe BiCMOS. IEEE ISSCC Dig of Tech Papers, San Francisco, CA, 2005:114[6] Urteaga M, Pierson R, Rowell P, et al. Advanced InP DHBT process for high speed LSI circuits. IEEE ICIPRM, Versailles, France, 2008:1 http://ieeexplore.ieee.org/document/4703058/?reload=true&arnumber=4703058[7] Thuries S, Tournier E, Cathelin A, et al. A 6-GHz low-power BiCMOS SiGe:C 0.25μm direct digital synthesizer. IEEE Microw Wireless Compon Lett, 2008, 18(1):46 doi: 10.1109/LMWC.2007.911994[8] Laemmle B, Wagner C, Knapp H, et al. A differential pair-based direct digital synthesizer MMIC with 16.8-GHz clock and 488-mW power consumption. IEEE Trans Microw Theory and Tech, 2010, 58(5):1375 doi: 10.1109/TMTT.2010.2042860[9] Strollo A G M, De Caro D, Petra N. A 630 MHz, 76 mW direct digital frequency synthesizer using enhanced ROM compression technique. IEEE J Solid-State Circuits, 2007, 42(2):350 doi: 10.1109/JSSC.2006.889382[10] De Caro D, Petra N, Strollo A G M. Reducing look-up tablesize in direct digital frequency synthesizers using optimized multipartite table method. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2008, 55(7):2116 doi: 10.1109/TCSI.2008.918008[11] Kang C Y, Swartzlander Jr E E. Digit-pipelined direct digital frequency synthesis based on differential CORDIC. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2006, 53(5):1035 doi: 10.1109/TCSI.2005.862183[12] Madisetti A, Kwentus A Y, Willson A N Jr. A 100-MHz, 16-b, direct digital frequency synthesizer with a 100-dBc spuriousfree dynamic range. IEEE J Solid-State Circuits, 1999, 34(8):1034 doi: 10.1109/4.777100[13] De Caro D, Napoli E, Strollo A G M. Direct digital frequency synthesizers with polynomial hyperfolding technique. IEEE Trans Circuits Syst Ⅱ, Exp Briefs, 2004, 51(7):337 doi: 10.1109/TCSII.2004.829553[14] Curticapean F, Niittylahti J. Direct digital frequency synthesizers of high spectral purity based on quadratic approximation. Proc IEEE Int Conf Electron Circuits Syst, Dubrovnik, 2002, 3:1095 doi: 10.1109/ICECS.2002.1046442[15] Ashrafi A, Adhami R, Milenkovic A. A direct digital frequency synthesizer based on the quasi-linear interpolation method. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2010, 57(4):863 doi: 10.1109/TCSI.2009.2027645[16] Langlois J M P, Al-Khalili D. Low power direct digital frequency synthesizers in 0.18-μm CMOS. Proc Custom Integr Circuits Conf, San Jose, CA, 2003:283[17] Yeoh H C, Jung J H, Jung Y H, et al. A 1.3-GHz 350-mW hybrid direct digital frequency synthesizer in 90-nm CMOS. IEEE J Solid-State Circuits, 2010, 45(9):1845 doi: 10.1109/JSSC.2010.2056830[18] Nicholas H T, Samueli H. A 150-MHz direct digital frequency synthesizer in 1.25-μm CMOS with -90-dBc spurious performance. IEEE J Solid-State Circuits, 1991, 26(12):1959 doi: 10.1109/4.104190[19] Chen J W, Wu D Y, Zhou L, et al. 5.3-GHz 32-bit accumulator designed for direct digital frequency sythesizer. Chinese Science Bulletin, 2012, 57(19):2480 doi: 10.1007/s11434-012-5157-4[20] Bellaouar A, O'Brecht M S, Fahim A M, et al. Low-power direct digital frequency synthesis for wireless communications. IEEE J Solid-State Circuits, 2000, 35(3):385 doi: 10.1109/4.826821 -

Proportional views

DownLoad:

DownLoad: