| Citation: |

Jamshid Sangirov, Ikechi Augustine Ukaegbu, Gulomjon Sangirov, Tae-Woo Lee, Hyo-Hoon Park. Power-aware transceiver design for half-duplex bidirectional chip-to-chip optical interconnects[J]. Journal of Semiconductors, 2013, 34(12): 125001. doi: 10.1088/1674-4926/34/12/125001

****

J Sangirov, I A Ukaegbu, G Sangirov, T W Lee, H H Park. Power-aware transceiver design for half-duplex bidirectional chip-to-chip optical interconnects[J]. J. Semicond., 2013, 34(12): 125001. doi: 10.1088/1674-4926/34/12/125001.

|

Power-aware transceiver design for half-duplex bidirectional chip-to-chip optical interconnects

DOI: 10.1088/1674-4926/34/12/125001

More Information

-

Abstract

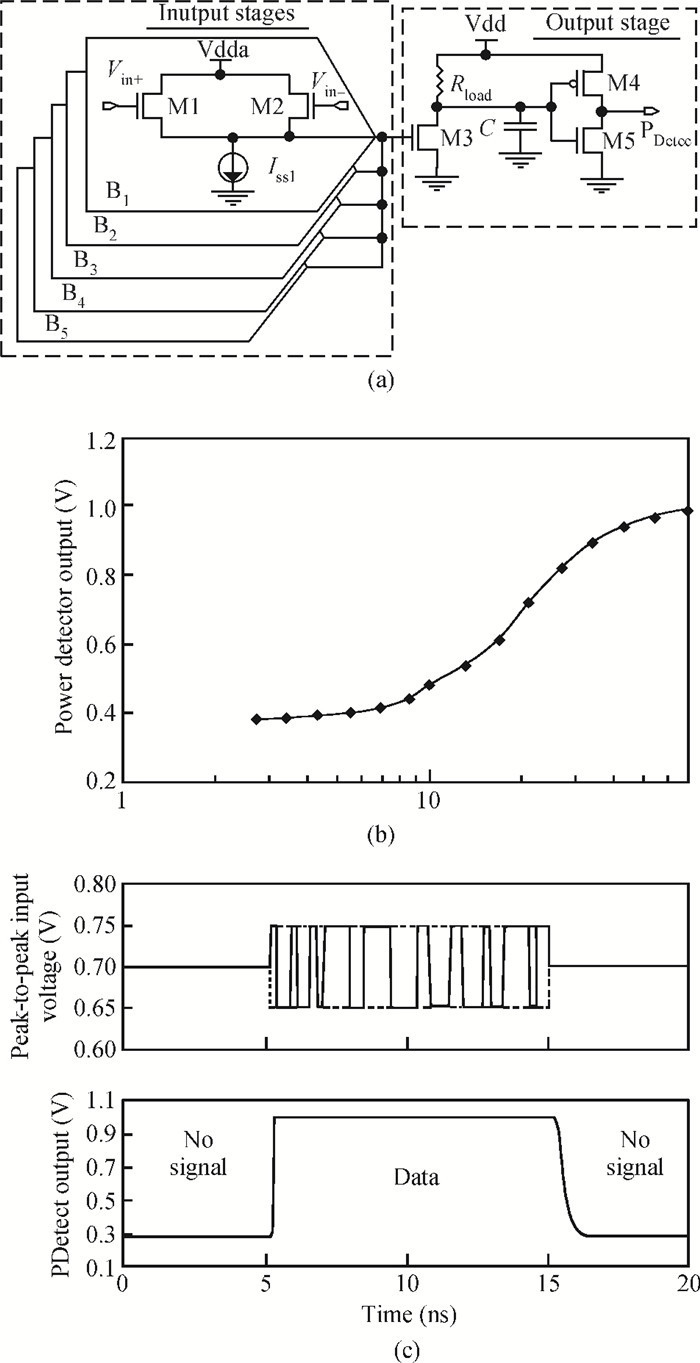

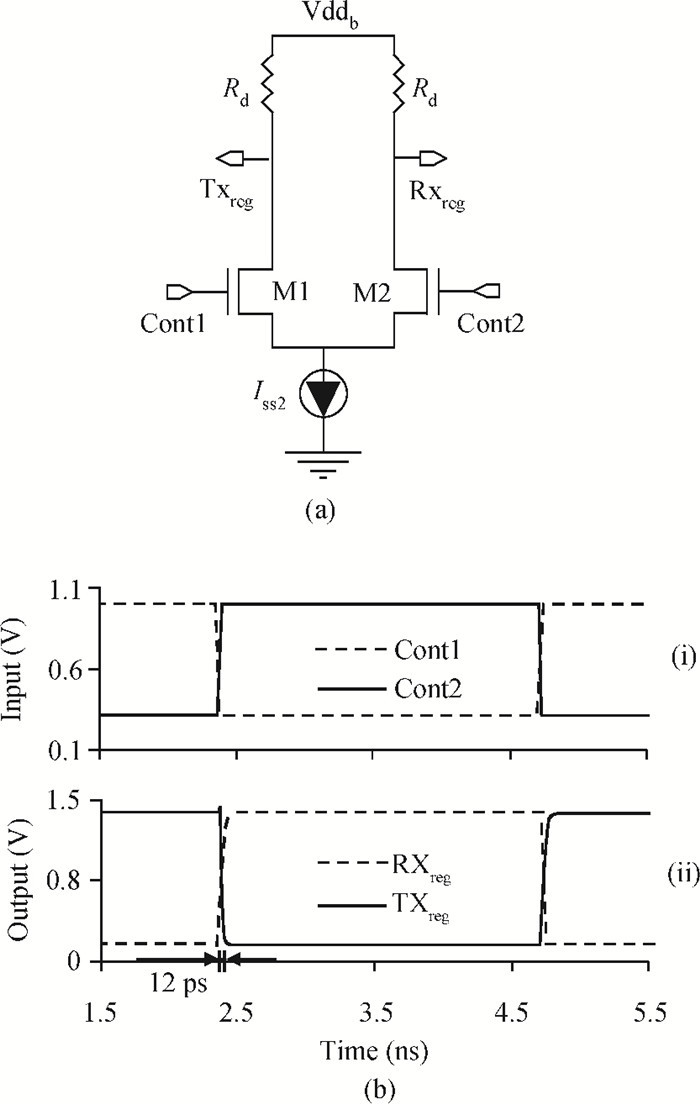

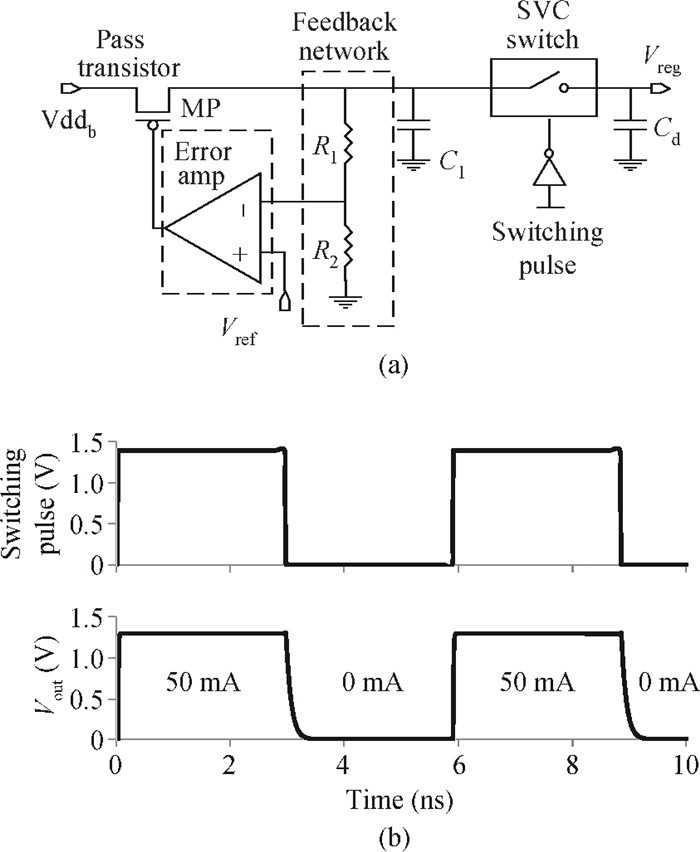

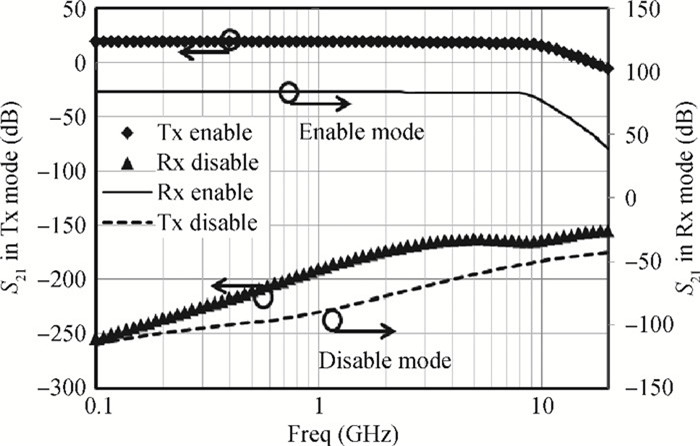

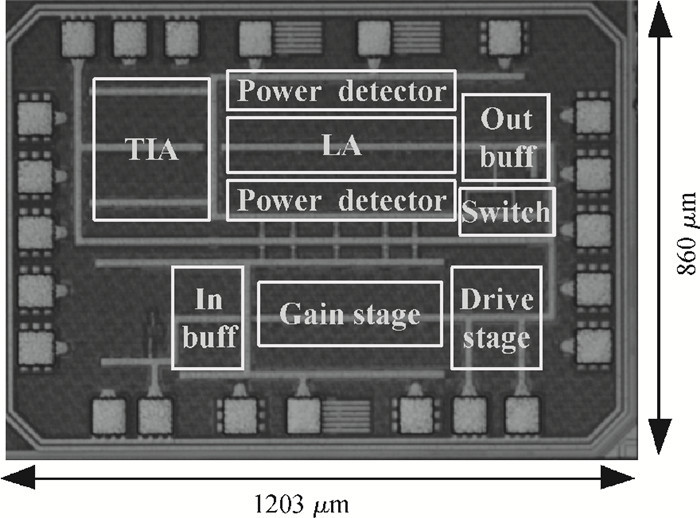

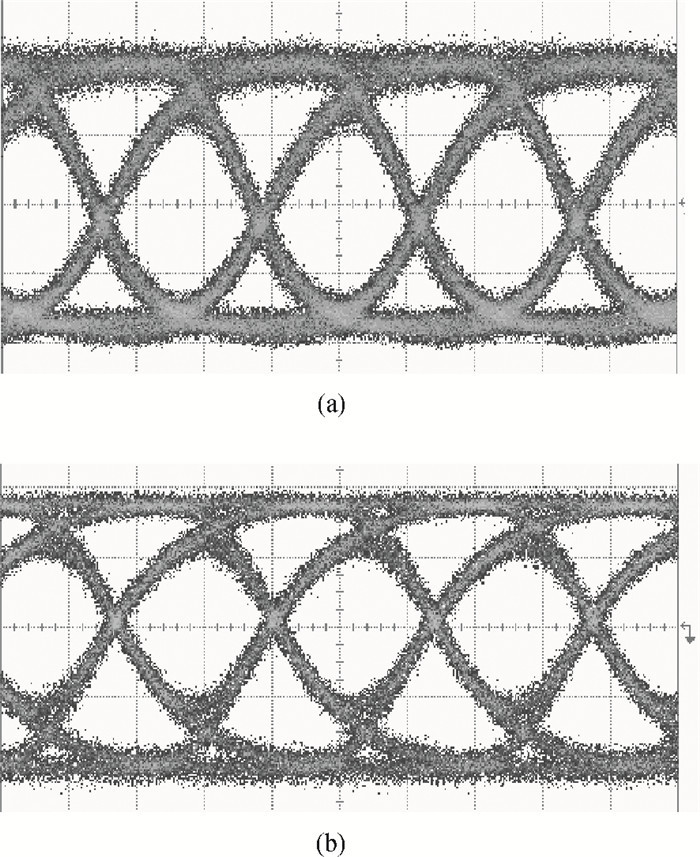

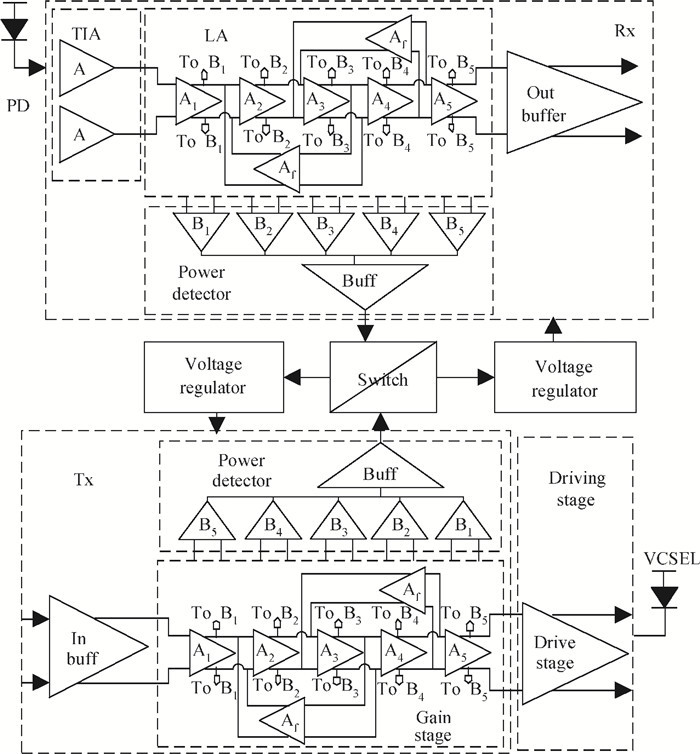

A power-aware transceiver for half-duplex bidirectional chip-to-chip optical interconnects has been designed and fabricated in a 0.13 μm complementary metal-oxide-semiconductor (CMOS) technology. The transceiver can detect the presence and absence of received signals and saves 55% power in Rx enabled mode and 45% in Tx enabled mode. The chip occupies an area of 1.034 mm2 and achieves a 3-dB bandwidth of 6 GHz and 7 GHz in Tx and Rx modes, respectively. The disabled outputs for the Tx and Rx modes are isolated with 180 dB and 139 dB, respectively, from the enabled outputs. Clear eye diagrams are obtained at 4.25 Gbps for both the Tx and Rx modes. -

References

[1] Pitwon R C A, Wang K, Jones J G, et al. First light:pluggable optical interconnect technologies for polymeric electro-optical printed circuit boards in data centers. J Lightwave Technol, 2012, 30(21):3316 doi: 10.1109/JLT.2012.2214764[2] Sangirov J, Ukaegbu I A, Lee T W, et al. Signal synchronization using a flicker reduction and denoising algorithm for video-signal optical interconnect. ETRI Journal, 2012, 34(1):122 https://etrij.etri.re.kr/etrij/journal/article/article.do?volume=34&issue=1&page=122[3] Hui X, Jun F, Quan L, et al. A 3.125-Gb/s inductorless transimpedance amplifier for optical communication in 0.35μm CMOS. Journal of Semiconductors, 2011, 32(10):105003 doi: 10.1088/1674-4926/32/10/105003[4] Kang S K, Lee T W, Plant D V, et al. A novel bidirectional CMOS transceiver for chip-to-chip optical interconnects. IEEE Photonics Technol Lett, 2006, 18(1):70 doi: 10.1109/LPT.2005.859993[5] Ngo T H, Nga T H N, Ukaegbu I A, et al. Bidirectional CMOS transceiver with automatic mode control for chip-to-chip optical interconnects. IEEE Photonics Technol Lett, 2009, 21(17):1241 doi: 10.1109/LPT.2009.2025045[6] Sangirov J, Ukaegbu I A, Lee T W, et al. Short turn-on/off time linear voltage regulator with data detector for power-aware optical interconnect system. Opto-Electronics and Communications Conference (OECC), 2012:109 http://ieeexplore.ieee.org/abstract/document/6276395/[7] Zhang T, Eisenstadt W R, Fox R M. 20 GHz bipolar RF RMS power detectors. BiCMOS Circuits and Technology Meetings Conference, 2005:204 http://ieeexplore.ieee.org/document/1555232/keywords[8] Razavi B. Design of analog CMOS integrated circuits. McGraw-Hill, 2001[9] Baker R J. CMOS circuit design, layout, and simulation. Wiley Interscience, 2005 doi: 10.1002/9780470891179;jsessionid=44978961BEF754A76BFC6672E0FA0750.f03t02?systemMessage=Wiley+Online+Library+will+be+unavailable+on+Saturday+7th+Oct+from+03.00+EDT+%2F+08%3A00+BST+%2F+12%3A30+IST+%2F+15.00+SGT+to+08.00+EDT+%2F+13.00+BST+%2F+17%3A30+IST+%2F+20.00+SGT+and+Sunday+8th+Oct+from+03.00+EDT+%2F+08%3A00+BST+%2F+12%3A30+IST+%2F+15.00+SGT+to+06.00+EDT+%2F+11.00+BST+%2F+15%3A30+IST+%2F+18.00+SGT+for+essential+maintenance.+Apologies+for+the+inconvenience+caused+.[10] Sangirov J, Ukaegbu I A, Lee T W, et al. 10 Gbps transimpedance amplifier-receiver for optical interconnects. J Optical Society of Korea, 2013, 17(1):44 doi: 10.3807/JOSK.2013.17.1.044[11] Huang H Y, Chien J C, Lu L H. A 10-Gb/s inductorless CMOS limiting amplifier with third-order interleaving active feedback. IEEE J Solid-State Circuits, 2007, 42(5):1111 doi: 10.1109/JSSC.2007.894819 -

Proportional views

DownLoad:

DownLoad: