| Citation: |

Jianming Lei, Hanshu Gui, Beiwen Hu. A low glitch 12-bit current-steering CMOS DAC for CNC systems[J]. Journal of Semiconductors, 2013, 34(2): 025007. doi: 10.1088/1674-4926/34/2/025007

****

J M Lei, H S Gui, B W Hu. A low glitch 12-bit current-steering CMOS DAC for CNC systems[J]. J. Semicond., 2013, 34(2): 025007. doi: 10.1088/1674-4926/34/2/025007.

|

A low glitch 12-bit current-steering CMOS DAC for CNC systems

DOI: 10.1088/1674-4926/34/2/025007

More Information

-

Abstract

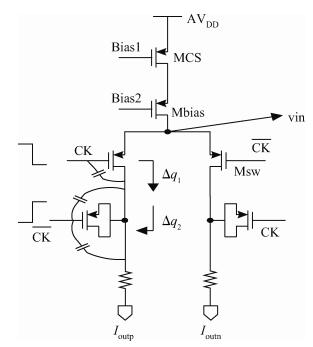

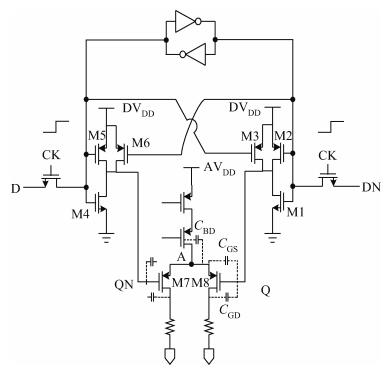

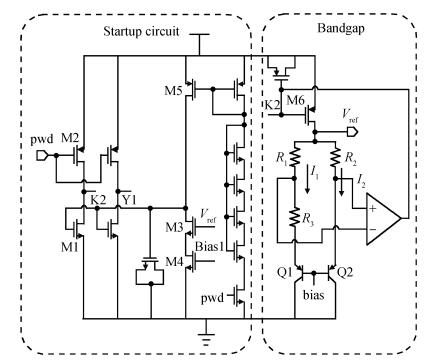

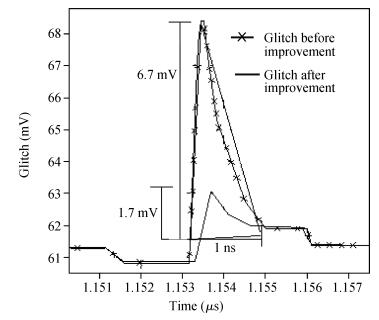

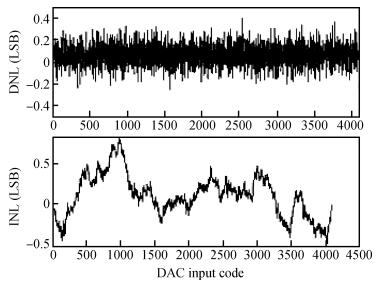

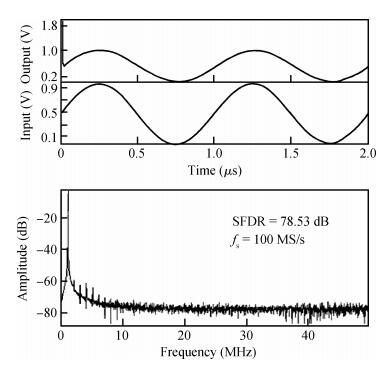

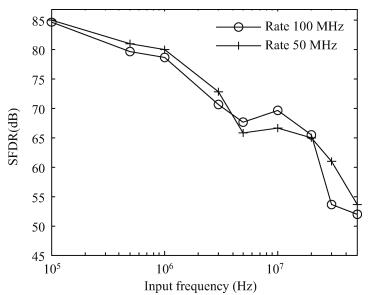

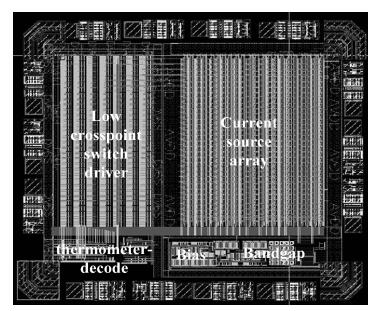

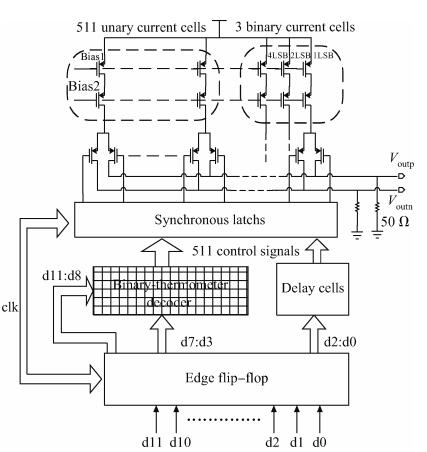

A 12-bit, 100-MHz CMOS current-steering D/A converter for CNC (computer number control) systems is presented. To reduce the glitch and increase the SFDR (spurious-free dynamic range), a low crosspoint switch driver and a special dummy switch are applied. In addition, a 4-5-3 segmental structure is used to optimize the performance and layout area. After improvement, the biggest glitch energy decreased from 6.7 pVs to 1.7 pVs, the INL decreased from 2 LSB to 0.8 LSB, the SFDR is 78 dB at a 100-MSPS clock rate and 1 MHz output frequency. This DAC can deliver up to 20.8 mA full-scale current into a 50 Ω load. The power when operating at full-scale current is 163 mW. The layout area is 1.8×1.8 mm2 in a standard 0.35-μm CMOS technology.-

Keywords:

- CNC systems,

- current-steering DAC,

- low glitch,

- cascode,

- crosspoint switch driver,

- SFDR

-

References

[1] Chen T, Geens P, Van der Plas G. A 14-bits 130-MHz CMOS current-steering DAC with adjustable INL. Solid-State Circuits Conference, 2004:167 https://core.ac.uk/display/34285991[2] Ikeda Y, Frey M, Matsuzawa A. A 14-bit 100-MS/s digitally calibrated binary weighted current-steering CMOS DAC without calibration ADC. IEEE Asian Solid-State Circuits Conference, 2007:356 http://www.ssc.pe.titech.ac.jp/publications/2007/ASSCC/13-3_Ikeda_presen.pdf[3] Van den Bosch A, Borremans M, Vandenbussche J. A 12 bits 200 MHz low glitch CMOS D/A converter. Custom Integrated Circuits Conference, 1998:249 doi: 10.1007/s10470-007-9105-1[4] O'Sullivan K, Gorman C, Hennessy M. A 12-bit 320-MSample/s current steering CMOS D/A converter in 0.44 mm2. IEEE J Solid-State Circuits, 2004, 39(7):1064 doi: 10.1109/JSSC.2004.829923[5] Xu Bulu, Shao Bowen, Lin Xia, et al. Design and verification of a 10-bits 1.2 V 100 Msps D/A IP core based on a 0.13μm low power CMOS process. Journal of Semiconductors, 2010, 31(9):095007 doi: 10.1088/1674-4926/31/9/095007[6] Chen Zhenhai, Ji Huicai, Zhang Ganying. A current switch driver for high-speed current-steering DAC. Journal of China Academy of Electronics and Information Technology, 2010, 5(5):523 https://wiki.analog.com/university/courses/tutorials/cmos-dac-chapter[7] Zhao Weibing, Shen Yanzhao, Zhang Xiangming. Current switches in improved high speed DAC and control signals of switches. Chinese Journal of Semiconductors, 2003, 24(9):991[8] Zhu Z, Yang Y. Design of a 14-bit 100 Msps digital to analog converter based on 0.35μm CMOS process. Research & Progress of SSE, 2004, 24(4):192[9] Qiu Dong, Fang Sheng. A current-steering self calibration 14 bits 100 Msps DAC. Journal of Semiconductors, 2010, 31(12):125007 doi: 10.1088/1674-4926/31/12/125007[10] Tomoroga M, Jurca L. Low glitch current-steering DAC with split input code. Proceedings of the 6th WSAEAS Int Conf on Electronics Hardware Wireless and Optical Communications, 2007:40 http://citeseerx.ist.psu.edu/viewdoc/summary?doi=10.1.1.495.8697[11] Tesch B J, Garcia J C. A low glitch 14-bits 100 MHz D/A converter. IEEE J Solid-state Circuits, 1997, 32(9):1465 doi: 10.1109/4.628767[12] Chen Hao, Liu Liyuan, Li Dongmei. A 12 bit current steering DAC with 2 dimensional gradient-error tolerant switching scheme. Journal of Semiconductors, 2010, 31(10):125006 http://www.jos.ac.cn/bdtxbcn/ch/reader/view_abstract.aspx?file_no=10040501&flag=1 -

Proportional views

DownLoad:

DownLoad: