| Citation: |

Jinxin Zhao, Jun Yan, Yin Shi. A-3 dBm RF transmitter front-end for 802.11g application[J]. Journal of Semiconductors, 2013, 34(4): 045002. doi: 10.1088/1674-4926/34/4/045002

****

J X Zhao, J Yan, Y Shi. A-3 dBm RF transmitter front-end for 802.11g application[J]. J. Semicond., 2013, 34(4): 045002. doi: 10.1088/1674-4926/34/4/045002.

|

A-3 dBm RF transmitter front-end for 802.11g application

DOI: 10.1088/1674-4926/34/4/045002

More Information

-

Abstract

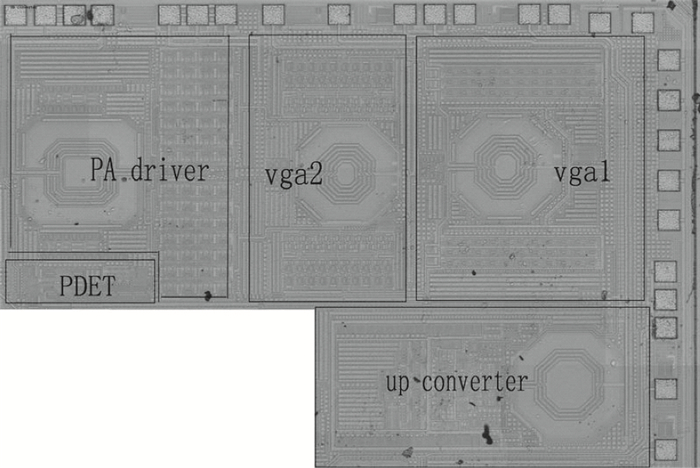

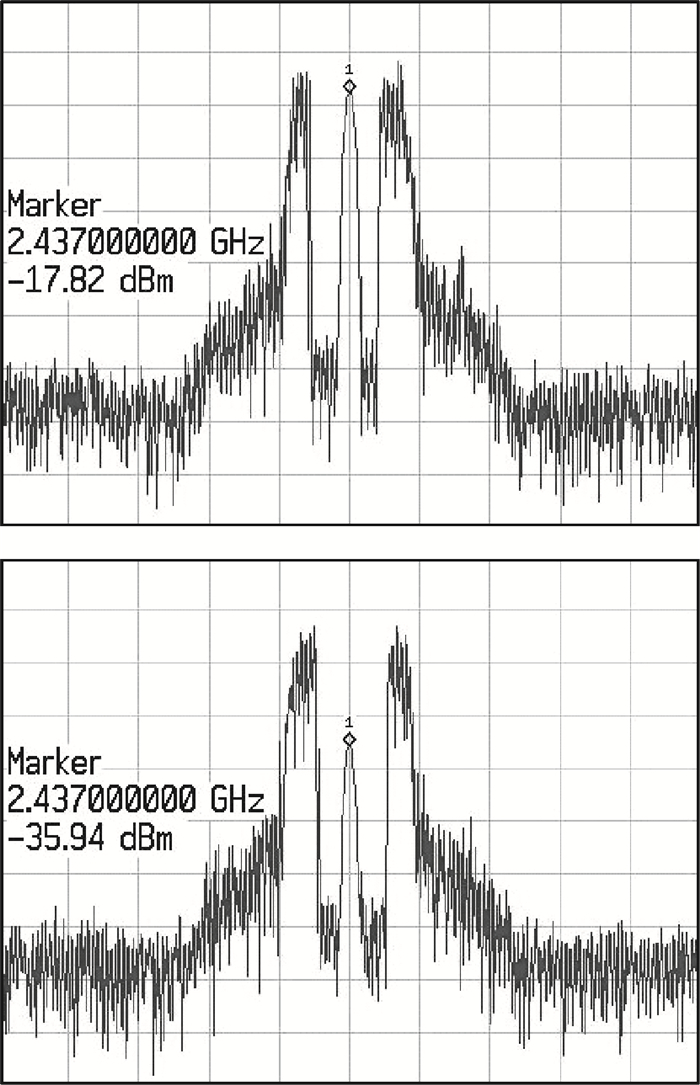

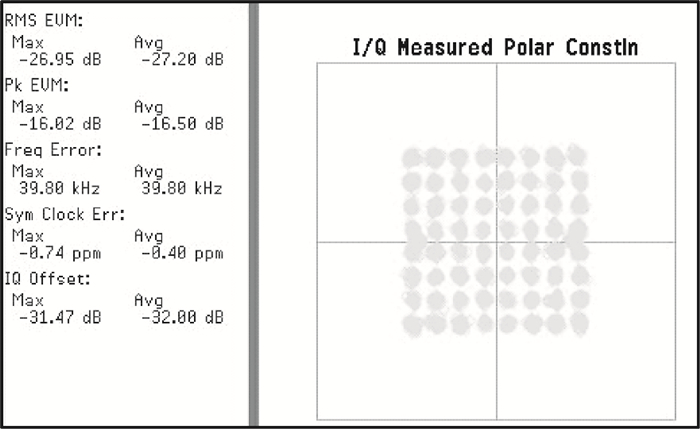

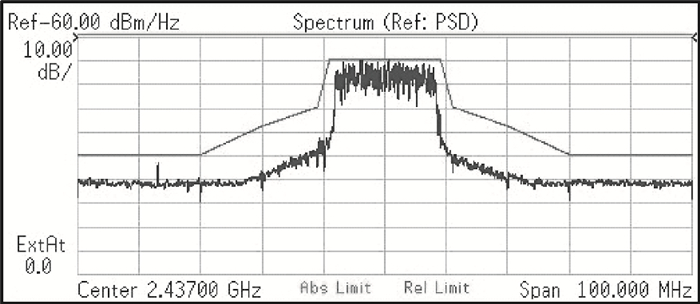

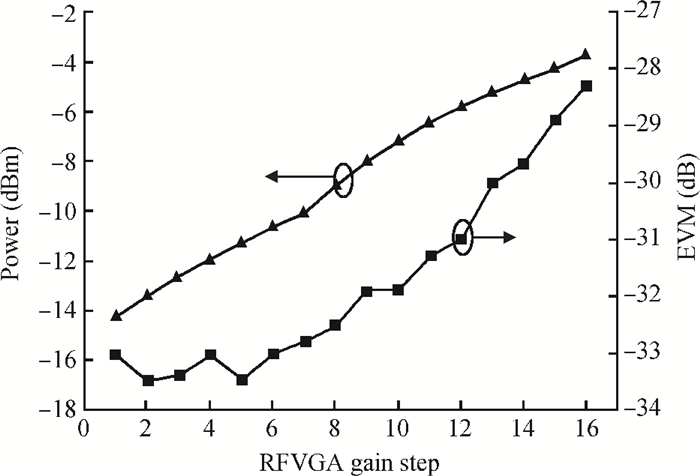

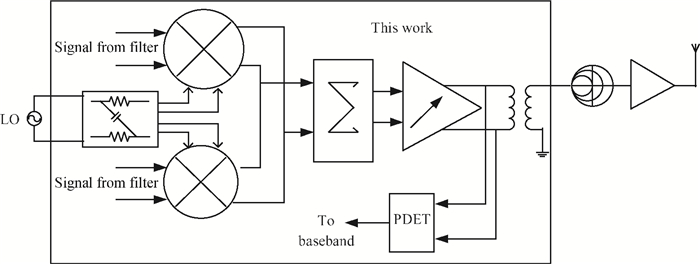

A 2.4 GHz, direct-conversion RF transmitter front-end with an up converter and PA driver is fabricated in a 0.13 μm CMOS process for the reliable transmission of 54 Mb/s OFDM signals. The front-end output power is-3 dBm while the corresponding EVM is-27 dB which is necessary for the 802.11g standard of EVM at-25 dB. With the adopted gain control strategy the output power changes from-14.3 to-3.7 dBm with every step 0.8 dB (20%) which covers the gain variation due to working temperature and process. A power detector indicates the output power and delivers a voltage to the baseband to control the output power.-

Keywords:

- 802.11g,

- RF transmitter front-end,

- up converter,

- RFVGA,

- PA driver,

- EVM

-

References

[1] Afsahi A, Behzad A, Magoon V, et al. Linearized dual-band power amplifiers with integrated baluns in 65 nm CMOS for a 2×2802.11n MIMO WLAN SoC. IEEE J Solid-State Circuits, 2010, 45(5):955 doi: 10.1109/JSSC.2010.2041401[2] Cripps S C. RF power amplifiers for wireless communications. 2nd ed. Artech House, 2006:250 http://ieeexplore.ieee.org/document/823830/citations[3] Razavi B. RF microelectronics. Upper Saddle River, New Jersey:Prentice Hall PTR, 1998:98[4] Gilbert B. A precise four-quadrant multiplier with subnanosecond response. IEEE J Solid-State Circuits, 1968, SC-3(4):365 http://ieeexplore.ieee.org/document/1049925/authors[5] Mehta S S, Weber D, Terrovitis M. An 802.11g WLAN SoC. IEEE J Solid-State Circuits, 2005, 40(12):2483 doi: 10.1109/JSSC.2005.857418[6] Galal S H, Ragaie H F, Tawfik M S. RC sequence asymmetric polyphase networks for RF integrated transceivers. IEEE Trans Circuits Syst Ⅱ:Analog and Digital Signal Progressing, 2000, 47(1):18 doi: 10.1109/82.818891[7] Simon M, Laaser P, Filimon V, et al. An 802.11a/b/g RF transceiver in an SoC. ISSCC, 2007:562 http://ieeexplore.ieee.org/document/4242515/[8] Long J R. Monolithic transformers for silicon RF IC design. IEEE J Solid-State Circuits, 2000, 35(9):1368 doi: 10.1109/4.868049[9] Darabi H, Khorram S, Zhou Z, et al. A fully integrated SoC for 802.11b in 0.18μm CMOS. IEEE International Solid-State Circuits Conference, 2005:96[10] Wu C H, Chung Y H, Lin A, et al. A world-band triple-mode 802.11a/b/g in 0.13μm CMOS. IEEE Asian Solid-State Circuits Conference, 2008:337[11] Winoto R, He M, Lu Y, et al. A WLAN and bluetooth combo transceiver with integrated power amplifier, transmit-receive switch and WLAN/bluetooth shared low noise amplifier. IEEE Radio Frequency Integrated Circuits Symposium, RTU2B-2,2012 http://ieeexplore.ieee.org/document/6242307/keywords[12] Mason R, Fortier J, DeVrises C. Complete SOC transceiver in 0.18μm CMOS using Q-enhanced filtering, sub-sampling and injection locking. IEEE Custom Integrated Circuit Conference, 2011 https://www.infona.pl/resource/bwmeta1.element.ieee-art-000006212476[13] Tan Y, Duster J, Fu C T, et al. A 2.4 GHz WLAN transceiver with fully-integrated highly-linear 1.8 V 28.4 dBm PA, 34 dBm T/R switch, 240 MS/s DAC, 320 MS/s ADC, and DPLL in 32 nm SoC CMOS. Symposium on VLSI Circuits Digest of Technical Papers, 2012:76 doi: 10.1007/978-1-4614-1371-4_10 -

Proportional views

DownLoad:

DownLoad: