| Citation: |

Kai Han, Xueli Ma, Hong Yang, Wenwu Wang. Modulation of the effective work function of a TiN metal gate for NMOS requisition with Al incorporation[J]. Journal of Semiconductors, 2013, 34(7): 076003. doi: 10.1088/1674-4926/34/7/076003

****

K Han, X L Ma, H Yang, W W Wang. Modulation of the effective work function of a TiN metal gate for NMOS requisition with Al incorporation[J]. J. Semicond., 2013, 34(7): 076003. doi: 10.1088/1674-4926/34/7/076003.

|

Modulation of the effective work function of a TiN metal gate for NMOS requisition with Al incorporation

DOI: 10.1088/1674-4926/34/7/076003

More Information

-

Abstract

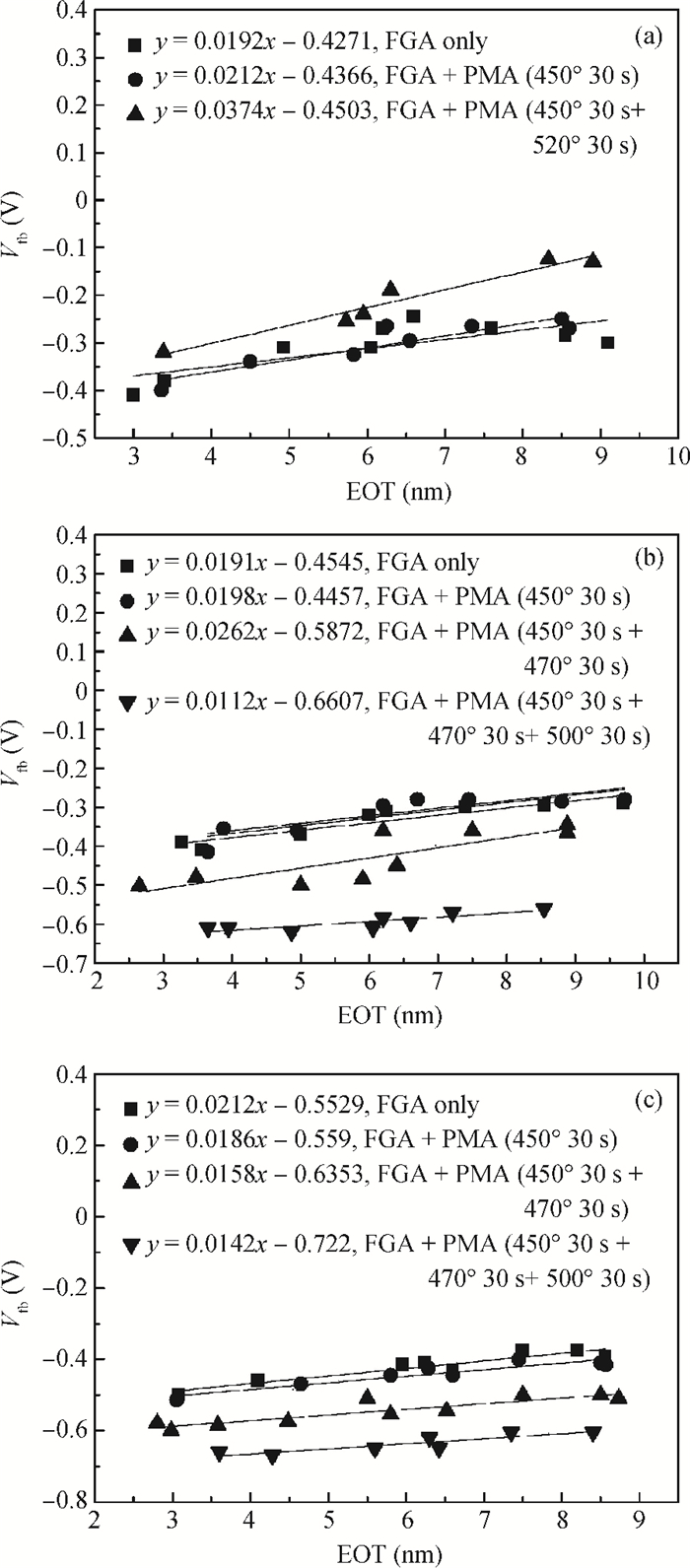

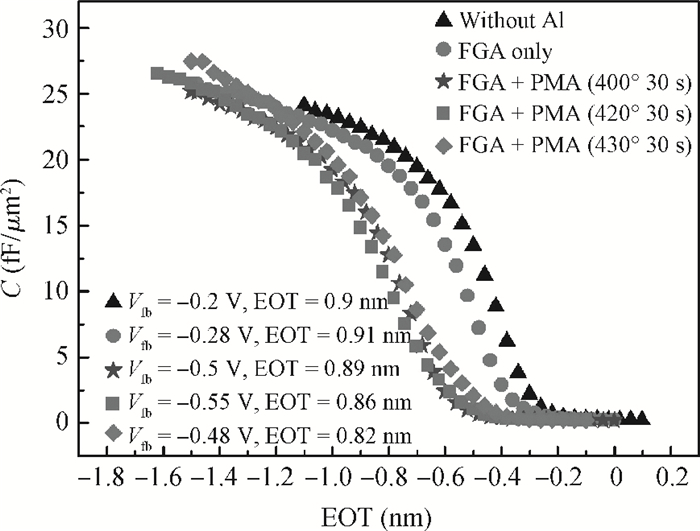

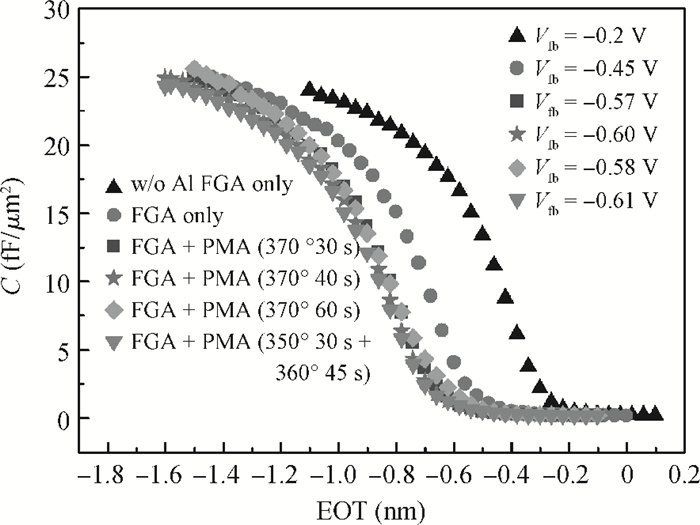

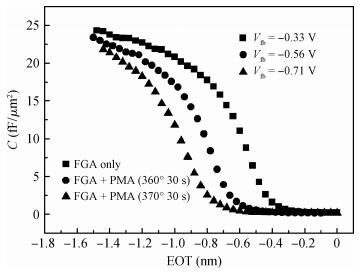

The effect of Al incorporation on the effective work function (EWF) of TiN metal gate was systematically investigated. Metal-oxide-semiconductor (MOS) capacitors with W/TiN/Al/TiN gate stacks were used to fulfill this purpose. Different thickness ratios of Al to TiN and different post metal annealing (PMA) conditions were employed. Significant shift of work function towards to Si conduction band was observed, which was suitable for NMOS and the magnitude of shift depends on the processing conditions.-

Keywords:

- work function modulation,

- Al,

- MOS capacitor,

- PMA

-

References

[1] Wilk G D, Wallace R M, Anthony J M. High-k gate dielectrics:current status and materials properties considerations. J Appl Phys, 2001, 89(10):5243[2] Zhao Y, Masahiro T, Koji K, et al. Moisture-absorption-induced permittivity deterioration and surface roughness enhancement of lanthanum oxide films on silicon. Appl Phys Lett, 2006, 88(7):072904 doi: 10.1063/1.2174840[3] Chau R, Brask J, Datta S, et al. Application of high-k gate dielectrics and metal gate electrodes to enable silicon and non-silicon logic nanotechnology. Microelectron Eng, 2005, 80:1 doi: 10.1016/j.mee.2005.04.035[4] Narayanan V, Paruchuri V K, Bojarczuk N A, et al. Band-edge high-performance high-k/metal gate n-MOSFETs using cap layers containing group ⅡA and ⅢB elements with gate-first processing for 45 nm and beyond. Dig Tech Pap Symp VLSI Technol, 2006:224[5] Masaru K, Takeo M, Seiichi M, et al. Effective-work-function control by varying the TiN thickness in poly-Si/TiN gate electrodes for scaled high-k CMOSFETs. IEEE Electron Device Lett, 2009, 30(5):466 doi: 10.1109/LED.2009.2016585[6] Jörgen W, Gustaf S, Jörgen O. Variable work function in MOS capacitors utilizing nitrogen-controlled TiNx gate electrodes. Microelectron Eng, 2004, 75:389 doi: 10.1016/j.mee.2004.07.061[7] Wang Xiaorong, Jiang Yulong, Xie Qi. Annealing effect on the metal gate effective work function modulation for the Al/TiN/SiO2/p-Si structure. Microelectron Eng, 2011, 88:573 doi: 10.1016/j.mee.2010.06.029 -

Proportional views

DownLoad:

DownLoad: