| Citation: |

Zhaoxin Ma, Xuefei Bai, Lu Huang. Design of a delay-locked-loop-based time-to-digital converter[J]. Journal of Semiconductors, 2013, 34(9): 095003. doi: 10.1088/1674-4926/34/9/095003

****

Z X Ma, X F Bai, L Huang. Design of a delay-locked-loop-based time-to-digital converter[J]. J. Semicond., 2013, 34(9): 095003. doi: 10.1088/1674-4926/34/9/095003.

|

Design of a delay-locked-loop-based time-to-digital converter

DOI: 10.1088/1674-4926/34/9/095003

More Information

-

Abstract

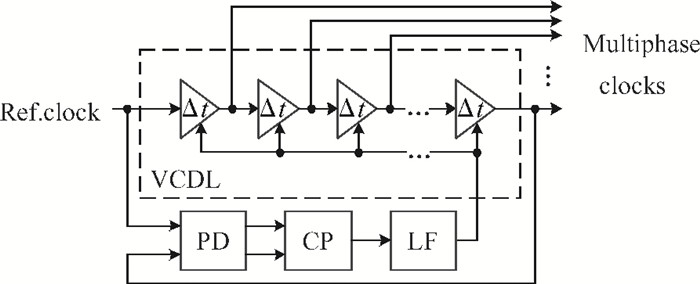

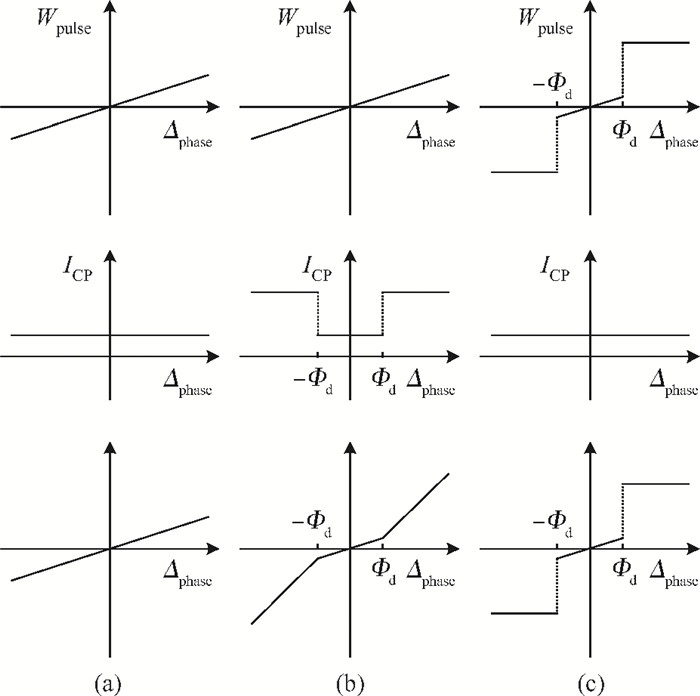

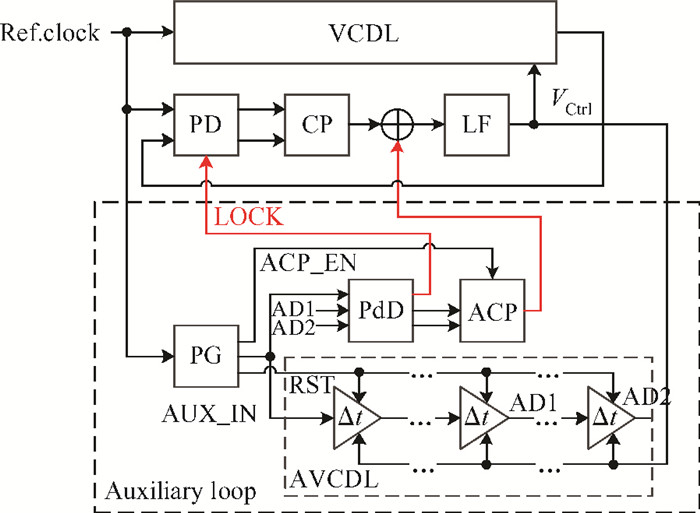

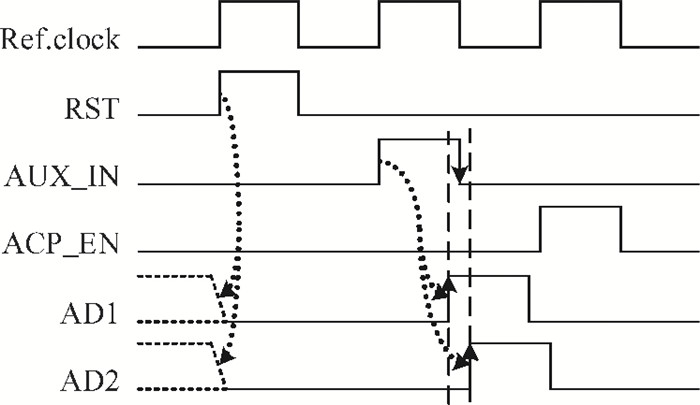

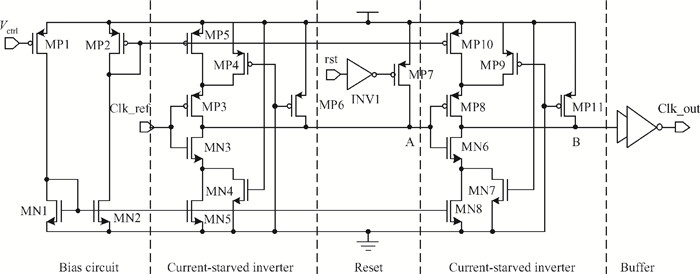

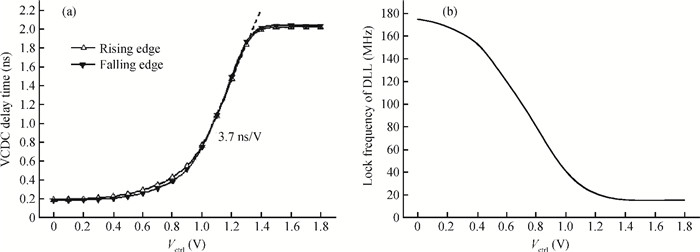

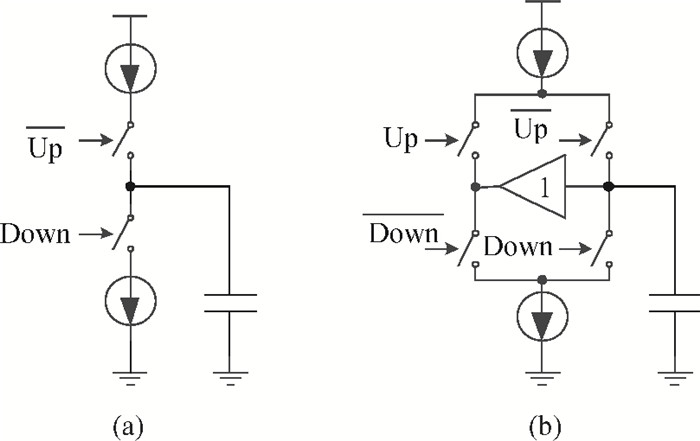

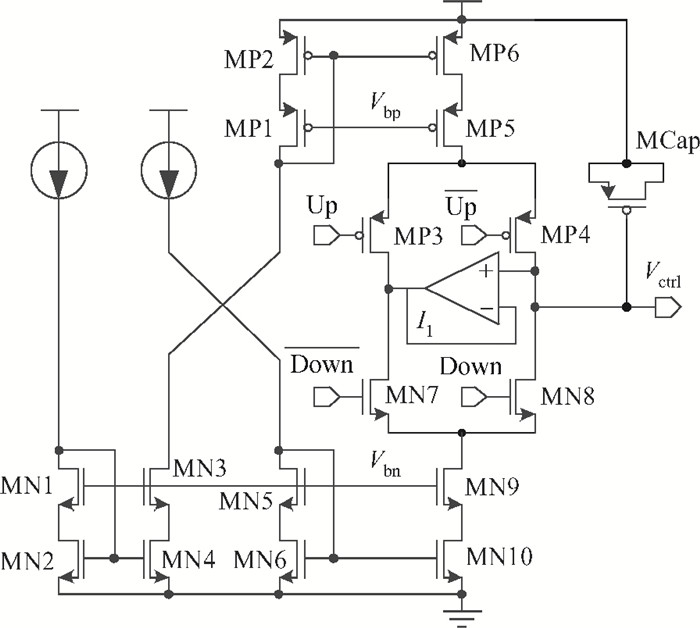

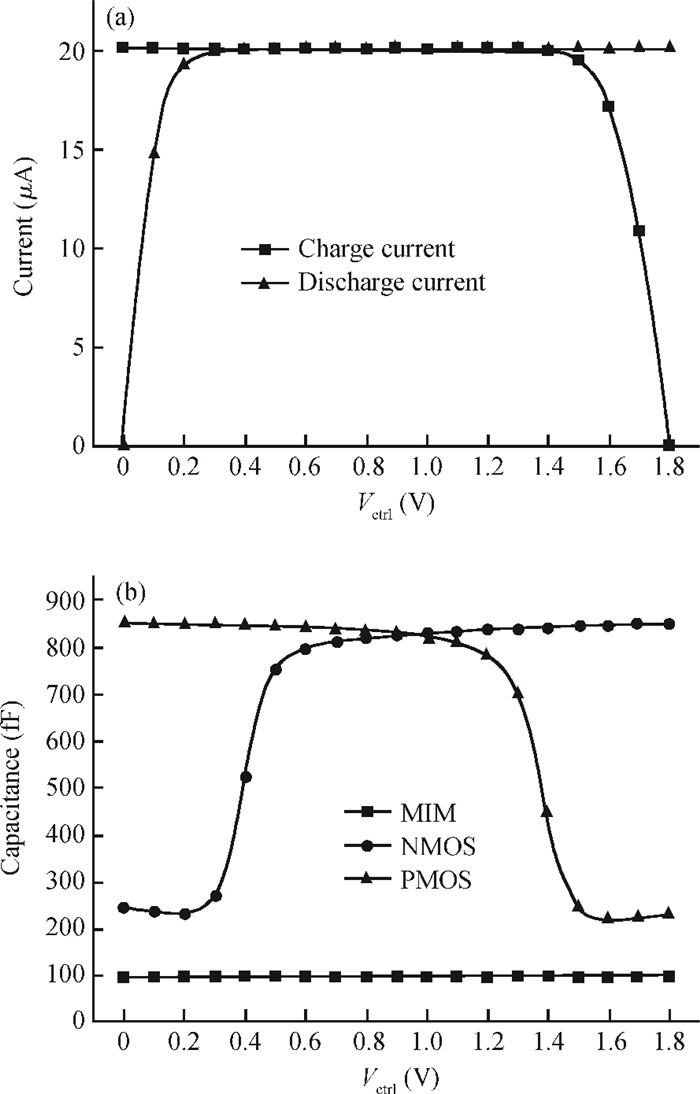

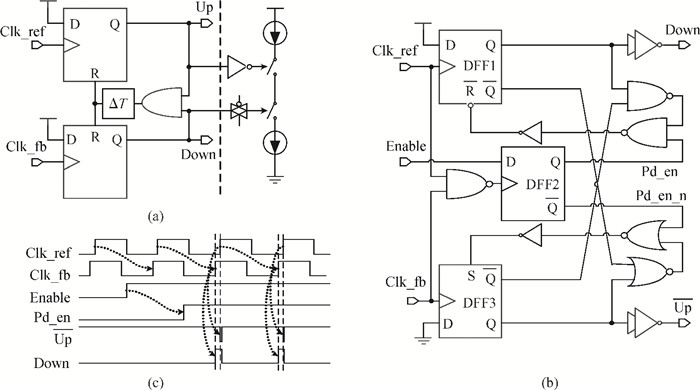

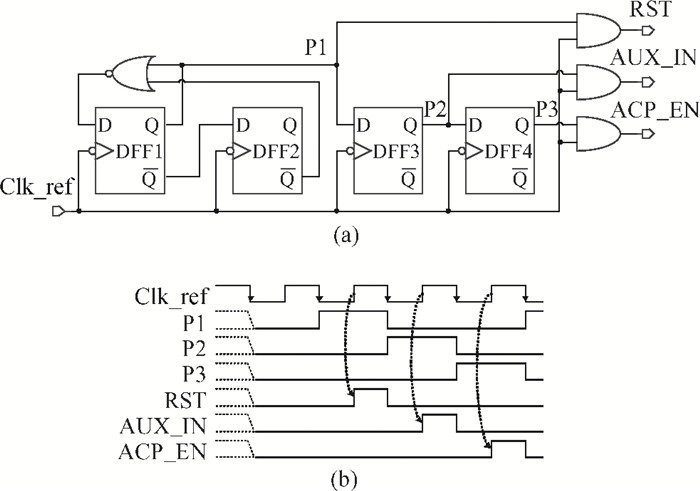

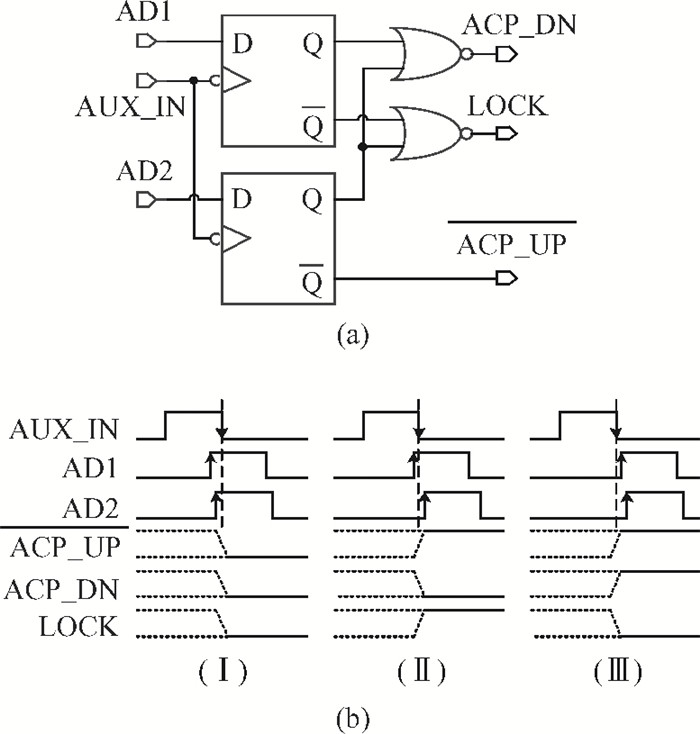

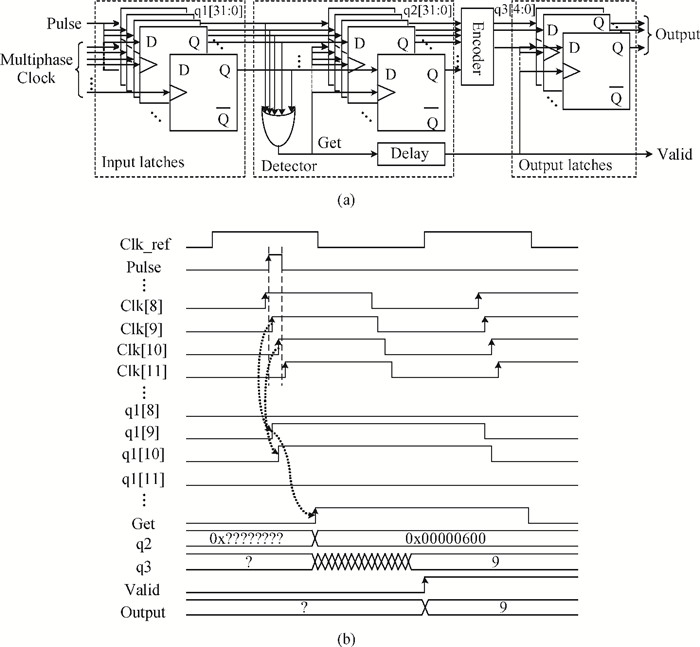

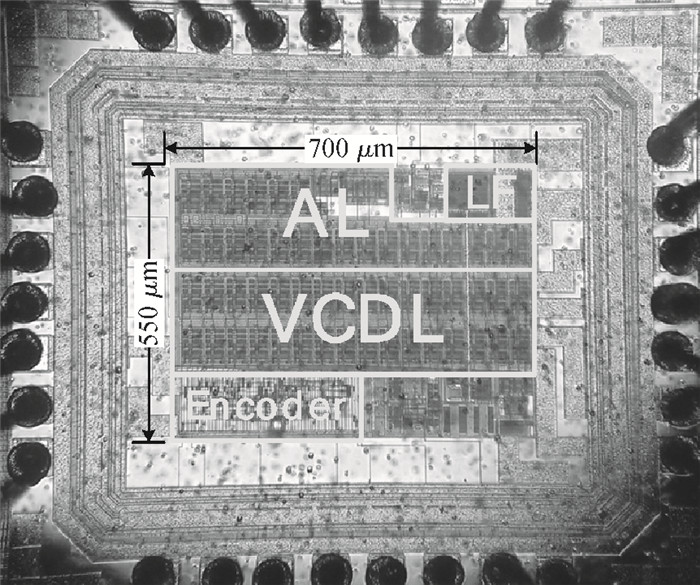

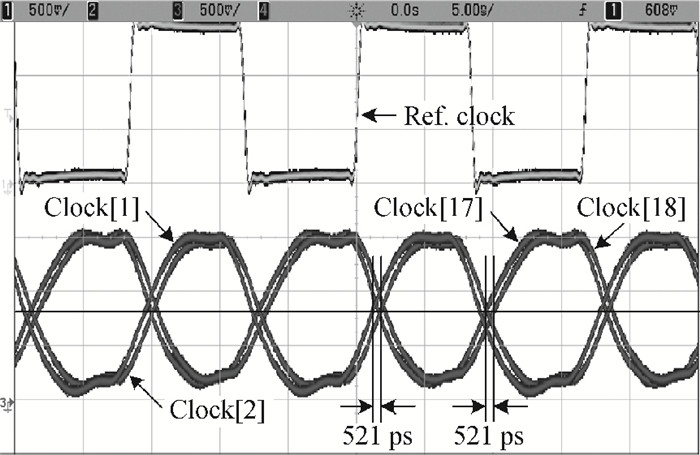

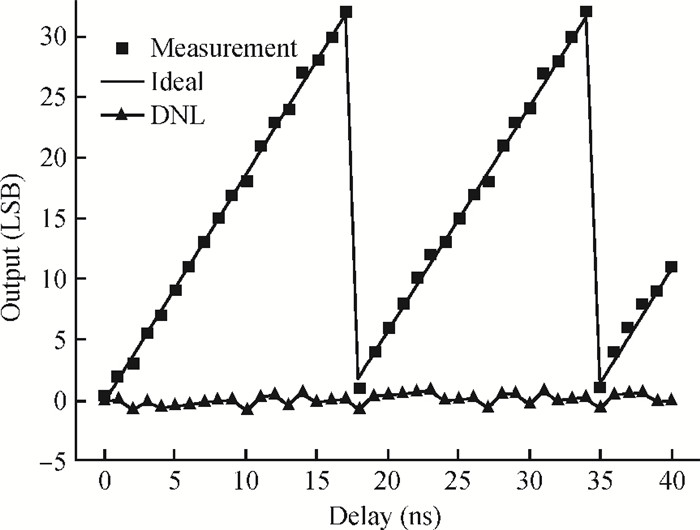

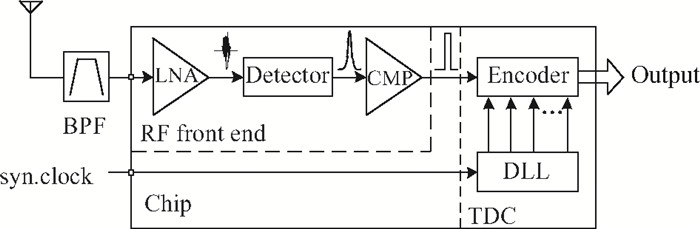

A time-to-digital converter (TDC) based on a reset-free and anti-harmonic delay-locked loop (DLL) circuit for wireless positioning systems is discussed and described. The DLL that generates 32-phase clocks and a cycle period detector is employed to avoid "false locking". Driven by multiphase clocks, an encoder detects pulses and outputs the phase of the clock when the pulse arrives. The proposed TDC was implemented in SMIC 0.18 μm CMOS technology, and its core area occupies 0.7×0.55 mm2. The reference frequency ranges from 20 to 150 MHz. An LSB resolution of 521 ps can be achieved by using a reference clock of 60 MHz and the DNL is less than ±0.75 LSB. It dissipates 31.5 mW at 1.8 V supply voltage.-

Keywords:

- TDC,

- DLL,

- multiphase clock,

- false lock,

- jitter

-

References

[1] Hui L, Houshang D, Pat B, et al. Survey of wireless indoor positioning techniques and systems. IEEE Trans Syst, Man, Cybern, Part C, 2007, 37(6):1067 doi: 10.1109/TSMCC.2007.905750[2] Michael K, Cemin Z, Brandon M, et al. High accuracy UWB localization in dense indoor environments. IEEE Inter Conf on UWB, 2008, 2:129 http://ieeexplore.ieee.org/document/4653368/[3] Cai L, Huang L, Fu Z, et al. An energy detection receiver for non-coherent IR-UWB. Journal of Semiconductors, 2011, 32(6):065006 doi: 10.1088/1674-4926/32/6/065006[4] Jorgen C. An integrated high resolution CMOS timing generator based on an array of delay locked loops. IEEE J Solid-State Circuits, 1996, 31(7):952 doi: 10.1109/4.508208[5] Fahim A M. Clock generators for SOC processors. Beijing:Science-Press, 2007:129[6] Lee M J E, Dally W J, Greer T, et al. Jitter transfer characteristics of delay-locked loops—theories and design techniques. IEEE J Solid-State Circuits, 2003, 38(4):614 doi: 10.1109/JSSC.2003.809519[7] Cheng K H, Yang W B, Ying C M. A dual-slope phase frequency detector and charge pump architecture to achieve fast locking of phase-locked loop. IEEE Trans Circuits Syst Ⅱ, 2003, 50(11):892 doi: 10.1109/TCSII.2003.819130[8] Song E, Lee S W, Lee J W, et al. A reset-free anti-harmonic delay-locked loop using a cycle period detector. IEEE J Solid-States Circuits, 2004, 39(11):2055 doi: 10.1109/JSSC.2004.835840[9] Wu G, Deyuan G, David B, et al. Precise multiphase clock generation using low-jitter delay-locked loop techniques for positron emission tomography imaging. IEEE Trans Nucl Sci, 2010, 57(3):1063 doi: 10.1109/TNS.2010.2044663[10] Hwang C S, Chen P, Tsao H W. A high-precision time-to-digital converter using a two-level conversion scheme. IEEE Trans Nucl Sci, 2004, 51(4):1349 doi: 10.1109/TNS.2004.832902 -

Proportional views

DownLoad:

DownLoad: