| Citation: |

Chenluan Wang, Shengxi Diao, Fujiang Lin. A low-power time-domain VCO-based ADC in 65 nm CMOS[J]. Journal of Semiconductors, 2014, 35(10): 105009. doi: 10.1088/1674-4926/35/10/105009

****

C L Wang, S X Diao, F J Lin. A low-power time-domain VCO-based ADC in 65 nm CMOS[J]. J. Semicond., 2014, 35(10): 105009. doi: 10.1088/1674-4926/35/10/105009.

|

A low-power time-domain VCO-based ADC in 65 nm CMOS

DOI: 10.1088/1674-4926/35/10/105009

More Information

-

Abstract

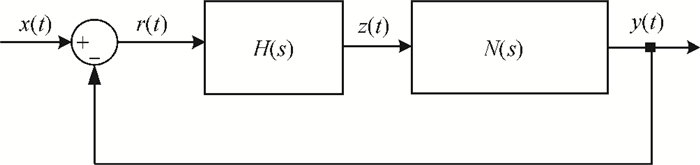

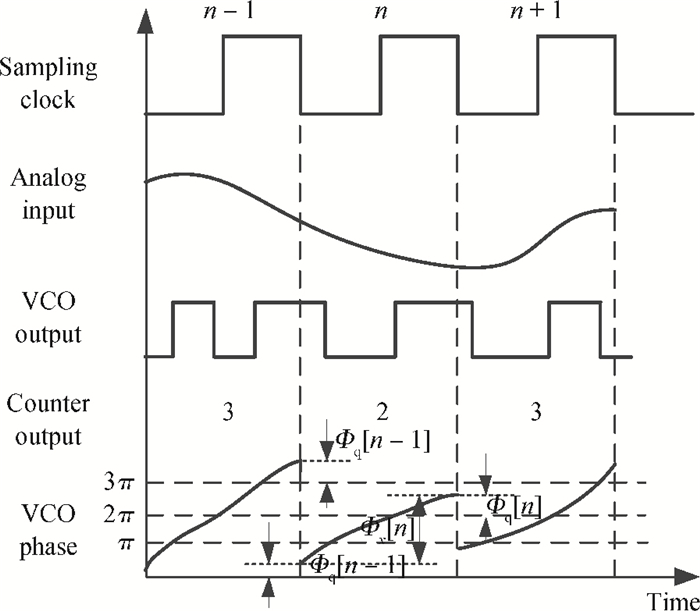

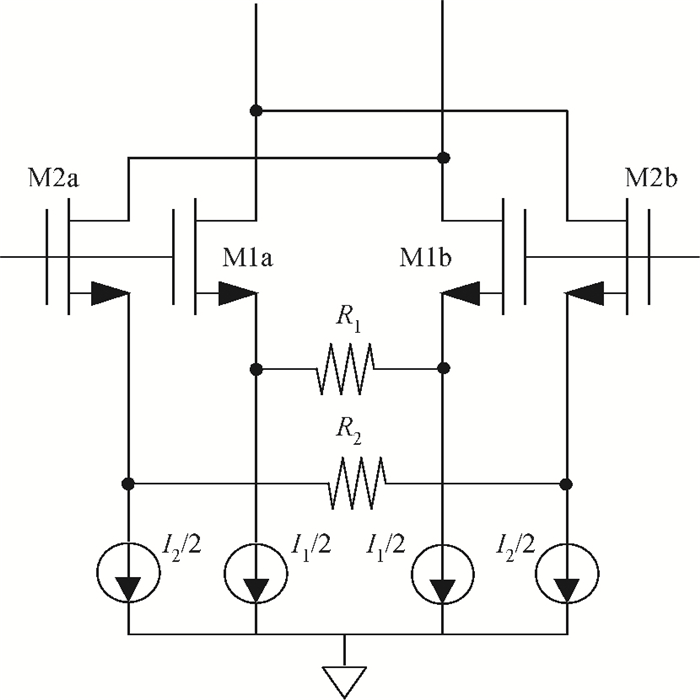

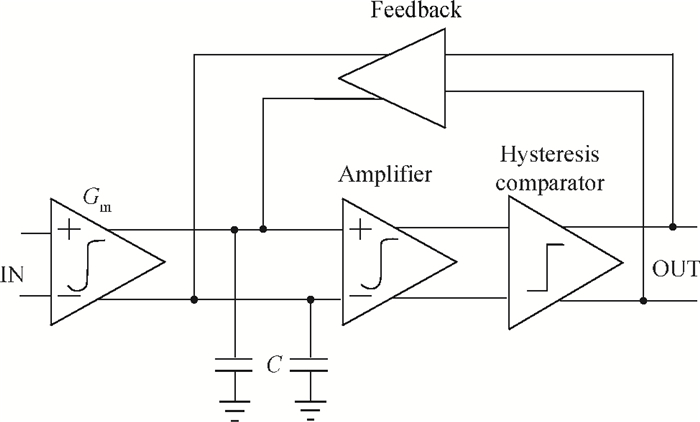

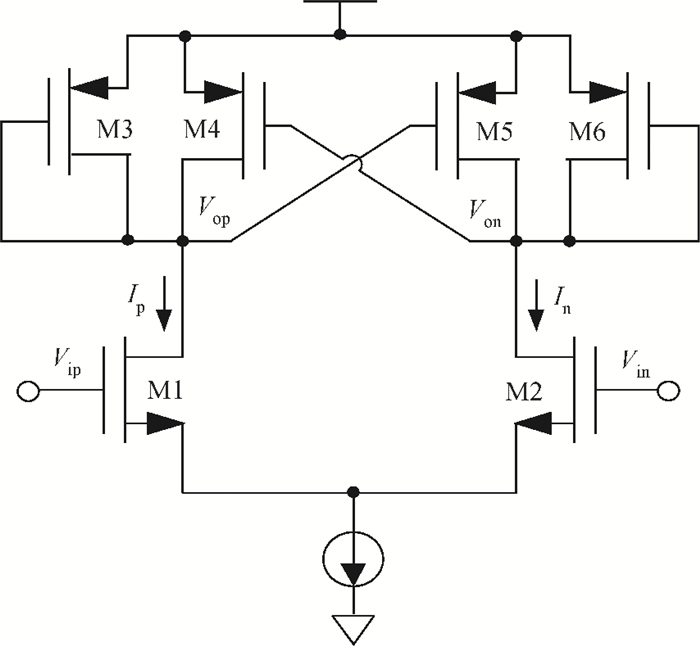

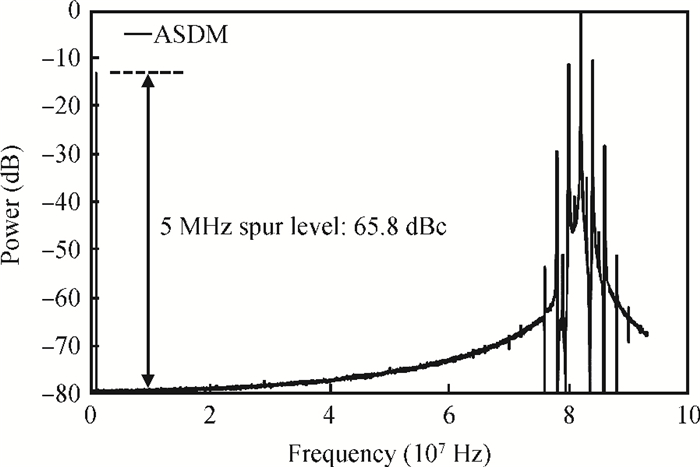

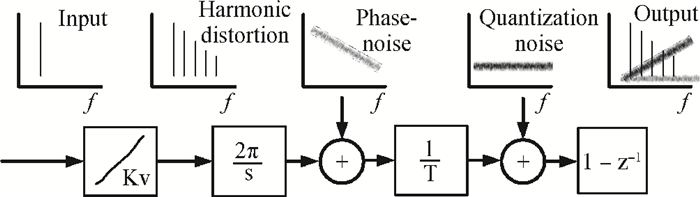

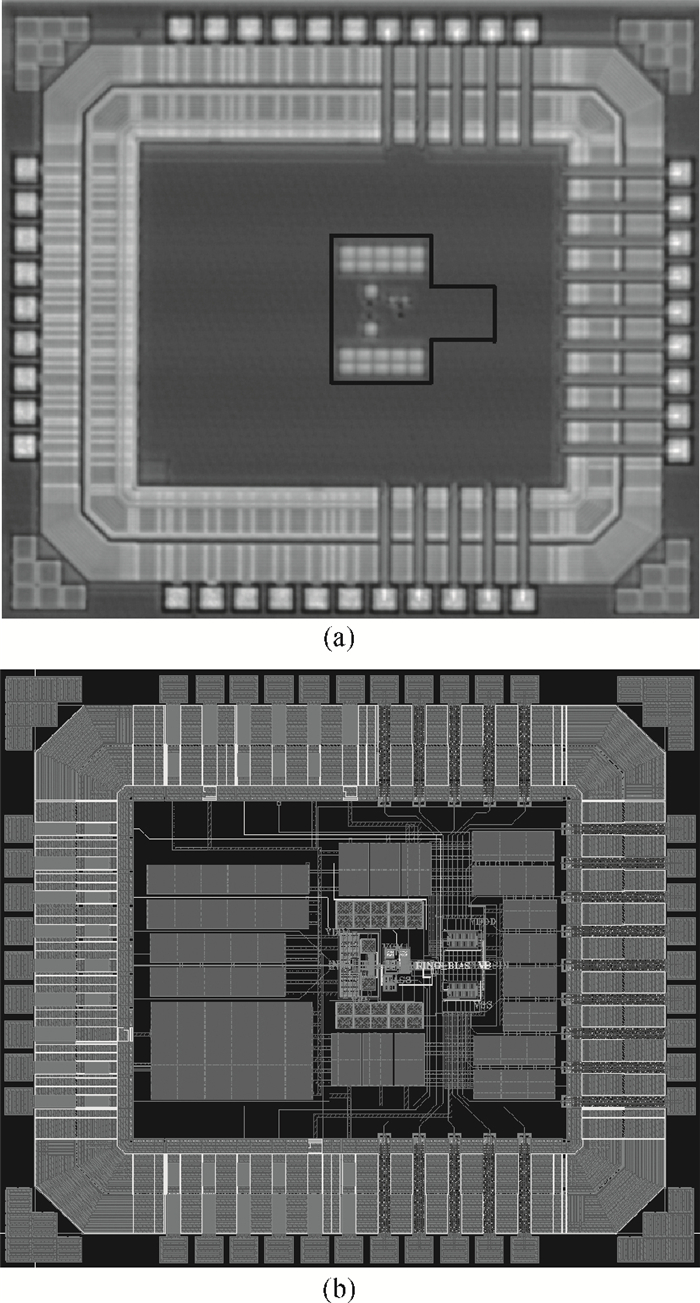

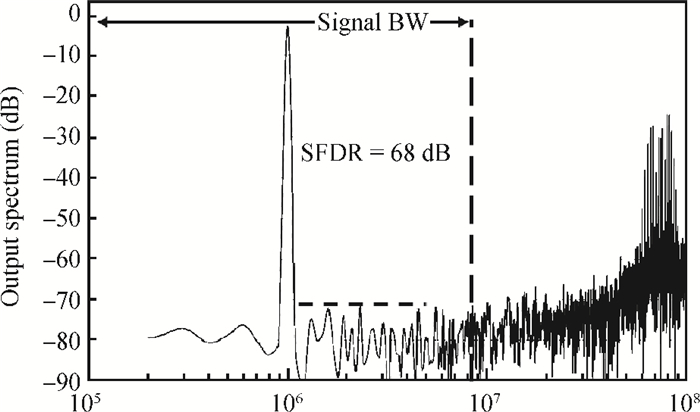

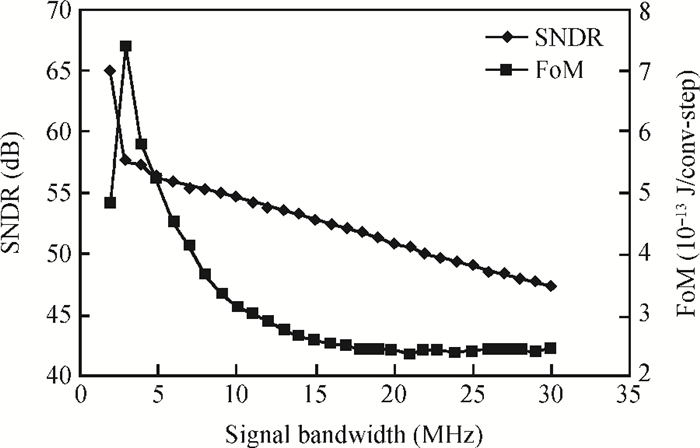

A low-power, high-FoM (figure of merit), time-domain VCO (voltage controlled oscillator)-based ADC (analog-to-digital converter) in 65 nm CMOS technology is proposed. An asynchronous sigma-delta modulator (ASDM) is used to convert the voltage input signal to a square wave time signal, where the information is contained in its pulse-width. A time-domain quantizer, which uses VCO to convert voltage to frequency, is adopted, while the XOR (exclusive-OR) gate circuits convert the frequency information to digital representatives. The ASDM does not need an external clock, so there is no quantization noise. At the same time, the ASDM applies a harmonic-distortion-cancellation technique to its transconductance stage, which increases the SNDR (signal to noise and distortion ratio) performance of the ASDM. Since the output of the ASDM is a two-level voltage signal, the VCO's V-F(voltage to frequency) conversion curve is always linear. The XOR phase quantizer has an inherent feature of first-order noise-shaping. It puts the ADC's low-frequency output noise to high-frequency which is further filtered out by a low-pass filter. The proposed ADC achieves an SNR/SNDR of 54. dB/54.3 dB in the 8 MHz bandwidth, while consuming 2.8 mW. The FoM of the proposed ADC is a 334 fJ/conv-step.-

Keywords:

- VCO,

- ADC,

- ASDM,

- PWM (pulse width modulation),

- nonlinearity,

- low-power

-

References

[1] Park M, Perrott M H. A 78 dB SNDR 87 mW 20 MHz bandwidth continuous-time delta-sigma ADC with VCO-based integrator and quantizer implemented in 0.13μm CMOS. IEEE J Solid-State Circuits, 2009, 44(12):3344 doi: 10.1109/JSSC.2009.2032703[2] Taylor G, Galton I. A mostly-digital variable-rate continuous-time delta-sigma modulator ADC. IEEE J Solid-State Circuits, 2010, 45(12):2634 doi: 10.1109/JSSC.2010.2073193[3] Rao S, Young B, Elshazly A, et al. A 71 dB SFDR open loop VCO-based ADC using 2-level PWM modulation. Symposium of VLSI Circuits Digest, 2011[4] Daniels J, Dehaene W, Steyaert M S J, et al. A/D conversion using asynchronous delta-sigma modulation and time-to-digital conversion. IEEE Trans Circuits Syst I Regular Papers, 2010, 57: 2404[5] Reddy K, Rao S, Inti R, et al. A 16 mW 78 dB-SNDR 10 MHz-BW CT-δ σ ADC using residue-cancelling VCO-based quantizer. ISSCC Digest Technical Papers, 2012[6] Ouzounov S, Roza E, Hegt J A, et al. Analysis and design of high-performance asynchronous sigma-delta modulators with a binary quantizer. IEEE J Solid-State Circuits, 2005, 41(3):588[7] Kim J, Jang T K, Yoon Y G, et al. Analysis and design of voltage-controlled oscillator based analog-to-digital converter. IEEE Trans Circuits Syst I:Regular Papers, 2010, 1(57):18[8] Ouzounov S, Roza E, Weide G V D, et al. A CMOS V-I converter with 75-dB SFDR and 360μW power consumption. IEEE J Solid-State Circuits, 2005, 40(7):1527 doi: 10.1109/JSSC.2005.847496[9] Ma Zhaoxin, Bai Xuefei, Huang Lu. Design of a delay-locked-loop-based time-to-digital converter. Journal of Semiconductors, 2013, 34(9):095003 doi: 10.1088/1674-4926/34/9/095003 -

Proportional views

DownLoad:

DownLoad: