| Citation: |

Xiaoyan Cheng, Haigang Yang, Tao Yin, Qisong Wu, Hongfeng Zhang, Fei Liu. Design and analysis of a dual mode CMOS field programmable analog array[J]. Journal of Semiconductors, 2014, 35(10): 105011. doi: 10.1088/1674-4926/35/10/105011

****

X Y Cheng, H G Yang, T Yin, Q S Wu, H F Zhang, F Liu. Design and analysis of a dual mode CMOS field programmable analog array[J]. J. Semicond., 2014, 35(10): 105011. doi: 10.1088/1674-4926/35/10/105011.

|

Design and analysis of a dual mode CMOS field programmable analog array

DOI: 10.1088/1674-4926/35/10/105011

More Information

-

Abstract

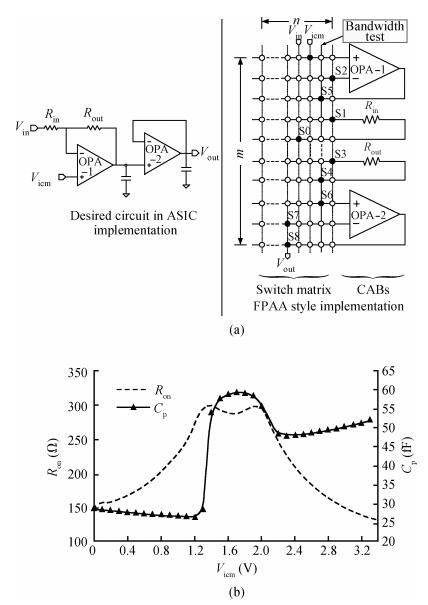

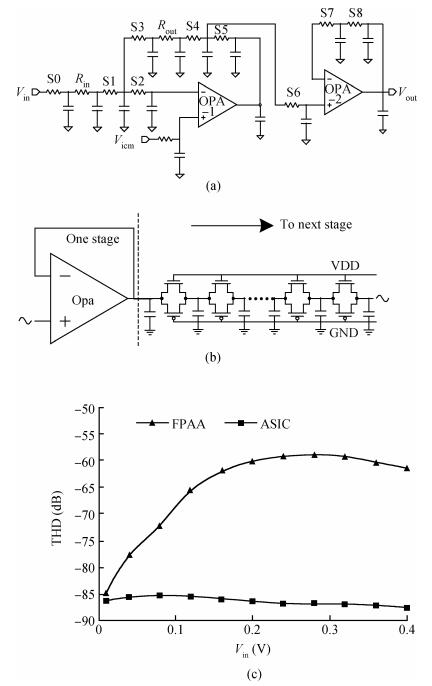

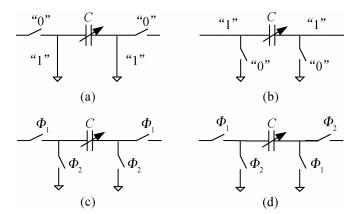

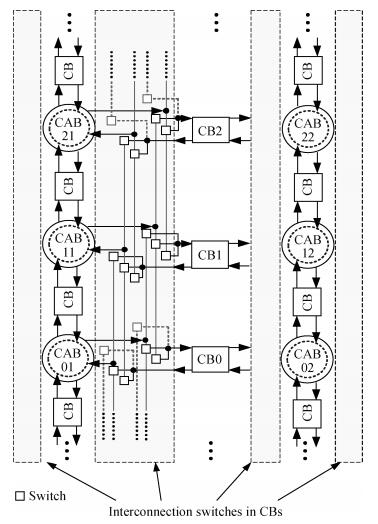

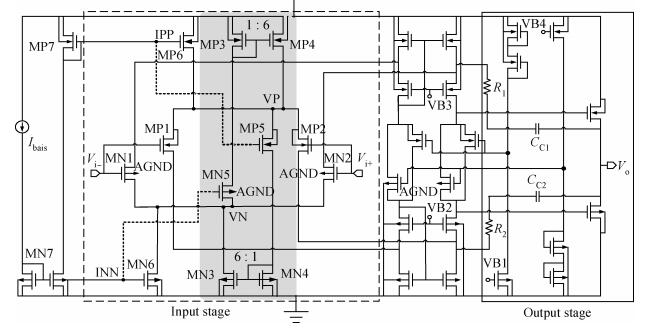

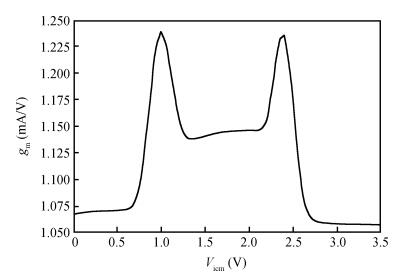

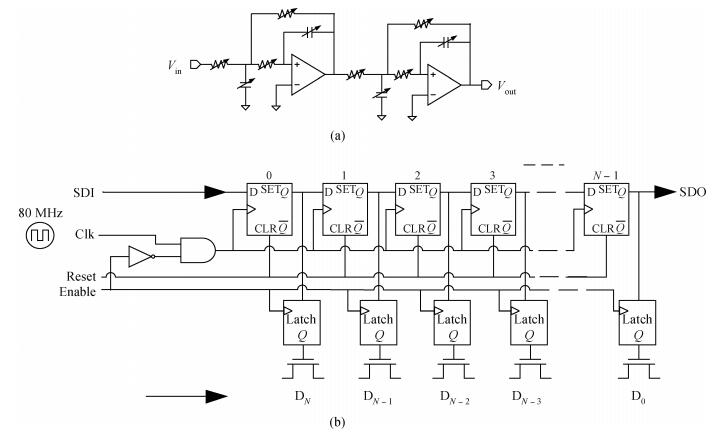

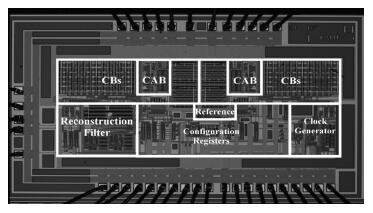

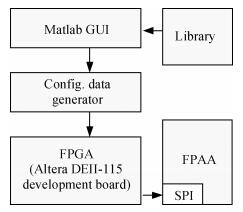

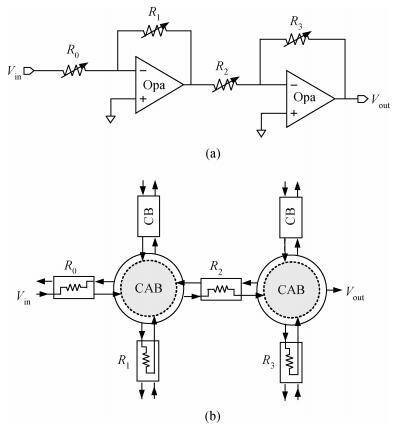

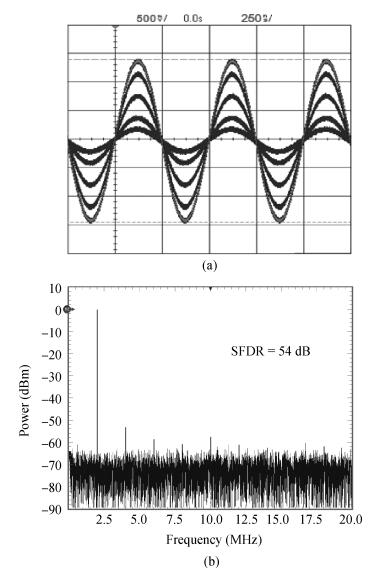

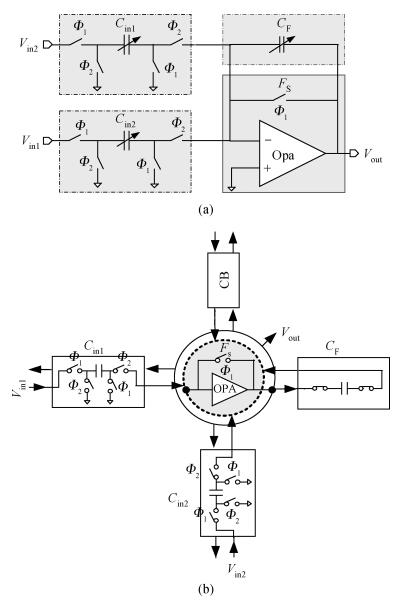

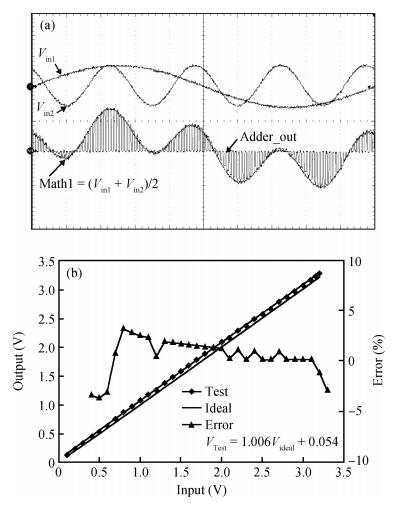

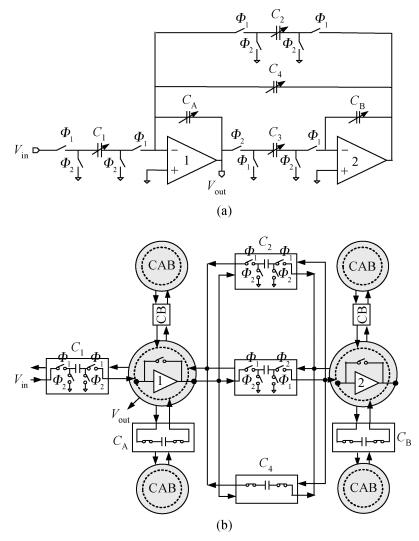

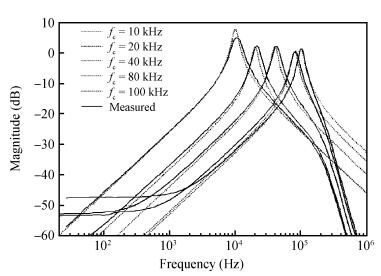

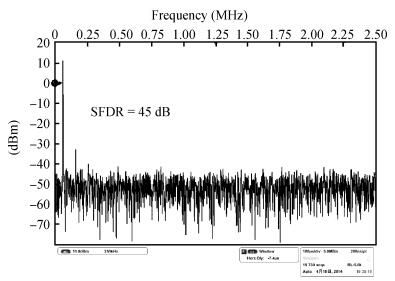

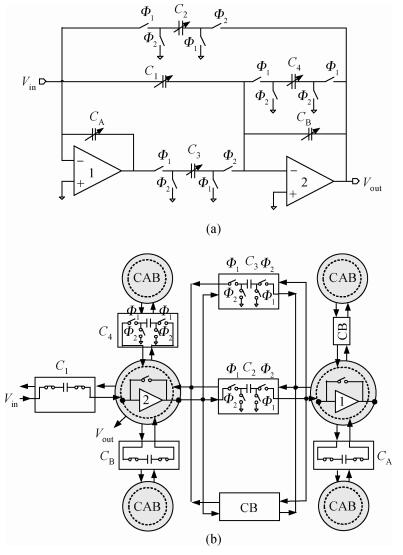

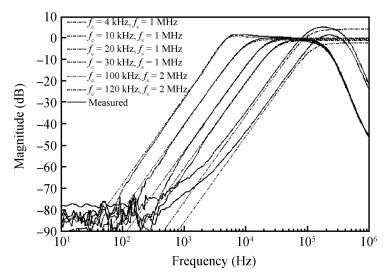

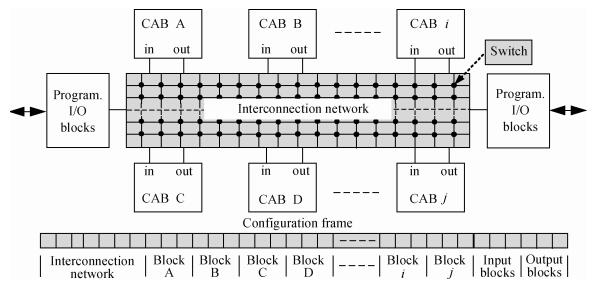

This paper presents a novel field-programmable analog array (FPAA) architecture featuring a dual mode including discrete-time (DT) and continuous-time (CT) operation modes, along with a highly routable connection boxes (CBs) based interconnection lattice. The dual mode circuit for the FPAA is capable of achieving targeted optimal performance in different applications. The architecture utilizes routing switches in a CB not only for the signal interconnection purpose but also for control of the electrical charge transfer required in switched-capacitor circuits. This way, the performance of the circuit in either mode shall not be hampered with adding of programmability. The proposed FPAA is designed and implemented in a 0.18 μm standard CMOS process with a 3.3 V supply voltage. The result from post-layout simulation shows that a maximum bandwidth of 265 MHz through the interconnection network is achieved. The measured results from demonstrated examples show that the maximum signal bandwidth of up to 2 MHz in CT mode is obtained with the spurious free dynamic range of 54 dB, while the signal processing precision in DT mode reaches 96.4%. -

References

[1] Sivilotti M A. A dynamically configurable architecture for prototyping analog circuits. Proceedings of the Fifth MIT Conference on Advanced Research in VLSI, MIT, 1988:237[2] Becker J, Henrici F, Trendelenburg S, et al. A field-programmable analog array of 55 digitally tunable OTAs in a hexagonal lattice. IEEE J Solid-State Circuits, 2008, 43(12):2759 doi: 10.1109/JSSC.2008.2005697[3] Stoica A, Zebulum R, Keymeulen D, et al. Reconfigurable VLSI architectures for evolvable hardware:from experimental field programmable transistor arrays to evolution-oriented chips. IEEE Trans Very Large Scale Integration (VLSI) Systems, 2001, 9(1):227 doi: 10.1109/92.920839[4] Lee E K F, Gulak P G. A CMOS field-programmable analog array. IEEE J Solid-State Circuits, 1991, 26(12):1860 doi: 10.1109/4.104162[5] Basu A, Brink S, Schlottmann C, et al. A floating-gate-based field-programmable analog array. IEEE J Solid-State Circuits, 2010, 45(9):1781 doi: 10.1109/JSSC.2010.2056832[6] Luo J. Circuit design and routing for field programmable analog arrays. Doctor of Philosophy, Department of Electrical and Computer Engineering, University of Maryland, 2005[7] Cheng X Y, Yin T, Wu Q S, et al. A CMOS FIELD programmable analog array for intelligent sensory application. 23rd International Conference on Field Programmable Logic and Applications, Porto, Portugal, 2013:2[8] Hasler P E, Twigg C M. An OTA-based large-scale field programmable analog array (FPAA) for faster on-chip communication and computation. IEEE International Symposium on Circuits and Systems, 2007:177[9] Brown T W, Fie T S Z, Hakkarainen M. Prediction and characterization of frequency dependent MOS switch linearity and the design implications. CICC, 2006 http://ieeexplore.ieee.org/document/4114948/[10] Gregorian R, Temes G C. Analog MOS integrated circuits for signal processing. John Wiley & Sons, 1986[11] Mohan P V A, Ramachandran V, Swamy M N S. Switched capacitor filters:theory, analysis and design. Prentice Hall, 1995[12] Moldovan L, Li H H. A rail-to-rail, constant gain, buffered op-amp for real time video applications. IEEE J Solid-State Circuits, 1997, 32(2):169 doi: 10.1109/4.551908[13] Hogervorst R, Tero J P, Eschauzier R G H, et al. A compact power-efficient 3 V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries. IEEE J Solid-State Circuits, 1994, 29(12):1505 doi: 10.1109/4.340424[14] Carrillo J M, Duque-Carrillo J F, Torelli G, et al. Constant-gm constant-slew-rate high-bandwidth low-voltage rail-to-rail CMOS input stage for VLSI cell libraries. IEEE J Solid-State Circuits, 2003, 38(8):1364 doi: 10.1109/JSSC.2003.814430[15] Fu W H, Jiang J, Qin X, et al. A reconfigurable analog processor using coarse-grained, heterogeneous configurable analog blocks for field programmable mixed-signal processing. Analog Integr Circuits Signal Process, 2011, 2011(68):93[16] Wunderlich R B, Adil F, Hasler P. Floating gate-based field programmable mixed-signal array. IEEE Trans Very Large Scale Integration (VLSI) System, 2013, 21(8):1496 doi: 10.1109/TVLSI.2012.2211049 -

Proportional views

DownLoad:

DownLoad: