| Citation: |

Huabin Chen, Jixuan Xiang, Xiangyan Xue, Chixiao Chen, Fan Ye, Jun Xu, Junyan Ren. An analog front end with a 12-bit 3.2-MS/s SAR ADC for a power line communication system[J]. Journal of Semiconductors, 2014, 35(11): 115008. doi: 10.1088/1674-4926/35/11/115008

****

H B Chen, J X Xiang, X Y Xue, C X Chen, F Ye, J Xu, J Y Ren. An analog front end with a 12-bit 3.2-MS/s SAR ADC for a power line communication system[J]. J. Semicond., 2014, 35(11): 115008. doi: 10.1088/1674-4926/35/11/115008.

|

An analog front end with a 12-bit 3.2-MS/s SAR ADC for a power line communication system

DOI: 10.1088/1674-4926/35/11/115008

More Information

-

Abstract

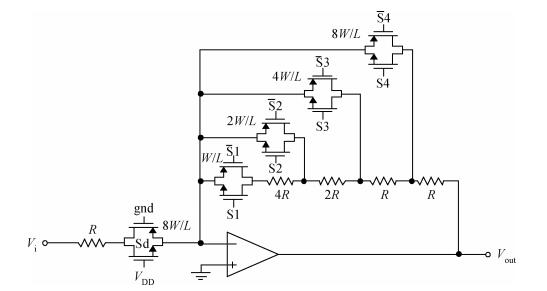

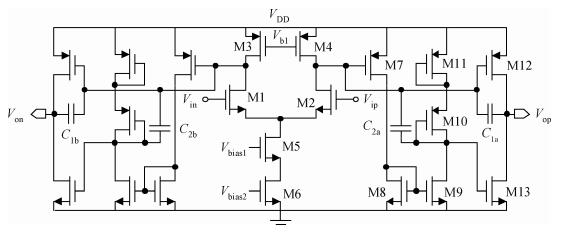

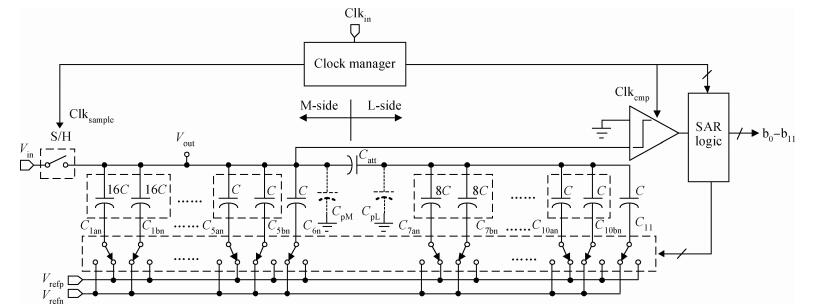

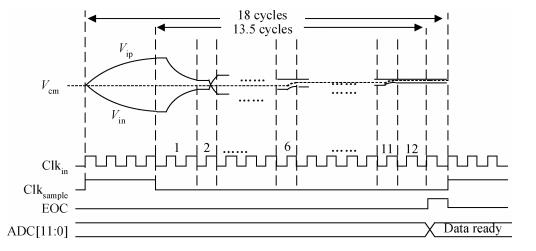

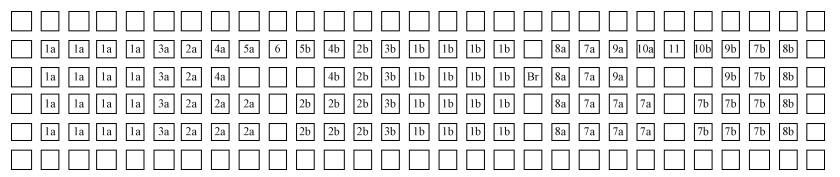

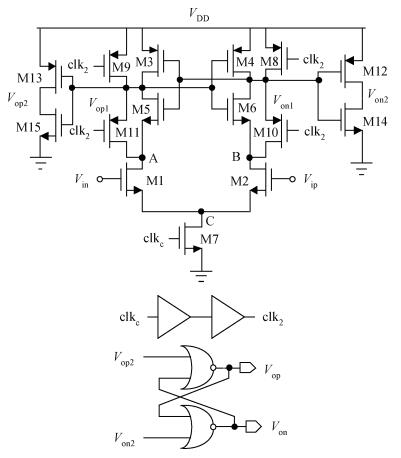

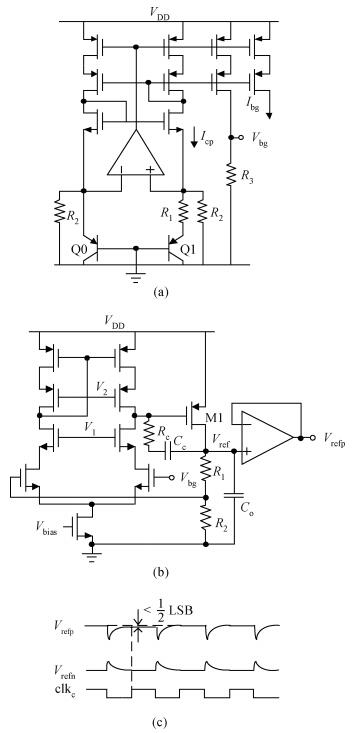

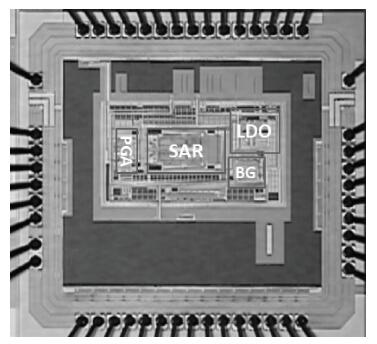

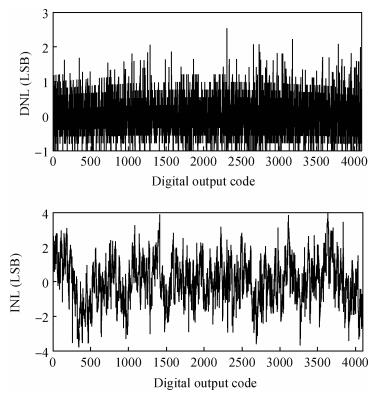

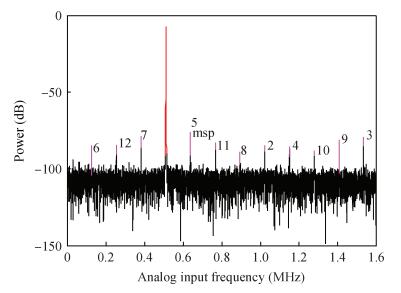

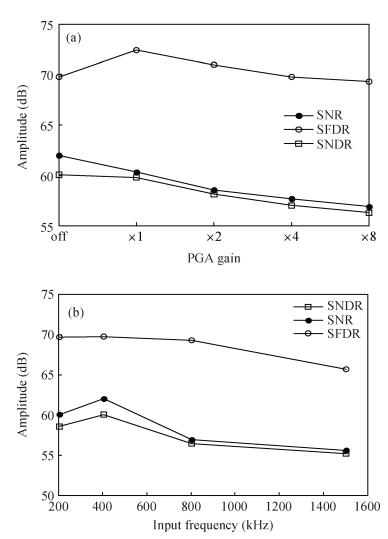

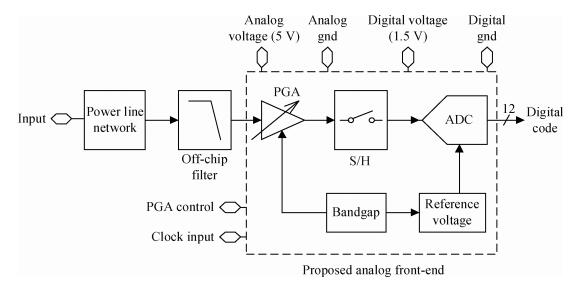

This paper presents an analog front end for a power line communication system, including a 12-bit 3.2-MS/s energy-efficient successive approximation register analog-to-digital converter, a positive feedback programmable gain amplifier, a 9.8 ppm/℃ bandgap reference and on-chip low-output voltage regulators. A two segment capacitive array structure (6 MSB 5 LSB) composed by split capacitors is designed for the SAR core to save area cost and release reference voltage accuracy requirements. Implemented in the GSMC 0.13 μm 1.5 V/12 V dual-gate 4P6M e-flash process, the analog front end occupies an area of 0.457 mm2 and consumes power of 18.8 mW, in which 1.1 mW cost by the SAR ADC. Measured at 500 kHz input, the spurious-free dynamic range and signal-to-noise plus distortion ratio of the ADC are 71.57 dB and 60.60 dB respectively, achieving a figure of merit of 350 fJ/conversion-step. -

References

[1] Bumiller G, Lampe L, Hrasnica H. Power line communication networks for large-scale control and automation systems. IEEE Commun Mag, 2010, 48:106[2] Young-Sung S, Pulkkinen T, Kyeong D M, et al. Home energy management system based on power line communication. IEEE Consumer Electronics Society, 2010, 56:1380 doi: 10.1109/TCE.2010.5606273[3] Zhai M Y. Transmission characteristics of low-voltage distribution networks in China under the smart grids environment. IEEE Power & Energy Society, 2011, 26:173[4] Chen Y, Tsukamoto S, Kuroda T. A 9 b 100 MS/s 1.46 mW SAR ADC in 65 nm CMOS. IEEE Asian Solid-State Circuits Conference, 2009:145[5] Harpe P, Zhou C, Wang X, et al. A 12 fJ/conversion-step 8 bit 10 MS/s asynchronous SAR ADC for low energy radios. IEEE ESSCIRC, 2010:214[6] Wu W L, Zhu Y, Ding L, et al. A 0.6 V 8 b 100 MS/s SAR ADC with minimized DAC capacitor and switching energy in 65 nm CMOS. IEEE Circuits and Systems (ISCAS), 2013:2239[7] Deng L, Yang C, Zhao M, et al. A 12-bit 200 kS/s SAR ADC with a mixed switching scheme and integer-based split capacitor array. IEEE New Circuits and Systems Conference (NEWCAS), 2013:1[8] Fan H, Han X, Wei Q, et al. A 12-bit self-calibrating SAR ADC achieving a Nyquist 90.4-dB SFDR. Analog Integrated Circuits and Signal Processing, 2013, 74(1):239 doi: 10.1007/s10470-012-9977-6[9] Liu C C, Chang S J, Huang G Y, et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 2010, 45(4):731 doi: 10.1109/JSSC.2010.2042254[10] Hariprasath V, Guerber J, Lee S H, et al. Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electron Lett, 2010, 46(9):620 doi: 10.1049/el.2010.0706[11] Yang Siyu, Zhang Hui, Fu Wenhui, et al. A low power 12-bit 200-kS/s SAR ADC with a differential time domain comparator. Journal of Semiconductors, 2011, 32(3):035002 doi: 10.1088/1674-4926/32/3/035002[12] Qiao Ning, Zhang Guoquan, Yang Bo, et al. A 10-bit 50-MS/s reference-free low power SAR ADC in 0.18-μm SOI CMOS technology. Journal of Semiconductors, 2012, 33(9):095005. doi: 10.1088/1674-4926/33/9/095005[13] Ma Jun, Guo Yawei, Wu Yue, et al. A 1-V 10-bit 80-MS/s 1.6-mW SAR ADC in 65-nm GP CMOS. Journal of Semiconductors, 2013, 34(8):085014 doi: 10.1088/1674-4926/34/8/085014 -

Proportional views

DownLoad:

DownLoad: