| Citation: |

Minzeng Li, Fule Li, Chun Zhang, Zhihua Wang. Pixel-level A/D conversion using voltage reset technique[J]. Journal of Semiconductors, 2014, 35(11): 115009. doi: 10.1088/1674-4926/35/11/115009

****

M Z Li, F L Li, C Zhang, Z H Wang. Pixel-level A/D conversion using voltage reset technique[J]. J. Semicond., 2014, 35(11): 115009. doi: 10.1088/1674-4926/35/11/115009.

|

Pixel-level A/D conversion using voltage reset technique

DOI: 10.1088/1674-4926/35/11/115009

More Information

-

Abstract

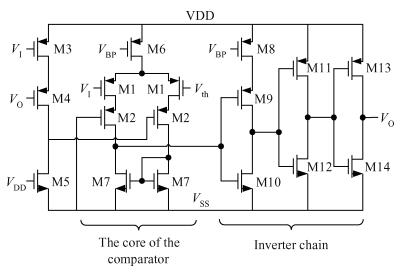

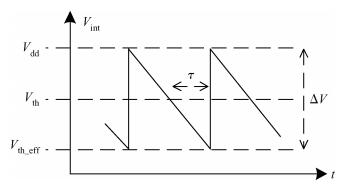

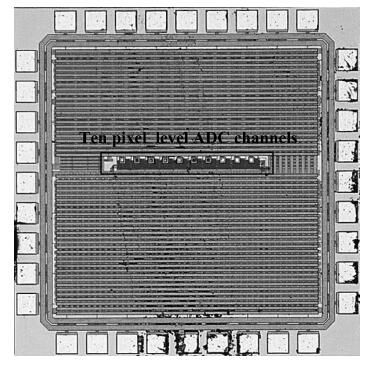

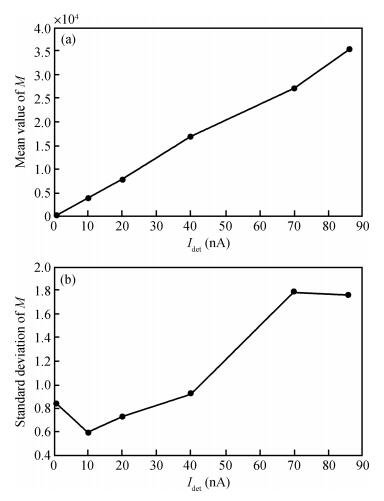

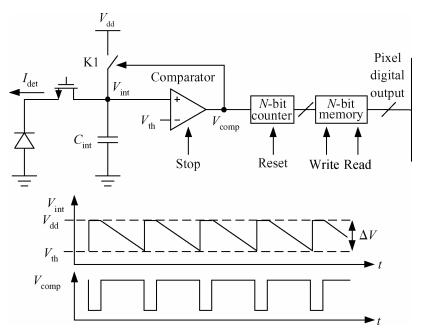

This paper presents a 50 Hz 15-bit analog-to-digital converter (ADC) for pixel-level implementation in CMOS image sensors. The ADC is based on charge packets counting and adopts a voltage reset technique to inject charge packets. The core circuit for charge/pulse conversion is specially optimized for low power, low noise and small area. An experimental chip with ten pixel-level ADCs has been fabricated and tested for verification. The measurement result shows a standard deviation of 1.8 LSB for full-scale output. The ADC has an area of 45×45 μm2 and consumes less than 2 μW in a standard 1P-6M 0.18 μm CMOS process. -

References

[1] Loinaz M J, Singh K J, Blanksby A J, et al. A 200 mW 3.3 V CMOS color camera IC producing 352×28824 b video at 30 frames/s. IEEE J Solid-State Circuit, 1998, 33(12):2092 doi: 10.1109/4.735552[2] Smith S, Hurwitz J, Torrie M, et al. A single-chip 306×244-pixel CMOS NTSC video camera. IEEE International Solid-State Circuit Conference, 1998:170[3] Snoeij M F, Theuwissen A J P, Makinwa K A A, et al. A CMOS image with column-level ADC using dynamic column fixed-pattern noise reduction. IEEE J Solid-State Circuits, 2006, 41(12):3007 doi: 10.1109/JSSC.2006.884866[4] Han Ye, Li Quanliang, Shi Cong, et al. A 10-bit column-parallel cyclic ADC for high-speed CMOS image sensors. Journal of Semiconductors, 2013, 34(8):085016 doi: 10.1088/1674-4926/34/8/085016[5] Snoeij M F, Donegan P, Theuwissen A J P, et al. A CMOS image sensor with a column-level multiple-ramp single-slope ADC. IEEE International Solid-State Circuit Conference, 2007:506[6] Li Y, Jiang L, Ji Z. Design of a low power high speed auto-zeroed column-level ADC for data readout of CMOS APS based vertex detector. 16th IEEE NPSS Real Time Conference, 2009:295[7] Mahmoodi A, Joseph D. Optimization of delta-sigma ADC for column-level data conversion in CMOS image sensor. IEEE Instrumentation and Measurement Technology Conference (IMTC), 2007:1[8] Peizerat A, Arques M, Villard P, et al. Pixel-level A/D conversion:comparison of two charge packets counting techniques. International Image Sensor Workshop (ⅡSW), 2007:200[9] Fowler B, Gamal A E, Yang D X D. A CMOS area image sensor with pixel-level A/D conversion. IEEE International Solid-State Circuit Conference, 1994:226[10] Mahmoodi A, Joseph D. Pixel-level delta-sigma ADC with optimized area and power for vertically-integrated image sensors. Midwest Symposium on Circuit and System (MWSCAS), 2008:41[11] Yang D X D, Fowler B, Gamal A E. A 128×128 pixel CMOS area image sensor with multiplexed pixel level A/D conversion. IEEE Custom Integrated Circuits Conference, 1996:303[12] Yang D X D, Fowler B, Gamal A E. A nyquist rate pixel level ADC for CMOS image sensors. IEEE J Solid-State Circuits, 1999, 34(3):348 doi: 10.1109/4.748186[13] Hashemi F, Hadidi K H, Khoei A. Design of A CMOS image sensor with pixel-level ADC in 0.35μm process. International Symposium on Circuit and Systems, 2003, 2:600[14] Reckleben C, Hansen K, Kalavakuru P, et al. 8-bit 5-MS/s per-pixel ADC in an 8-by-8 matrix. IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), 2011:668[15] Right U, Janson C, Liddiard K C. Readout concept employing a novel on-chip 16-bit ADC for smart IR focal plane arrays. Infrared Readout Electronics Ⅲ, 1996, 2745:99 doi: 10.1117/12.243528[16] Tchagaspanian M, Villard P, Dupont B, et al. Design of ADC in 25μm pixels pitch dedicated for IRFPA image processing at LETI. Proc SPIE, 2007 -

Proportional views

DownLoad:

DownLoad: