| Citation: |

Xurui Mao, Beiju Huang, Hongda Chen. A 900 MHz fractional-N synthesizer for UHF transceiver in 0.18 μm CMOS technology[J]. Journal of Semiconductors, 2014, 35(12): 125007. doi: 10.1088/1674-4926/35/12/125007

****

X R Mao, B J Huang, H D Chen. A 900 MHz fractional-N synthesizer for UHF transceiver in 0.18 μm CMOS technology[J]. J. Semicond., 2014, 35(12): 125007. doi: 10.1088/1674-4926/35/12/125007.

|

A 900 MHz fractional-N synthesizer for UHF transceiver in 0.18 μm CMOS technology

DOI: 10.1088/1674-4926/35/12/125007

More Information

-

Abstract

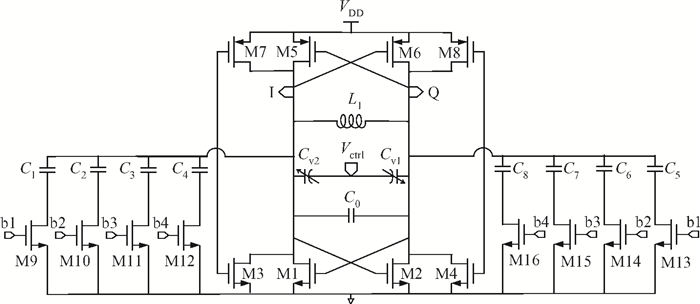

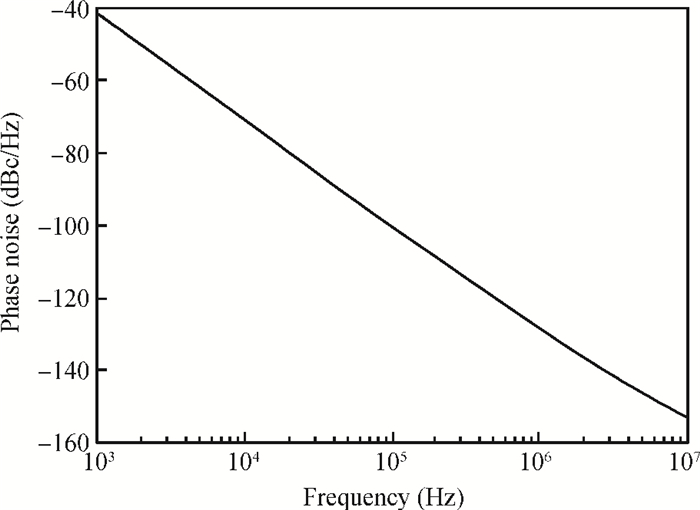

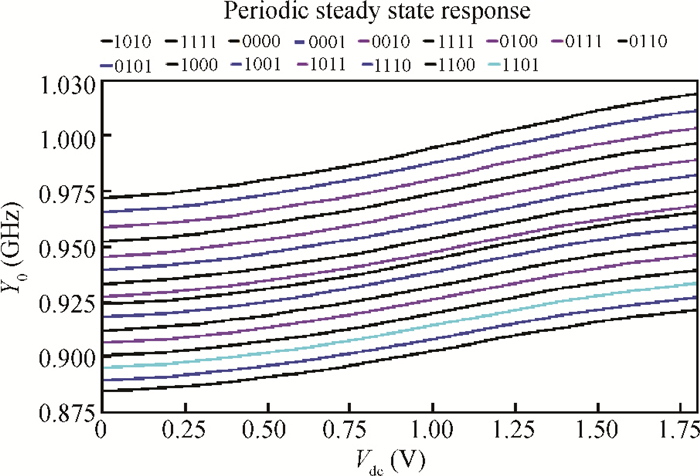

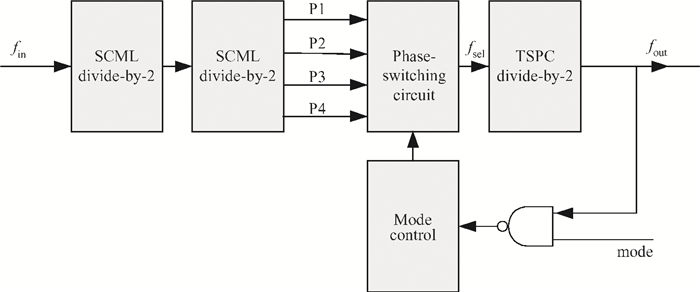

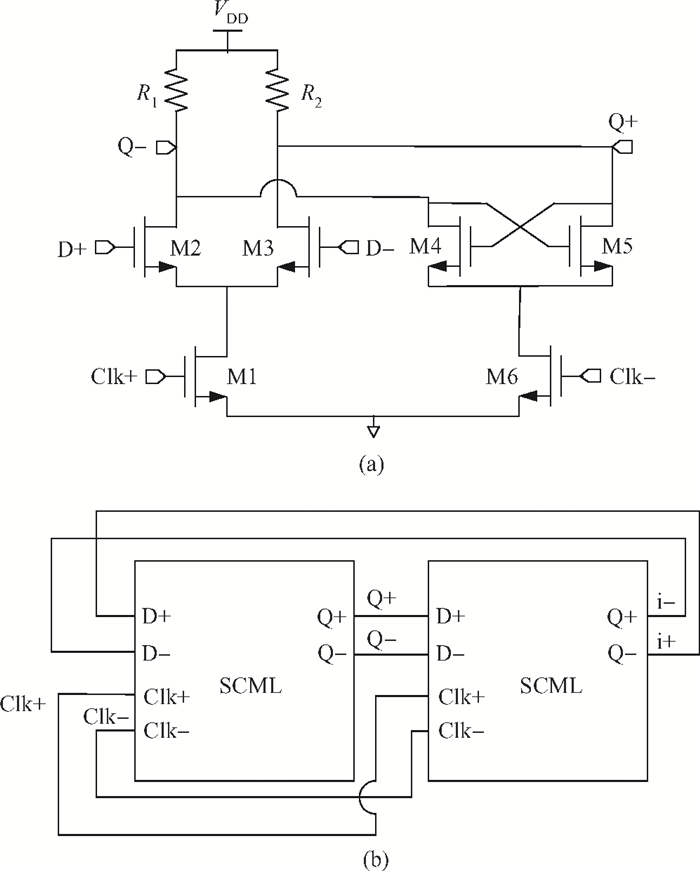

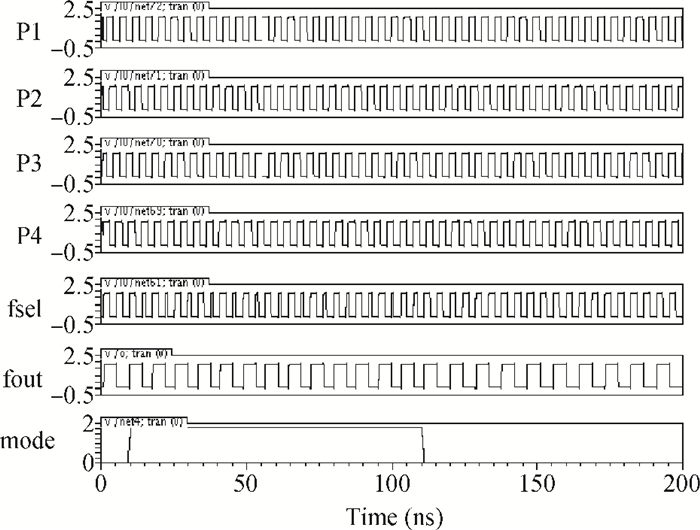

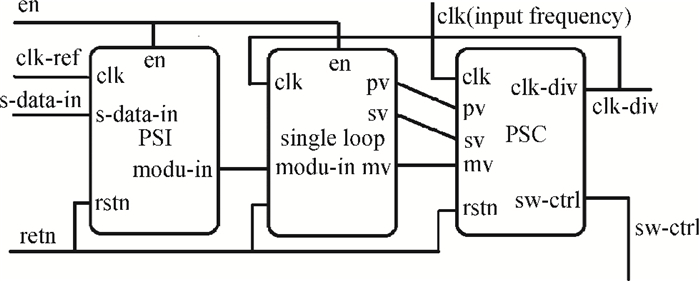

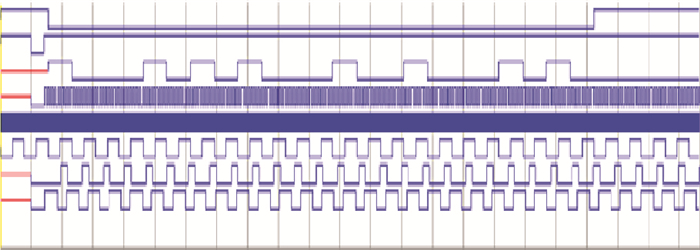

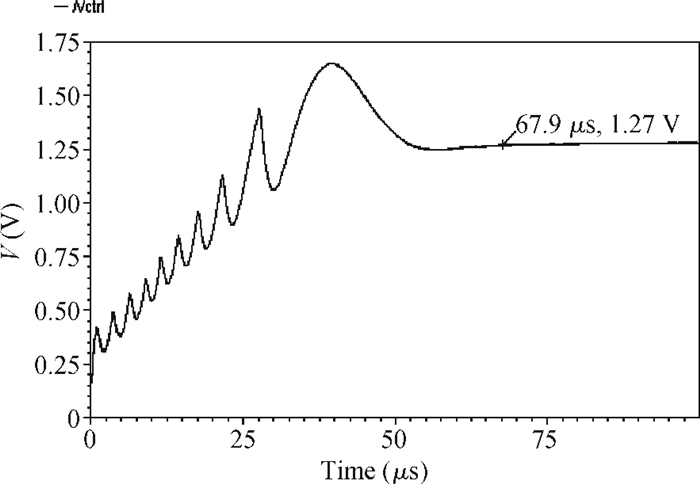

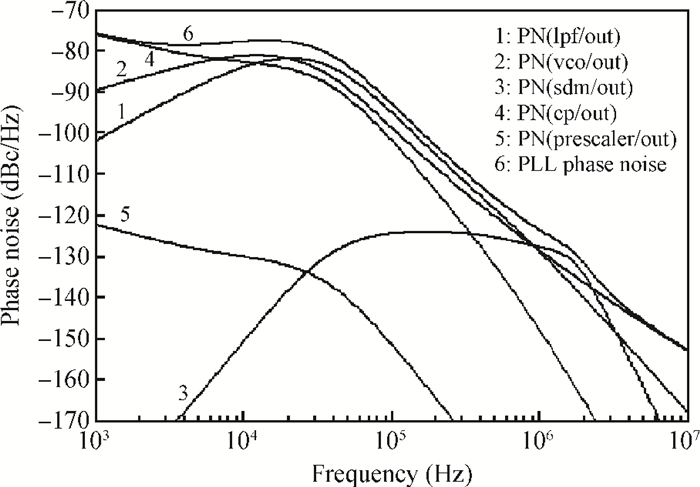

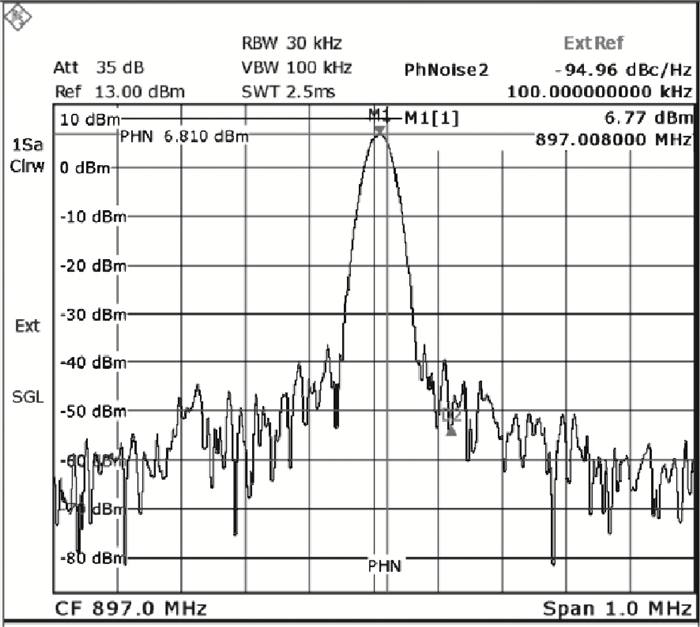

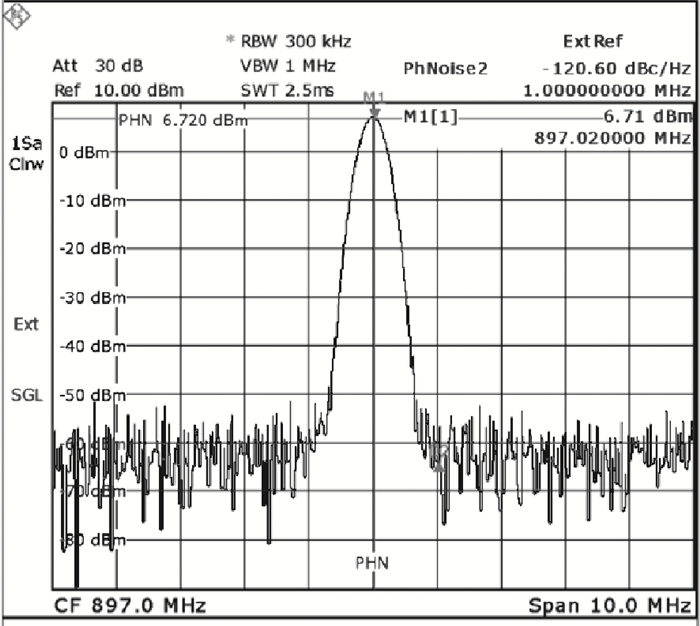

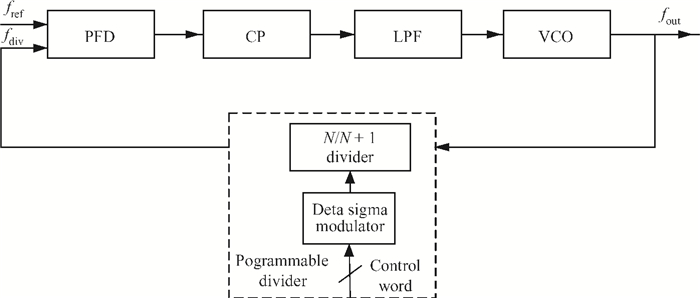

A 900 MHz fractional-N synthesizer is designed for the UHF transceiver. The VCO with a 4 bits capacitor bank covers 823-1061 MHz that implements 16 (24) sub-bands. A 7/8 dual-modulus prescaler is implemented with a phase-switching circuit and high-speed flip-flops, which are composed of source coupled logic. The proposed synthesizer phase-locked loop is demonstrated with a 50 kHz band width by a low 12.95 MHz reference clock, and offers a better phase noise and band width tradeoff. To reduce the out-band phase noise, a 4-levels 3-order single-loop sigma-delta modulator is applied. When its relative frequency resolution is settled to 10-6, the testing results show that the phase noises are -120.6 dBc/Hz at 1 MHz and -95.0 dBc/Hz at 100 kHz. The chip is 2.1 mm2 in UMC 0.18 μm CMOS. The power is 36 mW at a 1.8 V supply. -

References

[1] Wu T, Hanumolu P K, Mayaram K, et al. Method for constant loop bandwith in LC-VCO PLL frequency synthesizers. IEEE J Solid-State Circuits, 2009, 44(2):427 doi: 10.1109/JSSC.2008.2010792[2] Lo C, Luong H. A 1.5-V 900-MHz monolithic CMOS fast-switching frequency synthesizer for wireless applications. IEEE J Solid-State Circuits, 2002, 37(4):459 doi: 10.1109/4.991384[3] Shin J, Shin H. A fast and high-precision VCO frequency calibration technique for wideband Δ Σ fractional-N frequency synthesizers. IEEE Trans Circuits Syst I, 2010, 57(7):1573 doi: 10.1109/TCSI.2009.2036057[4] Nonis R, Dalt N D, Palestri P, et al. Modeling, design and characterization of a new low-jitter analog dual tuning LC-VCO PLL architecture. IEEE J Solid-State Circuits, 2005, 40(6):1303 doi: 10.1109/JSSC.2005.848037[5] Nakamura T, Masuda T, Nobuhiro, et al. A wide-tuning-range VCO with small VCO-gain fluctuation for multi-band WCDMA RFIC. Proceedings 32nd European Solid-State Circuits Conference, 2006:448 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4099800[6] Ding Y, Kenneth K O. A 21 GHz 8 modulus prescaler and a 20 GHz phase locked loop fabricated in 130 nm CMOS. IEEE J Solid-State Circuits, 2007, 42(2):1240 http://ieeexplore.ieee.org/document/4214963/[7] Yuan J, Svensson C. High speed CMOS circuit technique. IEEE J Solid-State Circuits, 1989, 24(2):62 http://ieeexplore.ieee.org/document/16303/[8] Chang B, Park J, Kim W. A 1.2 GHz CMOS dual modulus prescaler using new dynamic d-type flip-flops. IEEE J Solid-State Circuits, 1996, 31(5):749 doi: 10.1109/4.509860[9] Muer B D, Steyaert M. A CMOS monolithic Δ Σ -controlled fractional-N frequency synthesizer for DCS-1800. IEEE J Solid-State Circuits, 2002, 37(7):835 doi: 10.1109/JSSC.2002.1015680[10] Muer B D, Steyaert M. On the analysis of delta sigma fractiona-N frequency synthesizers for high-spectral purity. IEEE Trans Circuits Syst Ⅱ:Analog and Digital Signal Processing, 2003, 50(11):784 doi: 10.1109/TCSII.2003.819119[11] Lee H I, Cho J K, Lee K S, et al. (2004). A Δ Σ fractional-N frequency synthesizer using a wide-band integrated VCO and a fast AFC technique for GSM/GPRS/WCDMA applications. IEEE J Solid-State Circuits, 2004, 39(7):1164 doi: 10.1109/JSSC.2004.829938[12] Wang W T, Lou S Z, Chui K, et al. A single-chip UHF RFID reader in 0.18μm CMOS process. IEEE J Solid-State Circuits, 2008, 43(8):1741 doi: 10.1109/JSSC.2008.925601[13] Kwon I, Bang H, Choi K, et al. A single-chip CMOS transceiver for UHF mobile RFID reader. IEEE J Solid-State Circuits, 2008, 43(3):216 http://ieeexplore.ieee.org/document/4456779/[14] Xie Weifu, Li Yongming, Zhang Chun, et al. CMOS implementation of an RF PLL synthesizer for use in RFID systems. Journal of Semiconductors, 2008, 29(8):1595 http://www.jos.ac.cn/bdtxbcn/ch/reader/view_abstract.aspx?flag=1&file_no=07092602&journal_id=bdtxbcn[15] Shin J, Shin H. A 1.9-3.8 GHz Δ Σ fractional-N PLL frequency synthesizer with fast auto-calibration of loop bandwidth and VCO frequency. IEEE J Solid-State Circuits, 2012, 47(3):665 doi: 10.1109/JSSC.2011.2179733[16] Yan D L, Bansal A, Zhao B, et al. A low power, 900 MHz fractional-N synthesizer with quadrature outputs in 0. 13μm CMOS. IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-BIO), 2013: 1 -

Proportional views

DownLoad:

DownLoad: