| Citation: |

Haijun Wu, Bin Li, Huabin Zhang, Zhengping Li, Longyue Zeng. A single die 1.2 V 55 to 95 dB DR delta sigma ADC with configurable modulator and OSR[J]. Journal of Semiconductors, 2014, 35(3): 035003. doi: 10.1088/1674-4926/35/3/035003

****

H J Wu, B Li, H B Zhang, Z P Li, L Y Zeng. A single die 1.2 V 55 to 95 dB DR delta sigma ADC with configurable modulator and OSR[J]. J. Semicond., 2014, 35(3): 035003. doi: 10.1088/1674-4926/35/3/035003.

|

A single die 1.2 V 55 to 95 dB DR delta sigma ADC with configurable modulator and OSR

DOI: 10.1088/1674-4926/35/3/035003

More Information

-

Abstract

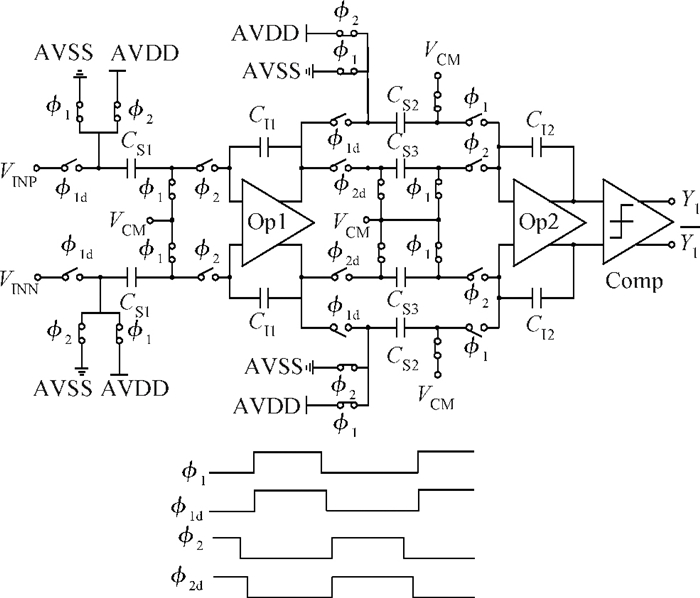

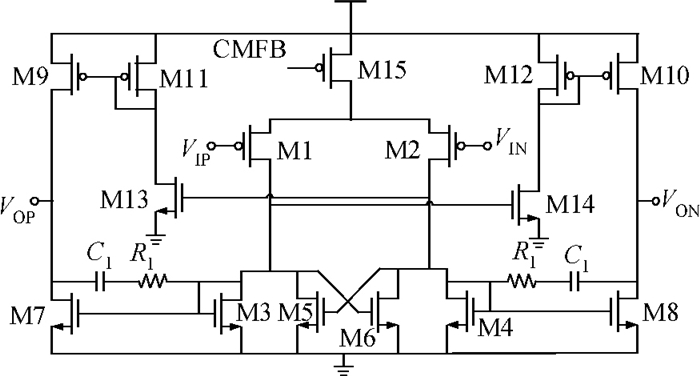

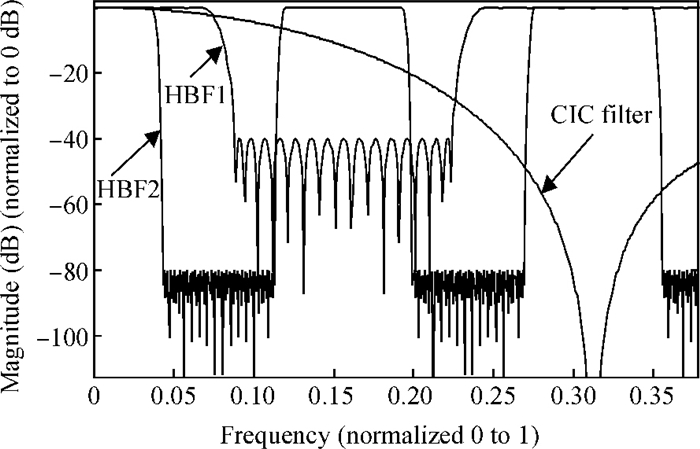

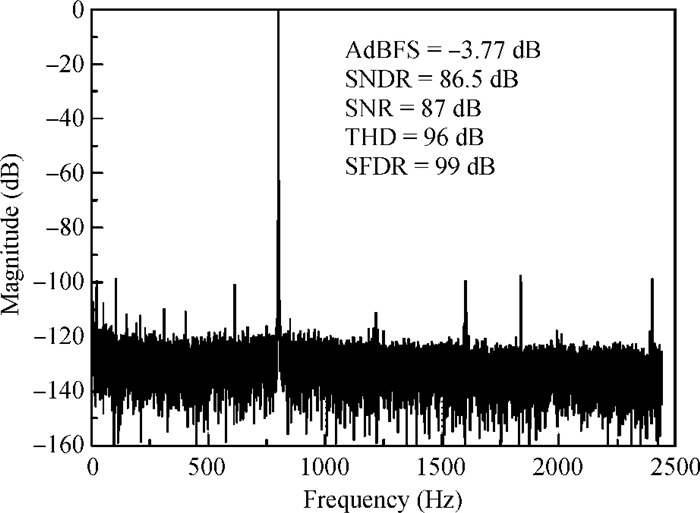

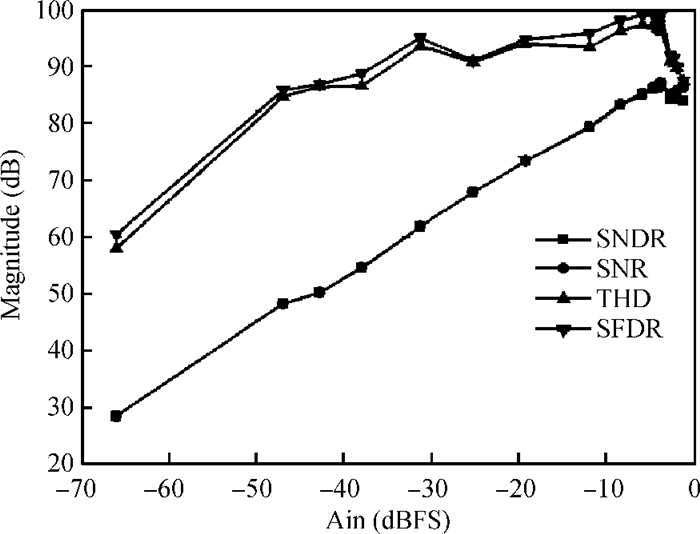

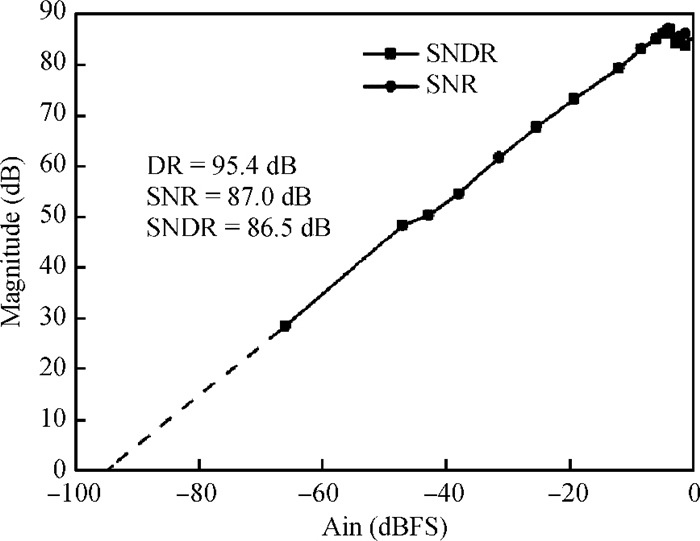

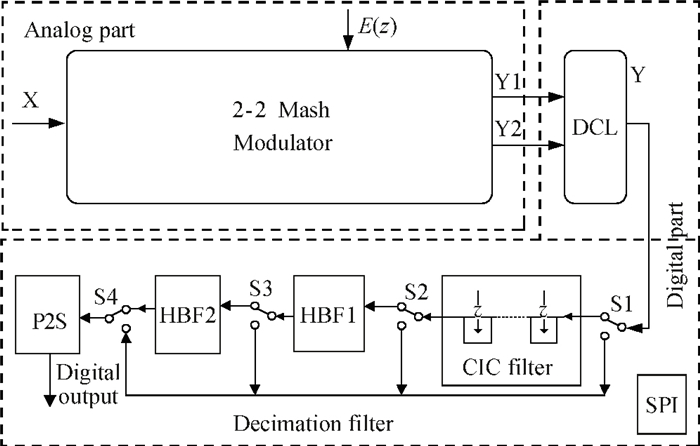

A single die 1.2 V multi-stage noise shaping (Mash) 2-2 delta sigma analog to digital converter (ADC) for wide applications is implemented. The configurable Mash 2-2 modulator with a new decimation filter design is presented to achieve wide and high dynamic range (DR) for multiple practical applications. The novel modulator can be configured as a Mash 2-2 modulator for high precision or a 2-order modulator for low DR. The decimation filter is designed to select the OSR flexibly among cascaded integrator comb (CIC) filter and two half-band filters (HBF). The serial peripheral interface (SPI) can be used to adjust the sampling frequency and the oversampling ratio (OSR). The design was fabricated in a 0.13 μm CMOS process with an area of 0.91 mm2 and a total power of 5.2 mW. The measurement results show that the dynamic range (DR) of the proposed ADC can change from 55 to 95 dB with the configurable OSR from 16 to 256. The spurious free dynamic range (SFDR) and signal-to-noise distortion ratio (SNDR) can get 99 dB and 86.5 dB, respectively.-

Keywords:

- delta sigma ADC,

- modulator,

- low power,

- decimation filter,

- configurable OSR

-

References

[1] Xie H L, Rakers P, Fernandez R, et al. Single-chip multi-band SAW-less LTE WCDMA and EGPRS CMOS receiver with diversity. IEEE Radio Frequency Integrated Circuits Symposium, 2011:1 http://ieeexplore.ieee.org/xpl/abstractKeywords.jsp?reload=true&arnumber=5940614[2] Ahmed S, Mohamed A, Markus B, et al. A power-efficient tunable narrow-band digital front end for bandpass sigma-delta ADCs in digital FM receivers. IEEE Trans Circuits & Syst Ⅱ, 2010, 59(1):30 http://ieeexplore.ieee.org/abstract/document/5618554[3] Koli K, Kallioinen S, Jussila J, et al. A 900-MHz direct delta-sigma receiver in 65-nm CMOS. IEEE J Solid-State Circuits, 2010, 45(12):2807 doi: 10.1109/JSSC.2010.2075270[4] Arias J, Boccuzzi V, Quintanilla L, et al. Low pipeline ADC for wireless LANs. IEEE J Solid-State Circuits, 2004, 39(8):1338 doi: 10.1109/JSSC.2004.831477[5] Pieter C, Geert V, Michiel S, et al. A single-bit 500 kHz-10 MHz multimode power-performance scalable 83-to-67 dB DR CT Δ Σ for SDR in 90 nm digital CMOS. IEEE J Solid-State Circuits, 2010, 45(6):1159 doi: 10.1109/JSSC.2010.2046230[6] Wang J, Yang H, Wei R, et al. A fourth-order bandwidth-reconfigurable delta-sigma modulator for audio applications. Journal of Semiconductors, 2012, 33(7):075002 doi: 10.1088/1674-4926/33/7/075002[7] Ouzounov S, Veldhoven R, Bastiaansen C, et al. A 1.2 V 121-mode CT delta-sigma modulator for wireless receivers in 90 nm CMOS. IEEE ISSCC, 2007:242 doi: 10.1007/s10470-016-0907-x[8] Morgado A, Río R, Rosa J, et al. A 100 kHz-10 MHz BW, 78-to-52 dB DR, 4.6-to-11 mW flexible SC Δ Σ modulator in 1.2-V 90-nm CMOS. IEEE ESSCIRC, 2010:418 doi: 10.1007/978-1-4614-1371-4_12/fulltext.html[9] Bos L, Vandersteen G, Rombouts P, et al. Multi rate cascaded discrete-time low-pass Δ Σ modulator for GSM/Bluetooth/UMTS. IEEE J Solid-State Circuits, 2010, 45(6):1198 doi: 10.1109/JSSC.2010.2046240[10] Barrett C J. Low-power decimation filter design for multi-standard transceiver applications. Master of Science Dissertation, Department of Electron and Engineering, University of California at Berkeley, 1997 https://www2.eecs.berkeley.edu/Pubs/TechRpts/1997/3347.html[11] Maloberti F. Data converters. Netherlands:Springer, 2007:391 http://dl.acm.org/citation.cfm?id=1206404[12] Ro R, Medeiro F, Pérez B, et al. CMOS cascade sigma-delta modulators for sensors and telecom. Netherlands:Springer, 2006:27 doi: 10.1007/1-4020-4776-2[13] Kuo C, Shi D, Chang K. A low-voltage fourth-order cascade delta-sigma modulator in 0.18-μm CMOS. IEEE Trans Circuits & Syst Ⅰ, 2010, 57(9):2450 doi: 10.1023/A:1026265624740[14] Roh J, Byun S, Choi Y, et al. A 0.9-V 60-μ W 1-bit fourth-order delta-sigma modulator with 83-dB dynamic range. IEEE J Solid-State Circuits, 2008, 43(2):361 doi: 10.1109/JSSC.2007.914266[15] Schreier R, Temes G. Understanding delta-sigma data converters. New York:Wiley/IEEE Press, 2004[16] Ahn G, Chang D, Brown M, et al. A 0.6-V 82-dB delta-sigma audio ADC using switched-RC integrators. IEEE J Solid-State Circuits, 2005, 40(12):2398 doi: 10.1109/JSSC.2005.856286[17] Koen C, Michiel S. Design considerations for cascade Δ Σ ADC's. IEEE Trans Circuits & Syst Ⅱ, 2008, 55(5):389 http://dl.acm.org/citation.cfm?id=1464511.1464748&coll=DL&dl=GUIDE[18] Yang Y, Terry S, Jacob A. A single-die 124 dB stereo audio delta-sigma ADC with 111 dB THD. IEEE J Solid-State Circuits, 2008, 43(7):1657 doi: 10.1109/JSSC.2008.923731[19] Geerts Y, Steyaert M. A high-performance multi-bit sigma delta CMOS ADC. IEEE J Solid-State Circuits, 2000, 35(12):1829 doi: 10.1109/4.890296[20] Li Y, Qi D, Dong Y, et al. A 1-V 60-μ W 85-dB dynamic range continuous time third order sigma delta modulator. Journal of Semiconductors, 2009, 30(12):125001 doi: 10.1088/1674-4926/30/12/125001[21] Liu Y, Hua S, Wang D, et al. A continuous-time/discrete-time mixed audio-band sigma delta ADC. Journal of Semiconductors. 2011, 32(17):015004 http://www.jos.ac.cn/bdtxbcn/ch/reader/view_abstract.aspx?flag=1&file_no=10052002&journal_id=bdtxbcn[22] Liu L, Li D, Chen L, et al. A 1-V 15-bit audio-Δ Σ ADC in 0.18μm CMOS. IEEE Trans Circuits & Syst Ⅰ, 2012, 59(5):915 doi: 10.1007/s10470-005-6568-9[23] Prasad A, Chokhawala A. A 120 dB 300 mW stereo audio A/D converter with 110 dB THD+N. IEEE J Solid-State Circuits, 2004, 39(14):191 http://www.aes.org/e-lib/browse.cfm?elib=4720&turnmobile=on[24] Yao L, Michiel S. Steyaert J, et al. A 1-V 140-μ W 88-dB audio sigma-delta modulator in 90-nm CMOS. IEEE J Solid-State Circuits, 2009, 44(11):3211 doi: 10.1109/JSSC.2009.2033505[25] Roh J, Byun S, Choi Y, et al. A 0.9-V 60-μ W 1-bit fourth-order delta-sigma modulator with 83-dB dynamic range. IEEE J Solid-State Circuits, 2008, 43(2):368 https://www.infona.pl//resource/bwmeta1.element.ieee-art-000004444579[26] Thomas C. A 15-bit 140-μ W scalable-bandwidth inverter-based modulator for a MEMS microphone with digital output. IEEE J Solid-State Circuits, 2013, 48(7):1612 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=6495485&sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A6545290%29[27] Petrellis N, Birbas M. An ultra low die area 8-b ADC and its generic calibration logic. Analog Integrated Circuits and Signal Processing, 2011, 69(6):1 doi: 10.1007/s10470-011-9686-6[28] Lukas D, Franz K, Andreas S, et al. A 2.2 mW, continuous-time sigma delta ADC for voice coding with 95 dB dynamic range in a 65nm CMOS process. IEEE ESSCIRC, 2006:195 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=4099737[29] Min G, Ahn G, Hanumolu P, et al. A 0.9 V 92 dB double-sampled switched-RC delta-sigma audio ADC. IEEE J Solid-State Circuits, 2008, 43(5):1195 doi: 10.1109/JSSC.2008.920329[30] Agah A, Vleugels K, Griffin P, et al. A high-resolution low-power incremental ADC with extended range for biosensor arrays. IEEE J Solid-State Circuits, 2010, 45(6):1099 doi: 10.1109/JSSC.2010.2048493[31] Kuo C, Shi D, Chang K. A low-voltage fourth-order cascade delta-sigma modulator in 0.18-μm CMOS. IEEE Trans Circuits & Syst Ⅰ, 2010, 57(9):2450 doi: 10.1023/A:1026265624740[32] Yin S, Li X. A 1.2-V, 84-dB Δ Σ ADM in 0.18-μm digital CMOS technology. Journal of Semiconductors, 2013, 34(8):085003 doi: 10.1088/1674-4926/34/8/085003 -

Proportional views

DownLoad:

DownLoad: