| Citation: |

Han Wang, Maomao Sun. A dynamic-biased dual-loop-feedback CMOS LDO regulator with fast transient response[J]. Journal of Semiconductors, 2014, 35(4): 045005. doi: 10.1088/1674-4926/35/4/045005

****

H Wang, M M Sun. A dynamic-biased dual-loop-feedback CMOS LDO regulator with fast transient response[J]. J. Semicond., 2014, 35(4): 045005. doi: 10.1088/1674-4926/35/4/045005.

|

A dynamic-biased dual-loop-feedback CMOS LDO regulator with fast transient response

DOI: 10.1088/1674-4926/35/4/045005

More Information

-

Abstract

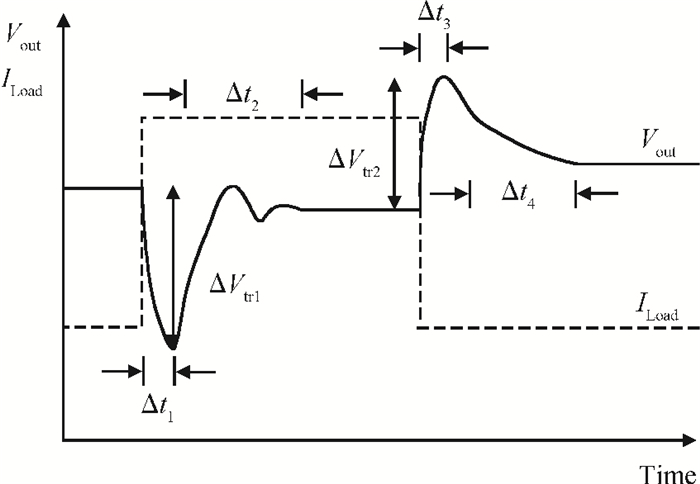

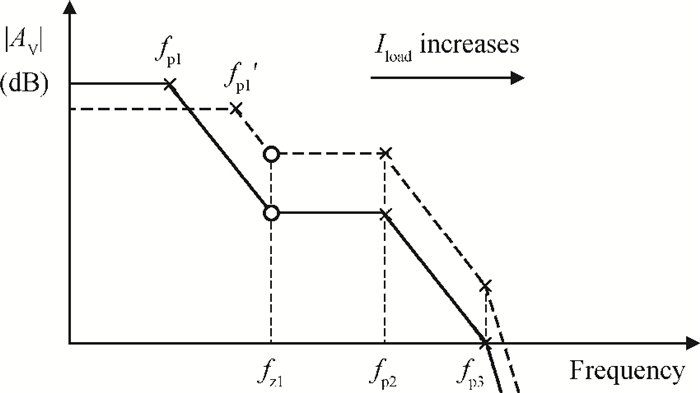

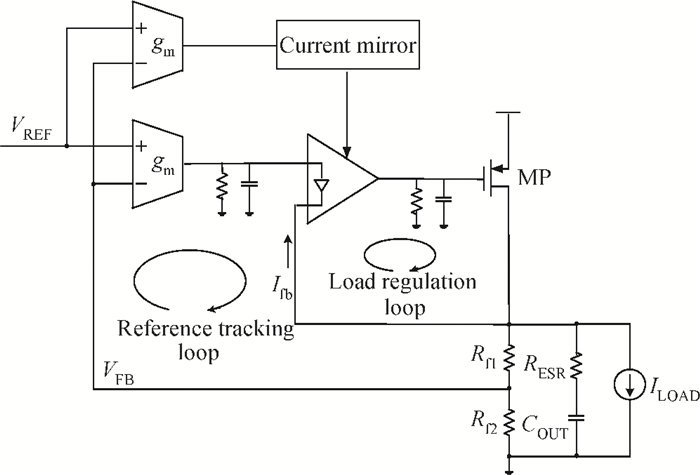

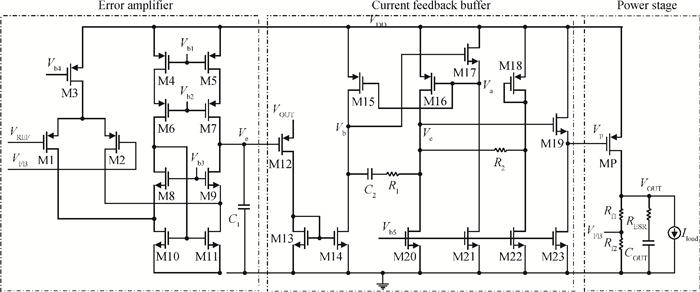

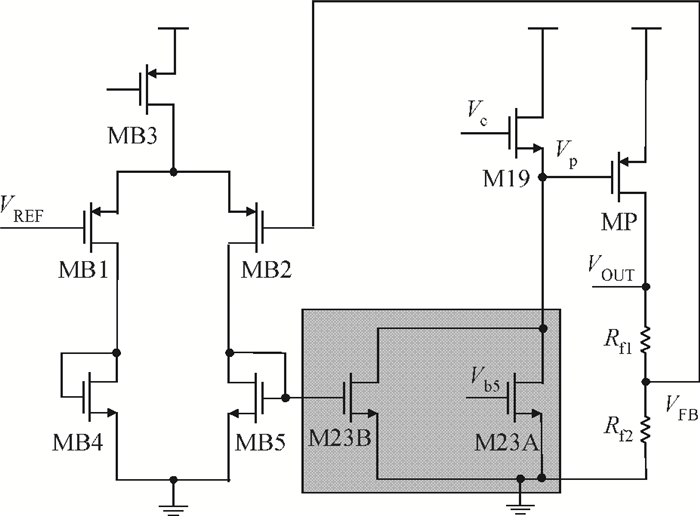

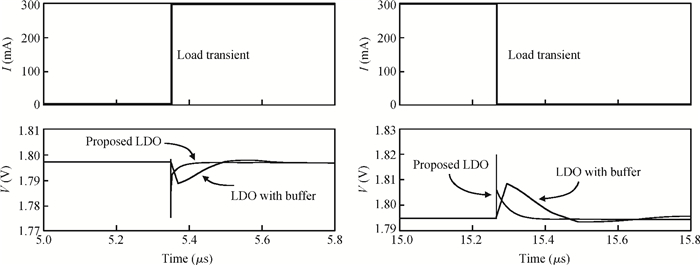

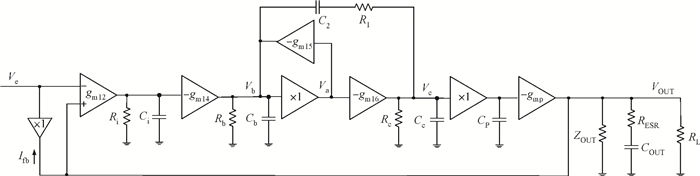

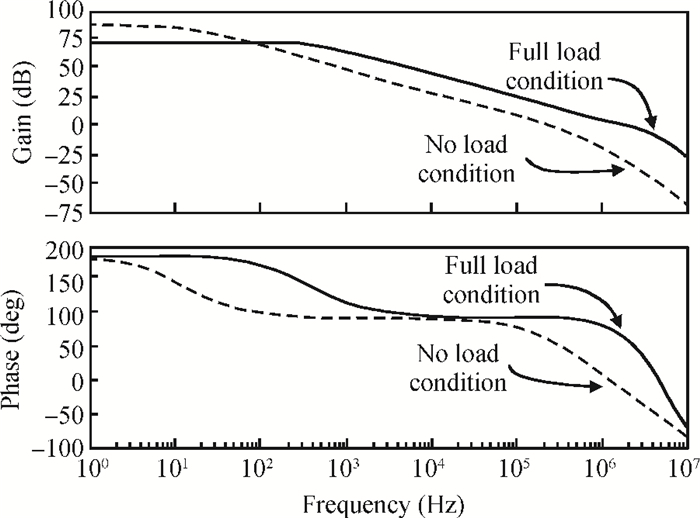

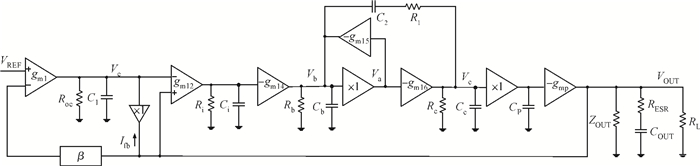

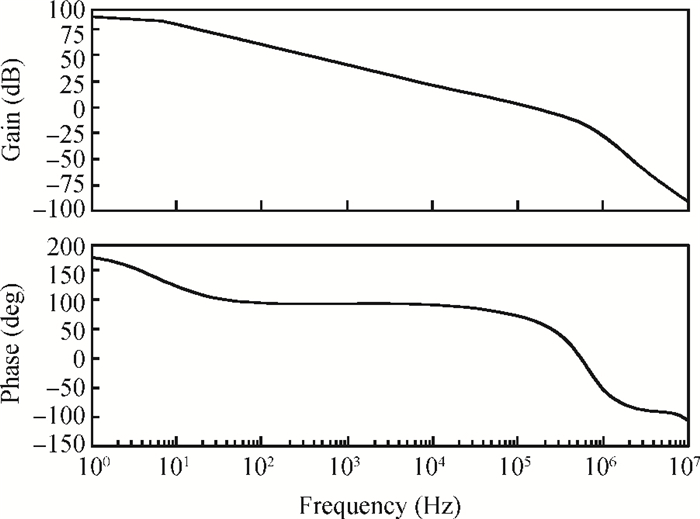

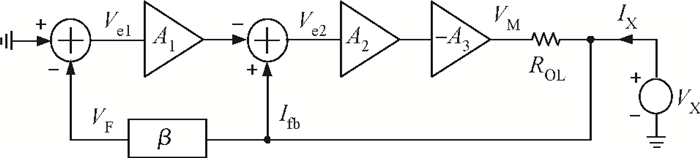

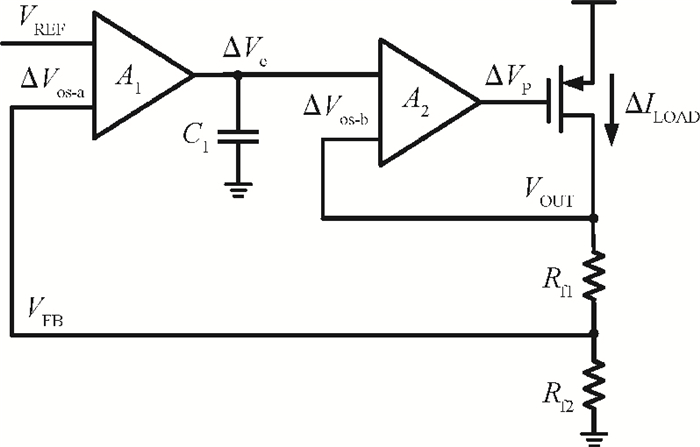

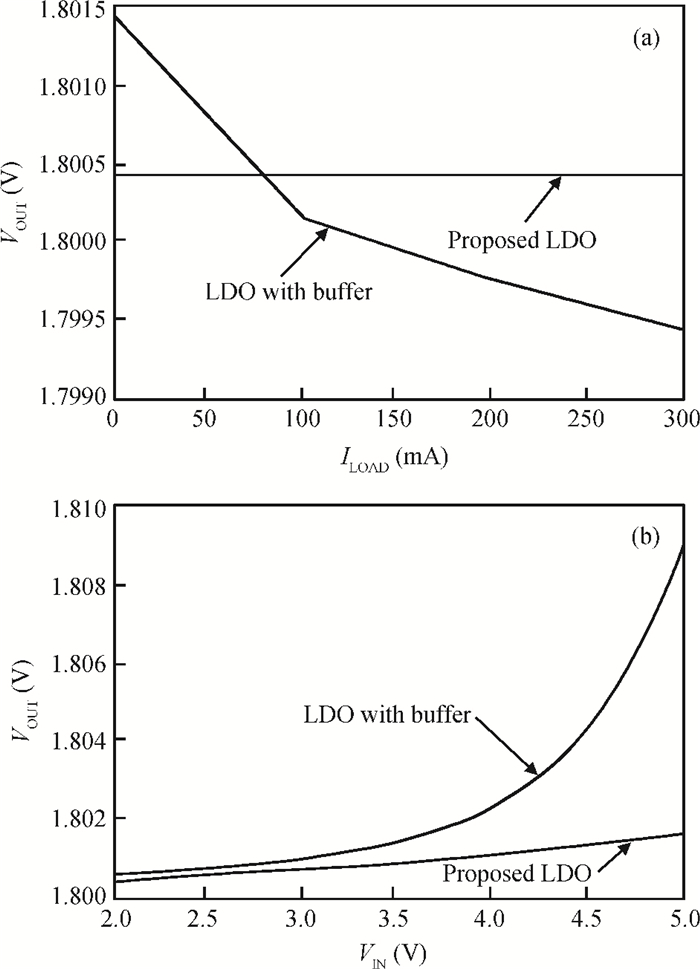

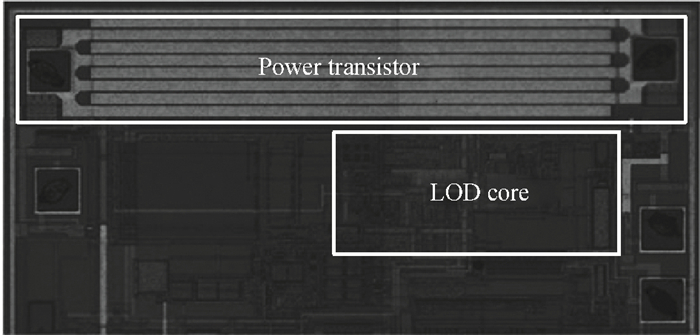

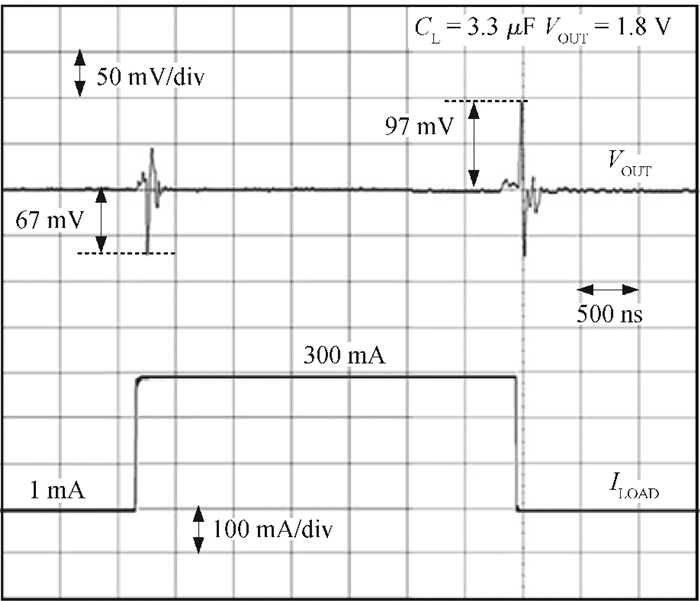

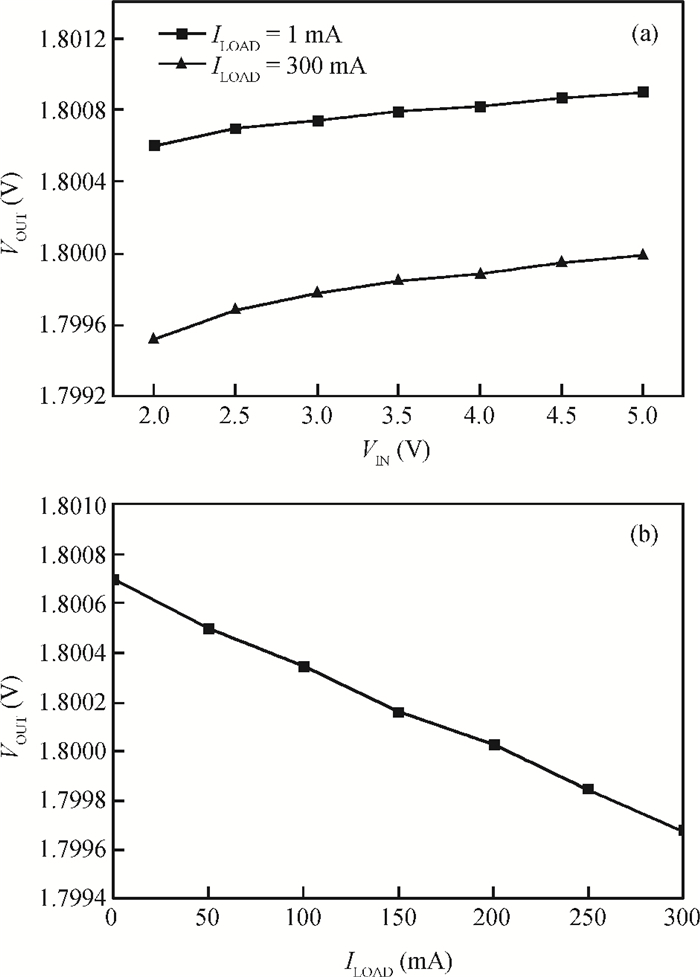

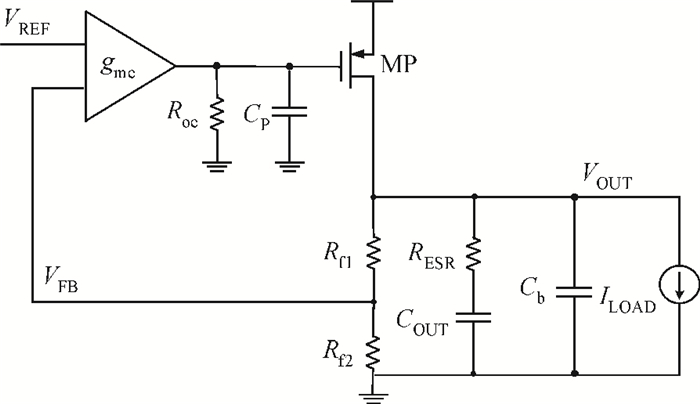

This paper presents a low-dropout regulator (LDO) for portable applications with dual-loop feedback and a dynamic bias circuit. The dual-loop feedback structure is adopted to reduce the output voltage spike and the response time of the LDO. The dynamic bias circuit enhances the slew rate at the gate of the power transistor. In addition, an adaptive miller compensation technique is employed, from which a single pole system is realized and over a 59° phase margin is achieved under the full range of the load current. The proposed LDO has been implemented in a 0.6-μm CMOS process. From the experimental results, the regulator can operate with a minimum dropout voltage of 200 mV at a maximum 300 mA load and IQ of 113 μA. The line regulation and load regulation are improved to 0.1 mV/V and 3.4 μV/mA due to the sufficient loop gain provided by the dual feedback loops. Under a full range load current step, the voltage spikes and the recovery time of the proposed LDO is reduced to 97 mV and 0.142 μs respectively. -

References

[1] Lam Y H, Ki W H. A 0.9 V 0.35 μm adaptively biased CMOS LDO regulator with fast transient response. IEEE Int Solid-State Circuits Conf, 2008:442 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4523247[2] Ho M, Leung K N. Dynamic bias-current boosting technique for ultralow-power low-dropout regulator in biomedical applications. IEEE Trans Circuits Syst Ⅱ, Exp Briefs, 2011, 58(3):174 doi: 10.1109/TCSII.2011.2110330[3] Zhan C, Ki W H. Output-capacitor-free adaptively biased low-dropout regulator for system-on-chips. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2010, 57(5):1017 doi: 10.1109/TCSI.2010.2046204[4] Al-Shyoukh M, Lee H, Perez R. A transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation. IEEE J Solid-State Circuits, 2007, 42(8):1732 doi: 10.1109/JSSC.2007.900281[5] Leung K N, Ng Y S. A CMOS low-dropout regulator with a momentarily current-boosting voltage buffer. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2010, 57(9):2312 doi: 10.1109/TCSI.2010.2043171[6] Man T Y, Mok P K T, Chan M. A high slew-rate push-pull output amplifier for low-quiescent current low-dropout regulators with transient-response improvement. IEEE Trans Circuits Syst Ⅱ, Exp Briefs, 2007, 54(9):755 doi: 10.1109/TCSII.2007.900347[7] Or P Y, Leung K N. An output-capacitorless low-dropout regulator with direct voltage-spike detection. IEEE J Solid-State Circuits, 2010, 45(2):458 doi: 10.1109/JSSC.2009.2034805[8] Lee H, Mok P K T, Leung K N. Design of low-power analog drivers based on slew-rate enhancement circuits for CMOS low-dropout regulators. IEEE Trans Circuits Syst Ⅱ, Exp Briefs, 2005, 52(9):563 doi: 10.1109/TCSII.2005.850781[9] Guo J P, Leung K N. A 6-μW chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J Solid-State Circuits, 2010, 45(9):1896 doi: 10.1109/JSSC.2010.2053859[10] Rincon-Mora G A, Allen P E. A low-voltage, low quiescent current, low dropout regulator. IEEE J Solid-State Circuits, 1998, 33(1):36 doi: 10.1109/4.654935[11] Endoh T, Sunaga K, Sakuraba H, et al. An on-chip 96.5% current efficiency CMOS linear regulator using a fiexible control technique of output current. IEEE J Solid-State Circuits, 2001, 36(1):34 doi: 10.1109/4.896226[12] Onizuka K, Kawaguchi H, Takamiya M, et al. VDD-hopping accelerators for on-chip power supply circuit to achieve nanosecond-order transient time. IEEE J Solid-State Circuits, 2006, 44(11):2382 http://ieeexplore.ieee.org/document/1717661/[13] Milliken R J, Silva-Martínez J, Sánchez-Sinencio E. Full on-chip CMOS low-dropout voltage regulator. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2007, 54(9):1879 doi: 10.1109/TCSI.2007.902615[14] Chava C K, Silva-Martínez J. A frequency compensation scheme for LDO voltage regulators. IEEE Trans Circuits Syst Ⅰ, Reg Papers, 2004, 51(6):1041 doi: 10.1109/TCSI.2004.829239[15] Ho E N Y, Mok P K T. A capacitor-less CMOS active feedback low-dropout regulator with slew-rate enhancement for portable on-chip application. IEEE Trans Circuits Syst Ⅱ, Exp Briefs, 2010, 57(2):80 doi: 10.1109/TCSII.2009.2038630[16] Lin H C, Wu H H, Chang T Y. An active-frequency compensation scheme for CMOS low-dropout regulators with transient-response improvement. IEEE Trans Circuits Syst Ⅱ, Exp Briefs, 2008, 55(9):853 doi: 10.1109/TCSII.2008.924366[17] Leung K N, Mok P K T. A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation. IEEE J Solid-State Circuits, 2003, 38(10):1691 doi: 10.1109/JSSC.2003.817256[18] Oh W, Bakkaloglu B. A CMOS low-dropout regulator with current-mode feedback buffer amplifier. IEEE Trans Circuits Syst Ⅱ, Exp Briefs, 2007, 54(10):922 doi: 10.1109/TCSII.2007.901621[19] Chen W, Ki W H, Mok P K T. Dual-loop feedback for fast low dropout regulators. IEEE 32nd Power Electron Specialists Conf, 2001, 3:1265 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=954294[20] Guo J, Leung K N. A 6-μW chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J Solid-State Circuits, 2010, 45(9):1896 doi: 10.1109/JSSC.2010.2053859[21] Ho M, Leung K N, Mak K L. A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages. IEEE J Solid-State Circuits, 2010, 45(11):2466 http://ieeexplore.ieee.org/document/5593893/[22] Chen C, Wu J H, Wang Z X. 150 mA LDO with self-adjusting frequency compensation scheme. Electron Lett, 2011, 47(13):767 doi: 10.1049/el.2011.0771[23] Chen C L, Huang W J, Liu S I. CMOS low dropout regulator with dynamic zero compensation. Electron Lett, 2007, 43(14):1063 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4271347[24] Rincon-Mora G A. Analog IC design with low-dropout regulators. New York:The McGraw-Hill Companies, 2009 -

Proportional views

DownLoad:

DownLoad: