| Citation: |

Honglin Xu, Qiang Fu, Hongna Liu, Liang Yin, Pengfei Wang, Xiaowei Liu. A 16-bit sigma-delta modulator applied in micro-machined inertial sensors[J]. Journal of Semiconductors, 2014, 35(4): 045007. doi: 10.1088/1674-4926/35/4/045007

****

H L Xu, Q Fu, H N Liu, L Yin, P F Wang, X W Liu. A 16-bit sigma-delta modulator applied in micro-machined inertial sensors[J]. J. Semicond., 2014, 35(4): 045007. doi: 10.1088/1674-4926/35/4/045007.

|

A 16-bit sigma-delta modulator applied in micro-machined inertial sensors

DOI: 10.1088/1674-4926/35/4/045007

More Information

-

Abstract

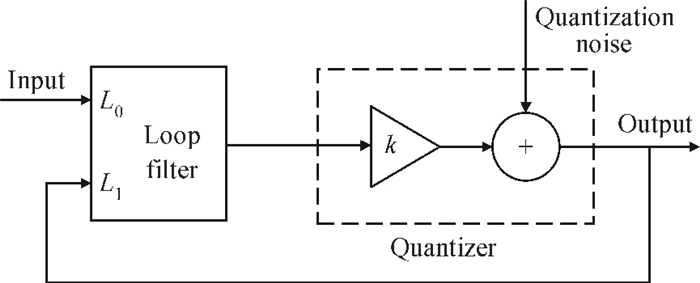

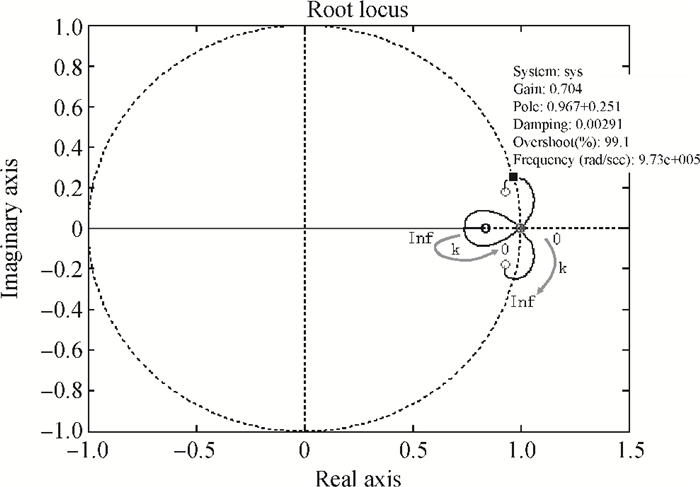

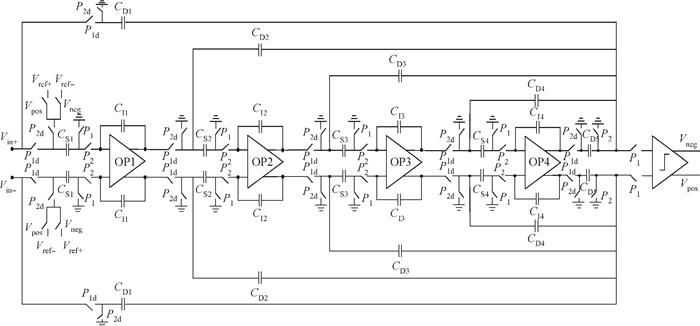

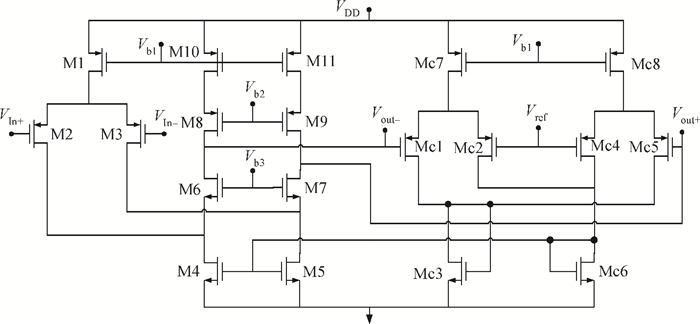

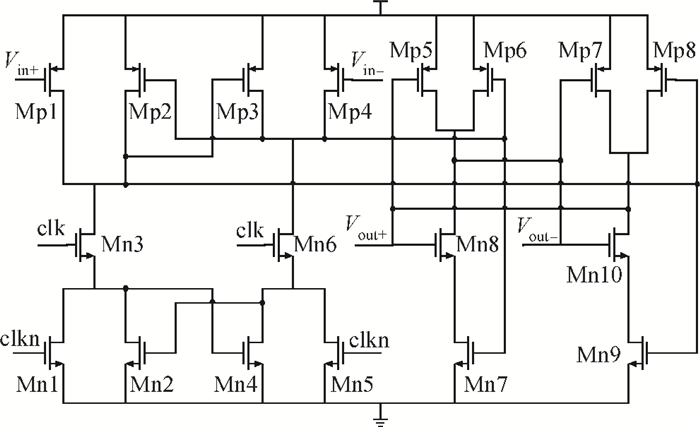

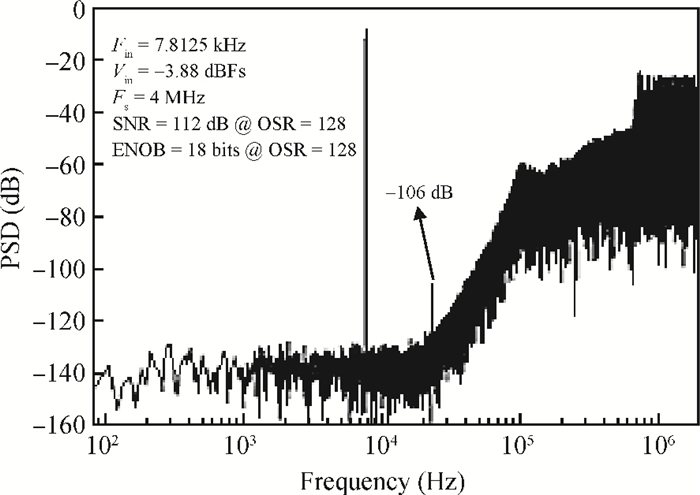

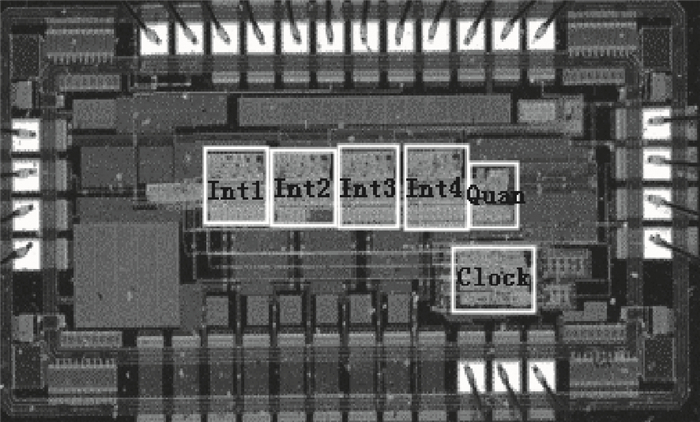

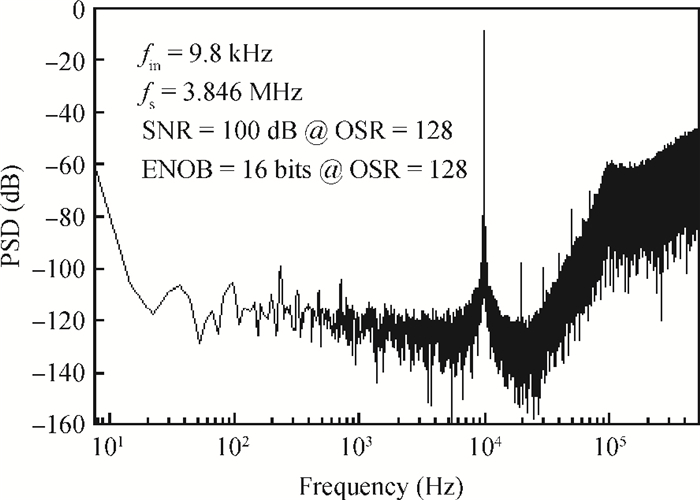

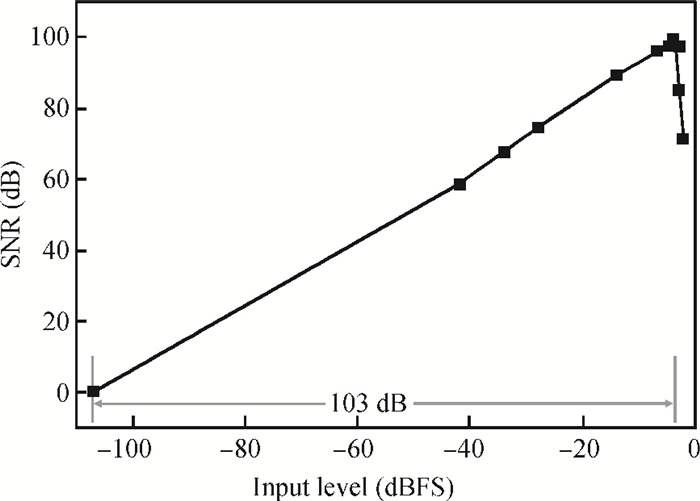

A fourth-order low-distortion low-pass sigma-delta (Σ Δ) modulator is presented for micro-machined inertial sensors. The proposed single-loop single-bit feedback modulator is optimized with a feed-forward path to decrease the nonlinearities and power consumption. The IC is implemented in a standard 0.6 μm CMOS technology and operates at a sampling frequency of 3.846 MHz. The chip area is 2.12 mm2 with 23 pads. The experimental results indicate a signal-to-noise ratio (SNR) of 100 dB and dynamic range (DR) of 103 dB at an oversampling rate (OSR) of 128 with the input signal amplitude of -3.88 dBFS at 9.8 kHz; the power consumption is 15 mW at a 5 V supply. -

References

[1] Cao Ying, Ren Tenglong, Hong Zhilian. A 16 bit 96 kHz chopper-stabilized sigma-delta ADC. Chinese Journal of Semiconductors, 2007, 28(8):1204 http://en.cnki.com.cn/Article_en/CJFDTOTAL-BDTX200708011.htm[2] Külah H, Chae J. Noise analysis and characterization of a sigma-delta capacitive microaccelerometer. IEEE J Solid-State Circuits, 2006, 41(2):352 doi: 10.1109/JSSC.2005.863148[3] Rusu A, Tenhunen H. DAC nonlinearity effects in a wide-band sigma-delta modulator architecture. 15th Annual IEEE International ASIC/SOC Conference, 2002:75 https://www.researchgate.net/publication/3995109_DAC_nonlinearity_effects_in_a_wide-band_sigma-delta_modulator_architecture?_sg=TuX8MXvE9rKVpPzWxmjlR7Kzzr2QFRPgTm2LDg9yHQUS7lG83Lye0Ga3MPtcmdURXnsRYTD_nZ9O8DLdmM4DEg[4] Xu H, Zhou J, Yang J. A low-distortion fourth-order bandpass sigma-delta modulator using double-sampling technique. Key Eng Mater, 2013, 562-565:1058 doi: 10.4028/www.scientific.net/KEM.562-565[5] Hsu C, Yo T, Luo C. An ultra low power variable resolution sigma delta modulator for signals acquisition of biomedical instrument. IEICE Trans Electron, 2007, E90-C(9):1823 doi: 10.1093/ietele/e90-c.9.1823[6] Li Jinfeng, Tang Zhen'an. An A/D interface based on Σ Δ modulator for thermal vacuum sensor ASICs. Journal of Semiconductors, 2010, 31(7):115 http://www.jos.ac.cn/bdtxbcn/ch/reader/view_abstract.aspx?file_no=09121402&flag=1[7] Ge Binjie, Wang Xin'an, Zhang Xing. Top-down design for MASH21 sigma-delta modulator. Acta Scientiarum Naturalium Universitatis Pekinensis, 2011, 47(4):593 https://www.researchgate.net/publication/293285879_Top-down_design_for_MASH21_sigma-delta_modulator[8] Silveira F, Flandre D, Jespers P G A. A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA. IEEE J Solid-State Circuits, 1996, 31(9):1314 doi: 10.1109/4.535416[9] Dammak H D, Bensalem S, Zouari S, et al. Design of folded cascode OTA in different regions of operation through gm/ID methodology. Proceeding of World Academy of Science, Engineering and Technology, 2008 https://www.researchgate.net/publication/228945289_Design_of_Folded_Cascode_OTA_in_Different_Regions_of_Operation_Through_gmID_Methodology?showAllCitations=1[10] Cubas H A, Navarro J. Design of an OTA-Miller for a 96 dB SNR SC multi-bit sigma-delta modulator based on gm/ID methodology. IEEE Fourth Latin American Symposium on Circuits and Systems, 2013 http://ieeexplore.ieee.org/document/6519051/[11] Amini B V, Ayazi F. A 2.5-V 14-bit Σ Δ CMOS SOI capacitive accelerometer. IEEE J Solid-State Circuits, 2004, 39(12):2467 doi: 10.1109/JSSC.2004.837025[12] Wu J. Sensing and control electronics for low-mass low-capacitance MEMS accelerometers. Doctoral Dissertation, Carnegie Mellon University, 2002:65[13] Yuan Yudan, Li Li, Chang Hong. A 100-MHz bandpass sigma-delta modulator with a 75-dB dynamic range for IF receivers. Journal of Semiconductors, 2011, 32(2):73 http://www.jos.ac.cn/bdtxbcn/ch/reader/view_abstract.aspx?file_no=10080402&flag=1[14] Chen Jianqiu, Ren Junyan, Xu Jun. An 80 dB dynamic range Σ -Δ modulator for a GSM system. Chinese Journal of Semiconductors, 2007, 28(2):294[15] Yang Pei, Yin Xiumei, Yang Huazhong. An 80 dB dynamic range Σ Δ modulator for low-IF GSM receivers. Journal of Semiconductors, 2008, 29(2):256 http://www.jos.ac.cn/bdtxbcn/ch/reader/view_abstract.aspx?file_no=07070802&flag=1[16] Nam K Y, Lee S M, Su D K, et al. A low-voltage low-power sigma-delta modulator for broadband analog-to-digital conversion. IEEE J Solid-State Circuits, 2005, 40(9):1855 doi: 10.1109/JSSC.2005.852161[17] Bos L, Vandersteen G, Rombouts P, et al. Multirate cascaded discrete-time low-pass Δ Σ modulator for GSM/Bluetooth/UMTS. IEEE J Solid-State Circuits, 2010, 45(6):1198 doi: 10.1109/JSSC.2010.2046240[18] Chen Lei, Zhao Yuanfu, Gao Deyuan, et al. A 16 bit stereo audio sigma-delta A/D converter. Chinese Journal of Semiconductors, 2006, 27(2):1183[19] Keskin M, Moon U K, Temes G C. A 1-V 10-MHz clock-rate 13-bit CMOS Δ Σ modulator using unity-gain-reset opamps. IEEE J Solid-State Circuits, 2002, 37(7):817 doi: 10.1109/JSSC.2002.1015678[20] Michel F, Steyaert M S J. A 250 mV 7.5μW 61 dB SNDR SC Δ Σ modulator using near-threshold-voltage-biased inverter amplifier in 130 nm CMOS. IEEE J Solid-State Circuits, 2012, 47(3):709 doi: 10.1109/JSSC.2011.2179732 -

Proportional views

DownLoad:

DownLoad: