| Citation: |

Lingjuan Lü, Ruping Liu, Min Lin, Zehua Sang, Shichang Zou, Genqing Yang. Performance comparison of radiation-hardened layout techniques[J]. Journal of Semiconductors, 2014, 35(6): 065006. doi: 10.1088/1674-4926/35/6/065006

****

L Lü, R P Liu, M Lin, Z H Sang, S C Zou, G Q Yang. Performance comparison of radiation-hardened layout techniques[J]. J. Semicond., 2014, 35(6): 065006. doi: 10.1088/1674-4926/35/6/065006.

|

Performance comparison of radiation-hardened layout techniques

DOI: 10.1088/1674-4926/35/6/065006

More Information

-

Abstract

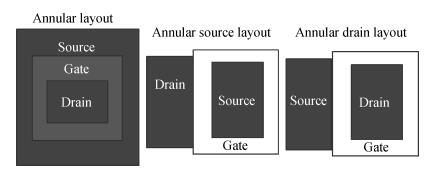

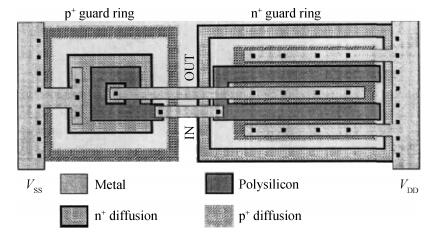

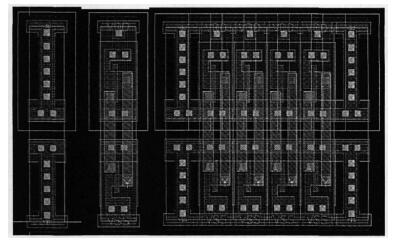

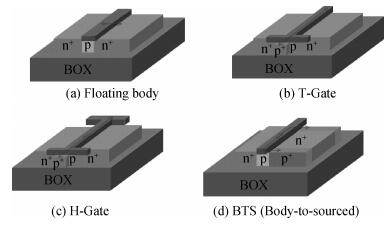

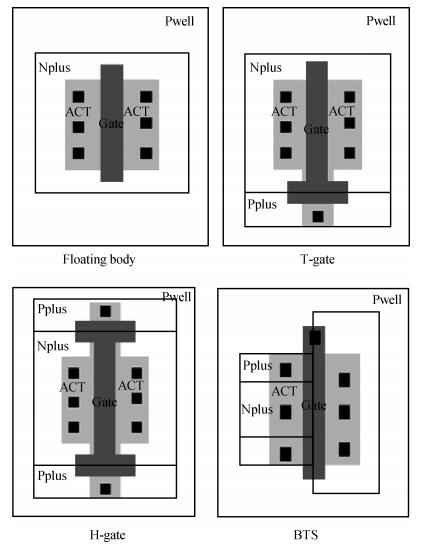

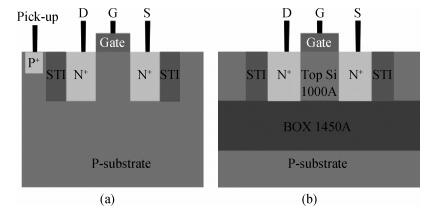

Total ionizing dose (TID) effect and single event effect (SEE) from space may cause serious effects on bulk silicon and silicon on insulator (SOI) devices, so designers must pay much attention to these bad effects to achieve better performance. This paper presents different radiation-hardened layout techniques to mitigate TID and SEE effect on bulk silicon and SOI device and their corresponding advantages and disadvantages are studied in detail. Under 0.13 μm bulk silicon and SOI process technology, performance comparisons of two different kinds of DFF circuit are made, of which one kind is only hardened in layout (protection ring for bulk silicon DFF, T-gate for SOI DFF), while the other kind is also hardened in schematic such as DICE structure. The result shows that static power and leakage of SOI DFF is lower than that of bulk silicon DFF, while SOI DFF with T-gate is a little slower than bulk silicon DFF with protection ring, which will provide useful guidance for radiation-hardened circuit and layout design. -

References

[1] Baumann R C. Single event effects in advanced CMOS technology. IEEE NSREC Short Course Text, 2005:1 http://www.mendeley.com/research/singleevent-effects-advanced-cmos-technology/[2] Dodd P E, Massengill L W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans Nucl Sci, 2003, 50:583 doi: 10.1109/TNS.2003.813129[3] Huang Ru, Zhang Guoyan. SOI CMOS technology and application. Beijing:Science Press, 2005[4] Champion C L, La Rue G S. Accurate SPICE models for CMOS analog radiation-hardness-by-design. IEEE Trans Nucl Sci, 2005, 52:2542 doi: 10.1109/TNS.2005.860717[5] Lacoe R C, Osborn J V, Koga R, et al. Application of hardness-by-design methodology to radiation-tolerant ASIC technologies. IEEE Trans Nucl Sci, 2000, 47:2334 doi: 10.1109/23.903774[6] Anelli G, Campbell M, Delmastro M, et al. Radiation tolerant VLSI circuits in standard deep submicron CMOS technologies for the LHC experiments:practical design aspects. IEEE Trans Nucl Sci, 1999, 46:1690 doi: 10.1109/23.819140[7] Hargrove M J, Voldman S, Gauthier R, et al. Latchup in CMOS technology. Proc IEEE 36th International Annual Reliability Physics Symposium, Reno, NV, USA, 1998:269 doi: 10.1007/978-1-4757-1887-4[8] Lacoe R C, Osborn J V, Koga R, et al. Application of hardness-by-design methodology to radiant-tolerant ASIC technologies. IEEE Trans Nucl Sci, 2000, 47(6):2334 doi: 10.1109/23.903774[9] Lacoe R C. Performance impact of radiation-hardness-by-design. Hardness-By-Design-Workshop, Albuquerque, NM, 2001[10] Nowlin N, Bailey J, Turfler B, et al. A total-dose hardening-by-design for high-speed mixed-signal CMOS integrate circuits. Intl Jour High Speed Elec Sys, 2004, 14:367 doi: 10.1142/S0129156404002417[11] Narasimham B, Bhuva B L, Schrimpf R D, et al. Effects of guard bands and well contacts in mitigating long SETs in advanced CMOS processes. IEEE Trans Nucl Sci, 2008, 55(3):1708 doi: 10.1109/TNS.2008.920260[12] Narasimham B, Gambles J W, Shuler R L, et al. Quantifying the effect of guard rings and guard drains in mitigating charge collection and charge spread. IEEE Trans Nucl Sci, 2008, 55(6):3456 doi: 10.1109/TNS.2008.2007119[13] Luo J, Chen J, Wu Q, et al. A tunnel diode body contact structure for high-performance SOI MOSFETs. IEEE Trans Electron Devices, 2012, 59:101 doi: 10.1109/TED.2011.2173201 -

Proportional views

DownLoad:

DownLoad: