| Citation: |

Di Zhao, Qian Luo, Xiangzhan Wang, Qi Yu, Wei Cui, Kaizhou Tan. Performance enhancement of c-CESL-strained 95-nm-gate NMOSFET usingtrench-based structure[J]. Journal of Semiconductors, 2015, 36(1): 014010. doi: 10.1088/1674-4926/36/1/014010

****

D Zhao, Q Luo, X Z Wang, Q Yu, W Cui, K Z Tan. Performance enhancement of c-CESL-strained 95-nm-gate NMOSFET usingtrench-based structure[J]. J. Semicond., 2015, 36(1): 014010. doi: 10.1088/1674-4926/36/1/014010.

|

Performance enhancement of c-CESL-strained 95-nm-gate NMOSFET usingtrench-based structure

DOI: 10.1088/1674-4926/36/1/014010

More Information

-

Abstract

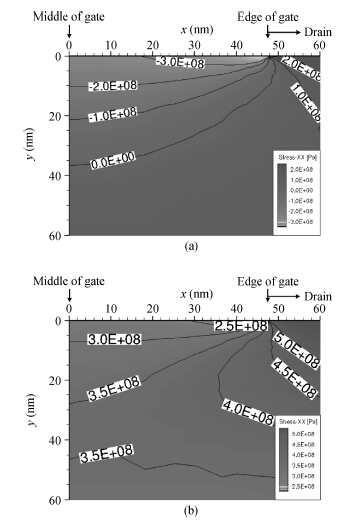

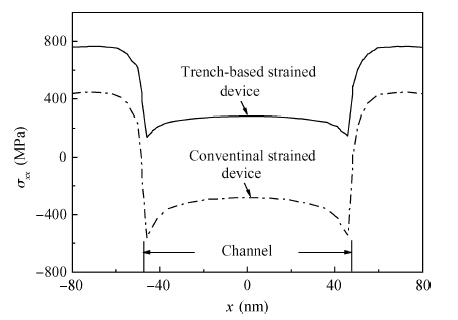

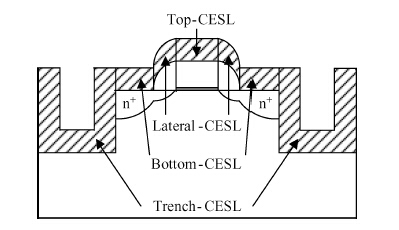

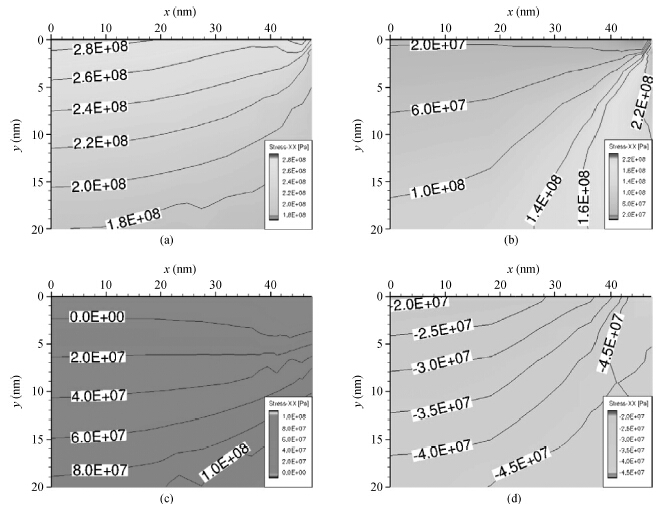

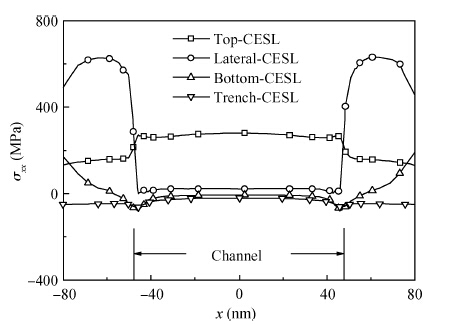

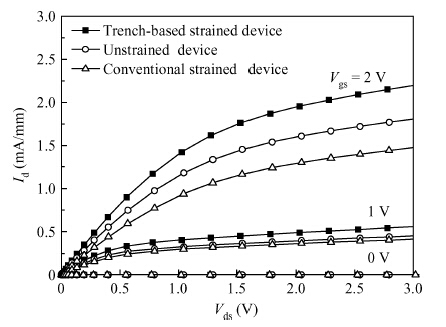

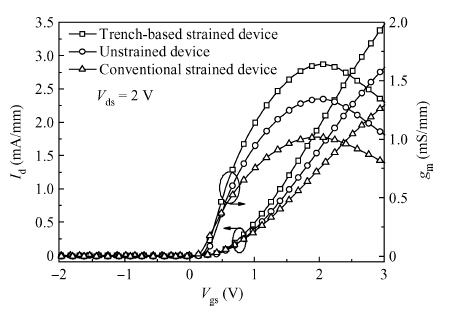

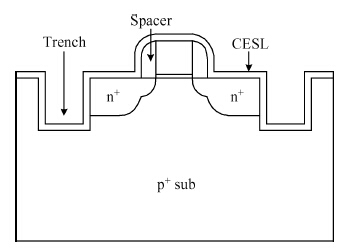

A stress modulation technology using a trench-based structure for strained NMOSFET is reported in this paper. With this technology, NMOSFET can be improved by a compressive contact etch stop layer (CESL), whereas the traditional CESL-strained NMOSFET requires a tensile one. To confirm this idea, a 95-nm-gate device with a-2.5 GPa strained CESL is simulated to investigate the effects of the trench-based structure on channel stress. It is demonstrated that the average longitudinal channel stress is transformed from-333 into 256 MPa, which leads to a significant improvement of the device's I-V performance. For strained CMOS, this approach provides a potential alternative besides dual stress liner technology.-

Keywords:

- CESL,

- trench,

- strained NMOSFET,

- SiN

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] -

Proportional views

DownLoad:

DownLoad: