| Citation: |

Weidong Yang, Jiandong Zang, Tiehu Li, Pu Luo, Jie Pu, Ruitao Zhang, Chao Chen. A 16 b 2 GHz digital-to-analog converter in 0.18 μm CMOS with digital calibration technology[J]. Journal of Semiconductors, 2015, 36(10): 105002. doi: 10.1088/1674-4926/36/10/105002

****

W D Yang, Jiandong Zang and O N Zang, T H Li, P Luo, J Pu, R T Zhang, C Chen. A 16 b 2 GHz digital-to-analog converter in 0.18 μm CMOS with digital calibration technology[J]. J. Semicond., 2015, 36(10): 105002. doi: 10.1088/1674-4926/36/10/105002.

|

A 16 b 2 GHz digital-to-analog converter in 0.18 μm CMOS with digital calibration technology

DOI: 10.1088/1674-4926/36/10/105002

-

Abstract

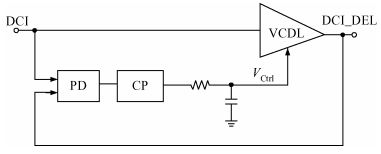

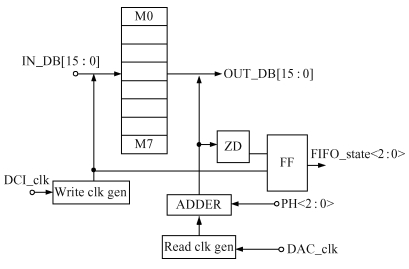

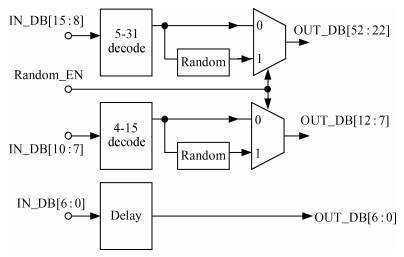

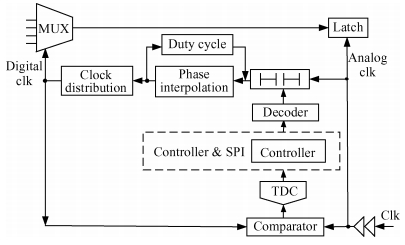

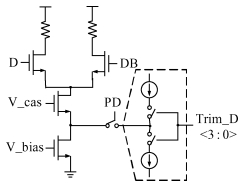

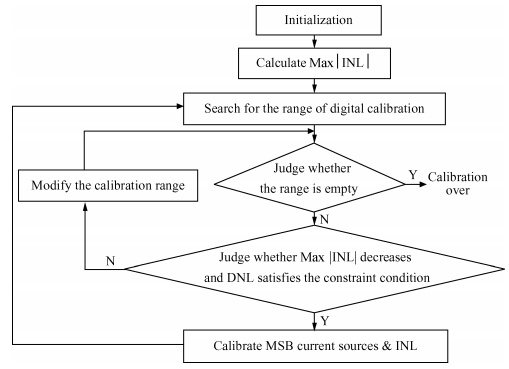

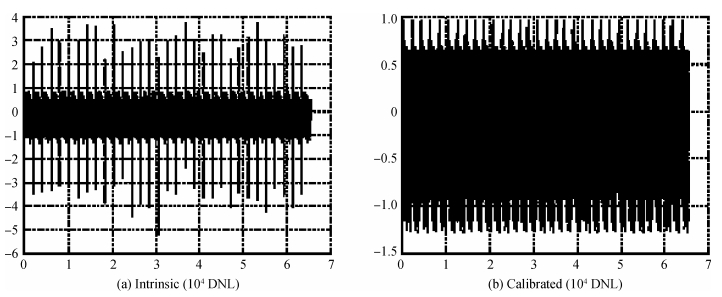

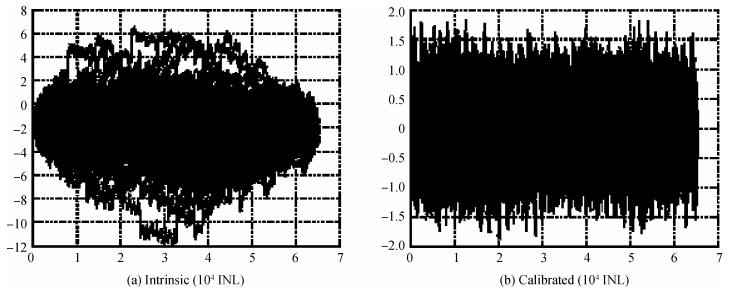

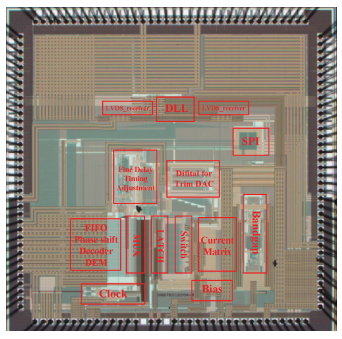

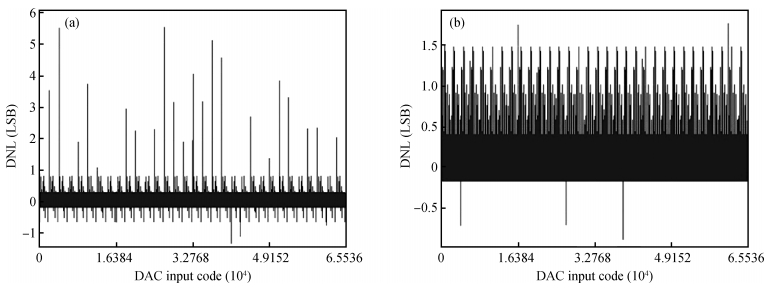

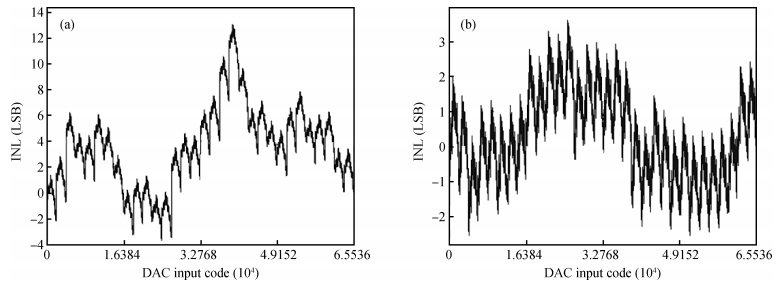

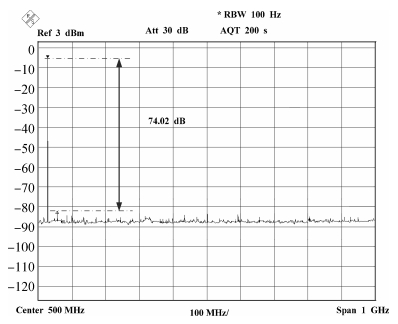

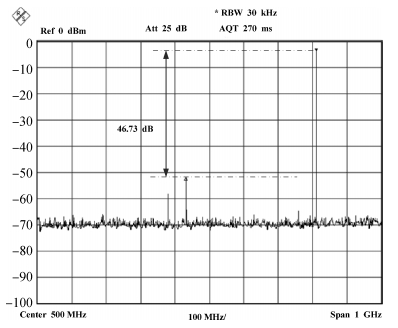

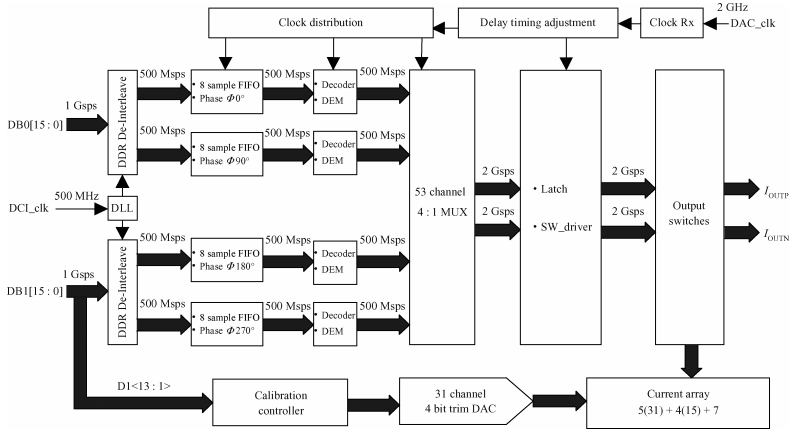

This paper presents a 16-bit 2 GSPS digital-to-analog converter (DAC) in 0.18μm CMOS technology.This DAC is implemented using time division multiplex access system architecture in the digital domain.The input data is received with a two-channel LVDS interface.The DLL technology is introduced to meet the timing requirements between phases of the LVDS data and the data sampling clock.A FIFO is designed to absorb the phase difference between the data clock and DAC system clock.A delay controller is integrated to adjust the phase relationship between the high speed digital clock and analog clock, obtaining a sampling rate of 2 GSPS.The current source mismatch at higher bits is calibrated in the digital domain.Test results show that the DAC achieves 74.02 dBC SFDR at analog output of 36 MHz, and DNL less than ±2.1 LSB INL less than ±4.3 LSB after the chip is calibrated. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] -

Proportional views

DownLoad:

DownLoad: