| Citation: |

Suge Yue, Xiaolin Zhang, Xinyuan Zhao. Single event transient pulse width measurement of 65-nm bulk CMOS circuits[J]. Journal of Semiconductors, 2015, 36(11): 115006. doi: 10.1088/1674-4926/36/11/115006

****

S G Yue, X L Zhang, X Y Zhao. Single event transient pulse width measurement of 65-nm bulk CMOS circuits[J]. J. Semicond., 2015, 36(11): 115006. doi: 10.1088/1674-4926/36/11/115006.

|

Single event transient pulse width measurement of 65-nm bulk CMOS circuits

DOI: 10.1088/1674-4926/36/11/115006

More Information

-

Abstract

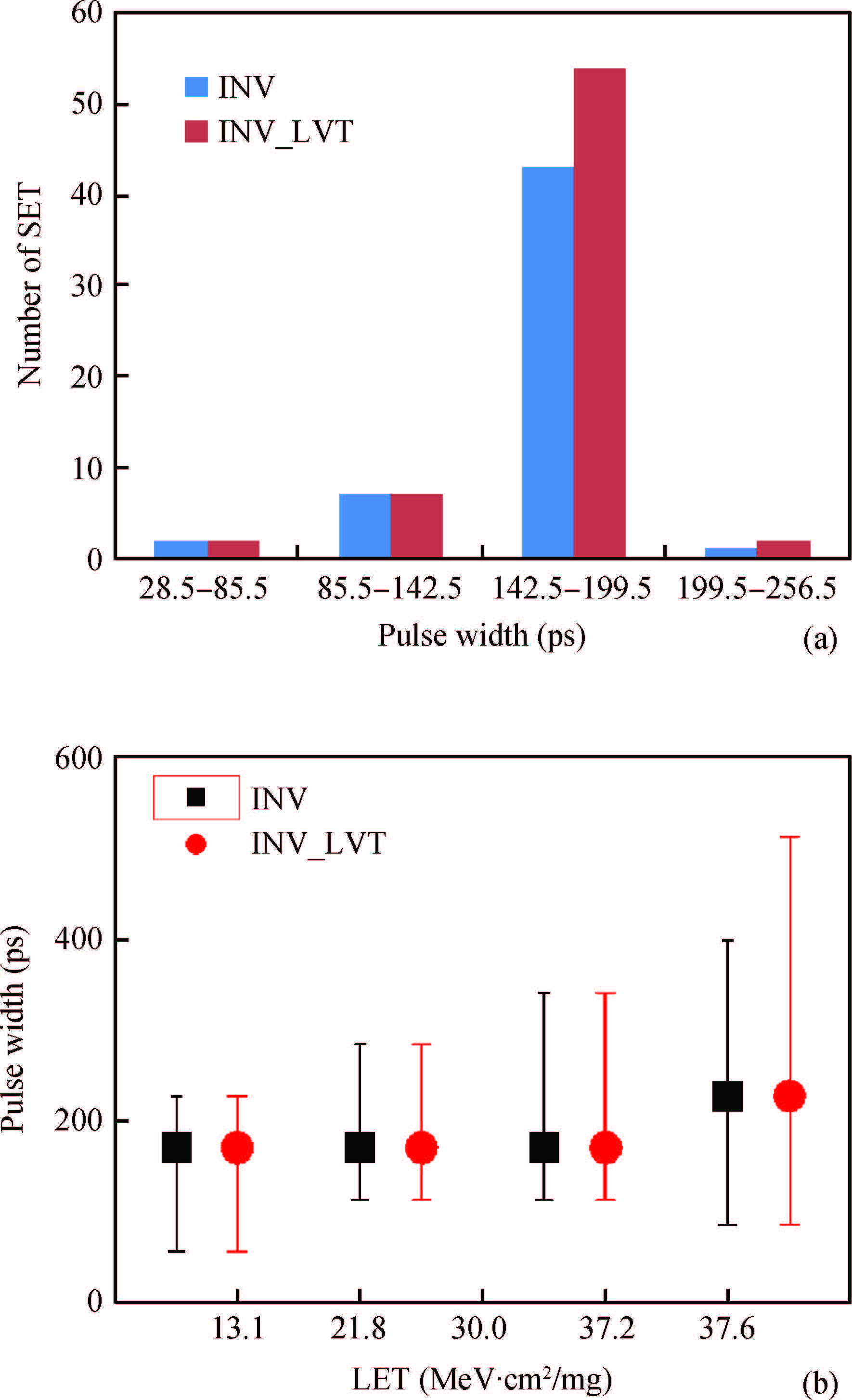

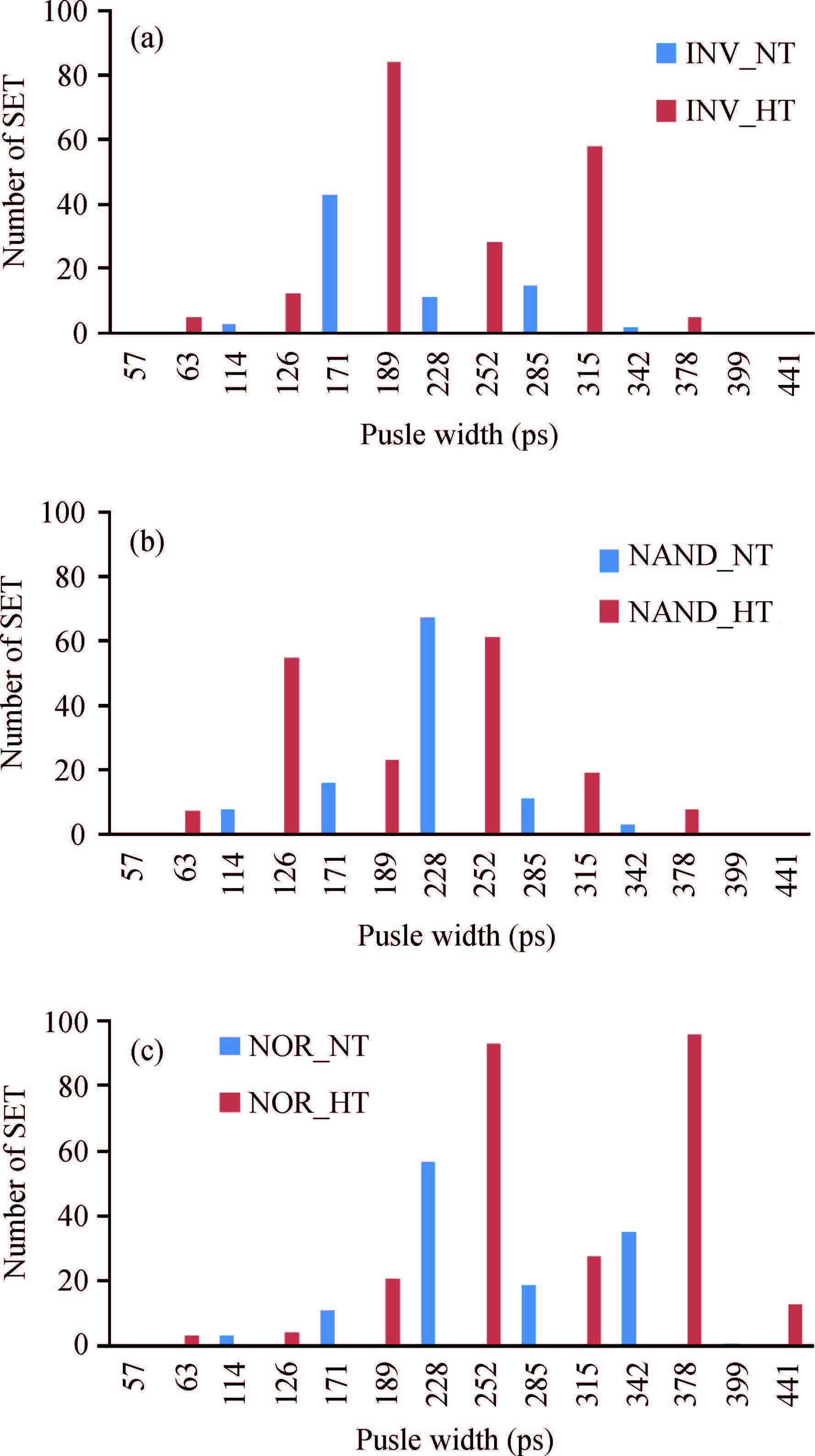

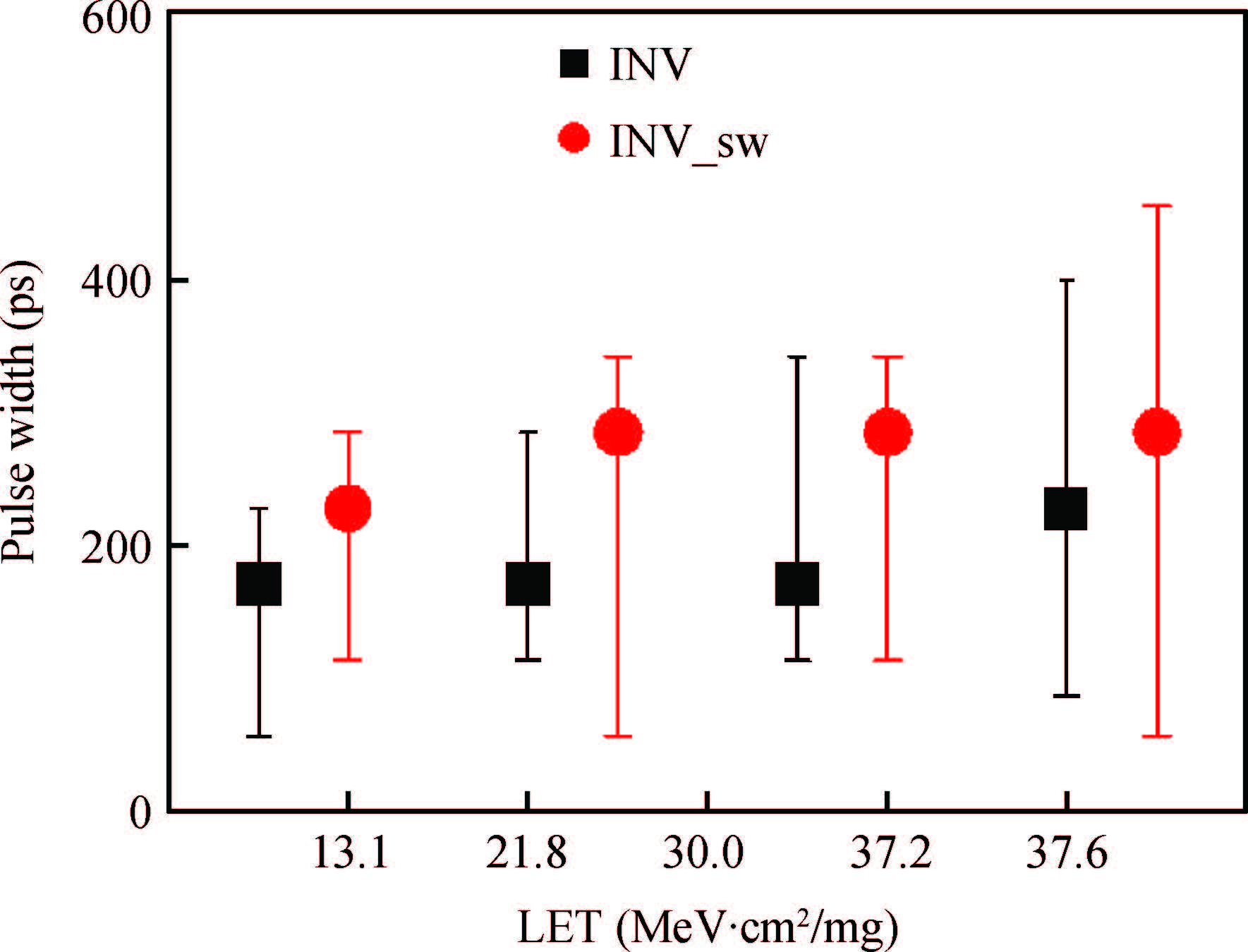

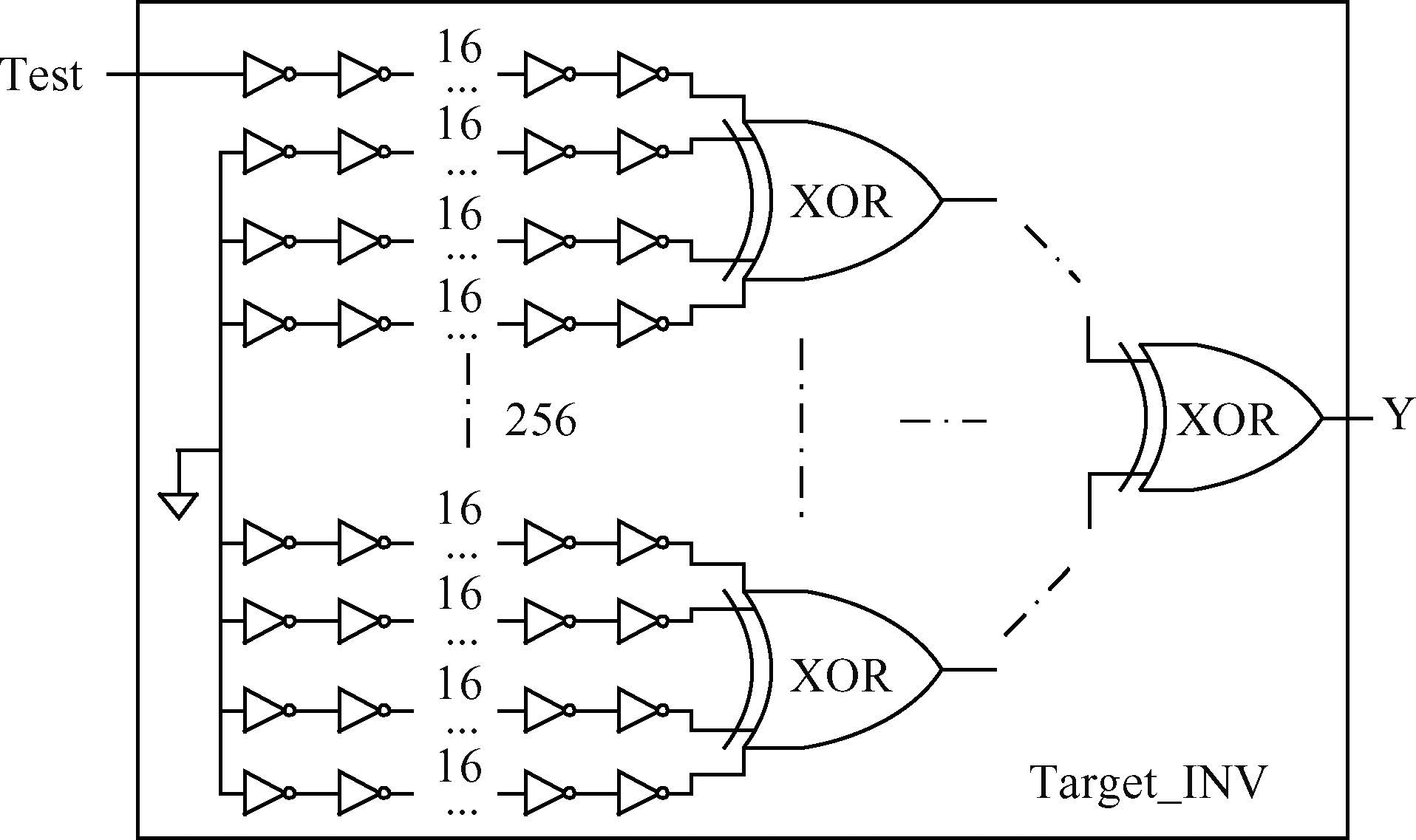

Heavy ion results of a 65-nm CMOS SET pulse width testchip are given. The influences of device threshold voltage, temperature and well separation on pulse width are discussed. Experimental data implied that the low device threshold, high temperature and well speraration would contribute to wider SET. The multi-peak phenomenon in the distribution of SET pulse width was first observed and its dependence on various factors is also discussed.-

Keywords:

- SET,

- pulsewidth,

- 65 nm

-

References

[1] [2] [3] [4] [5] [6] [7] [8] -

Proportional views

DownLoad:

DownLoad: