| Citation: |

Lin Liu, Suge Yue, Shijin Lu. A four-interleaving HBD SRAM cell based on dual DICE for multiple node collection mitigation[J]. Journal of Semiconductors, 2015, 36(11): 115007. doi: 10.1088/1674-4926/36/11/115007

****

L Liu, S G Yue, S J Lu. A four-interleaving HBD SRAM cell based on dual DICE for multiple node collection mitigation[J]. J. Semicond., 2015, 36(11): 115007. doi: 10.1088/1674-4926/36/11/115007.

|

A four-interleaving HBD SRAM cell based on dual DICE for multiple node collection mitigation

DOI: 10.1088/1674-4926/36/11/115007

More Information

-

Abstract

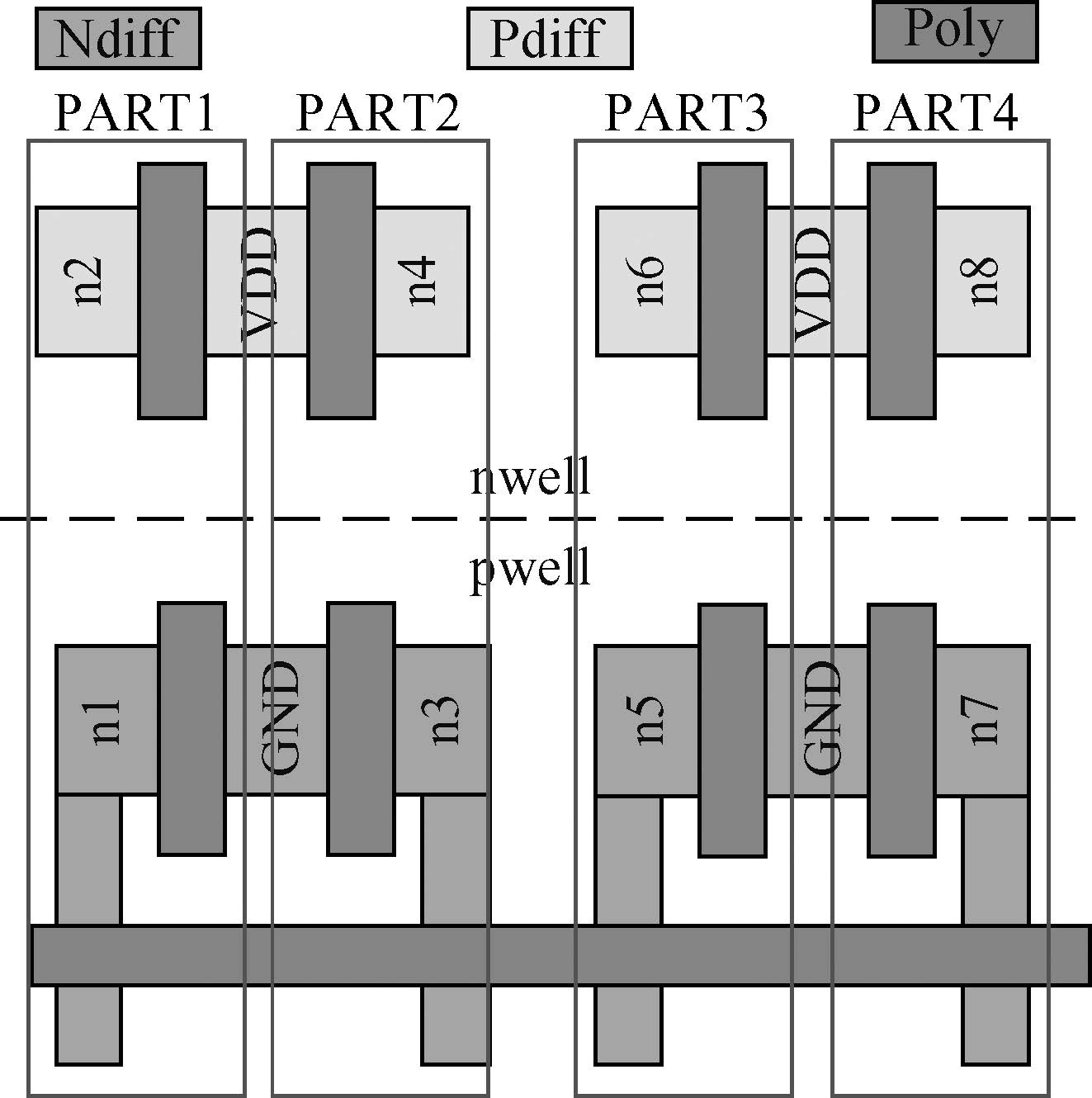

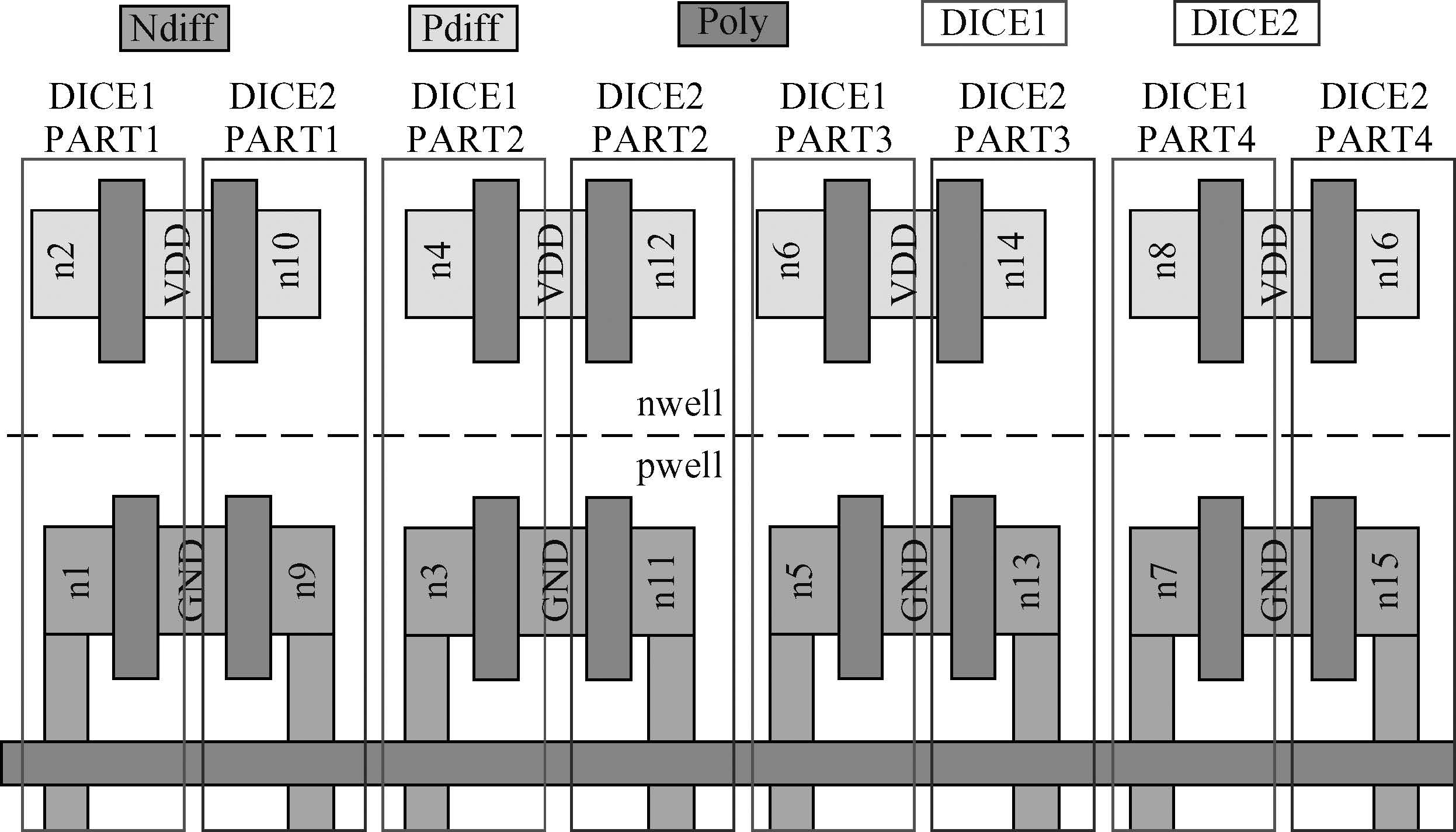

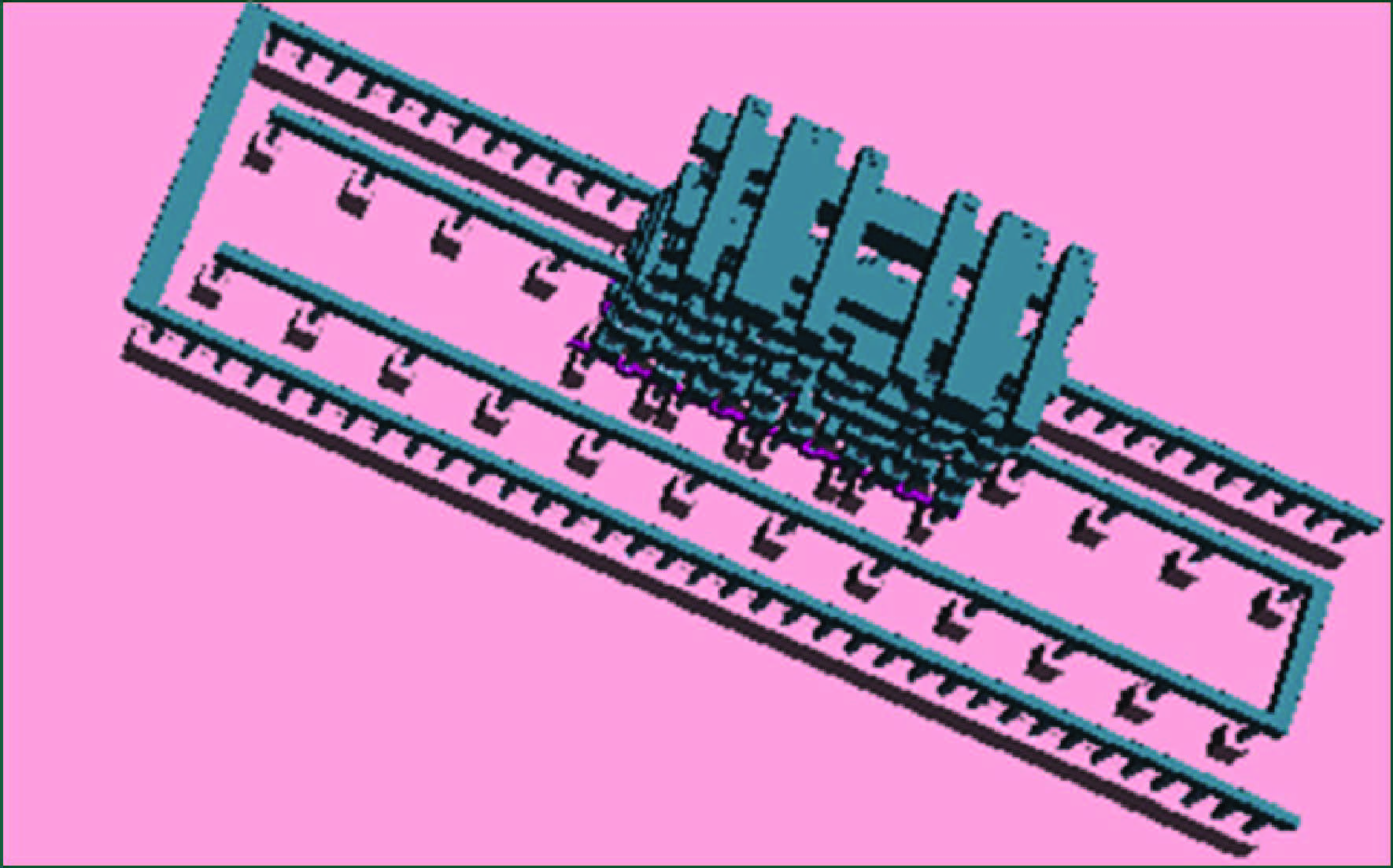

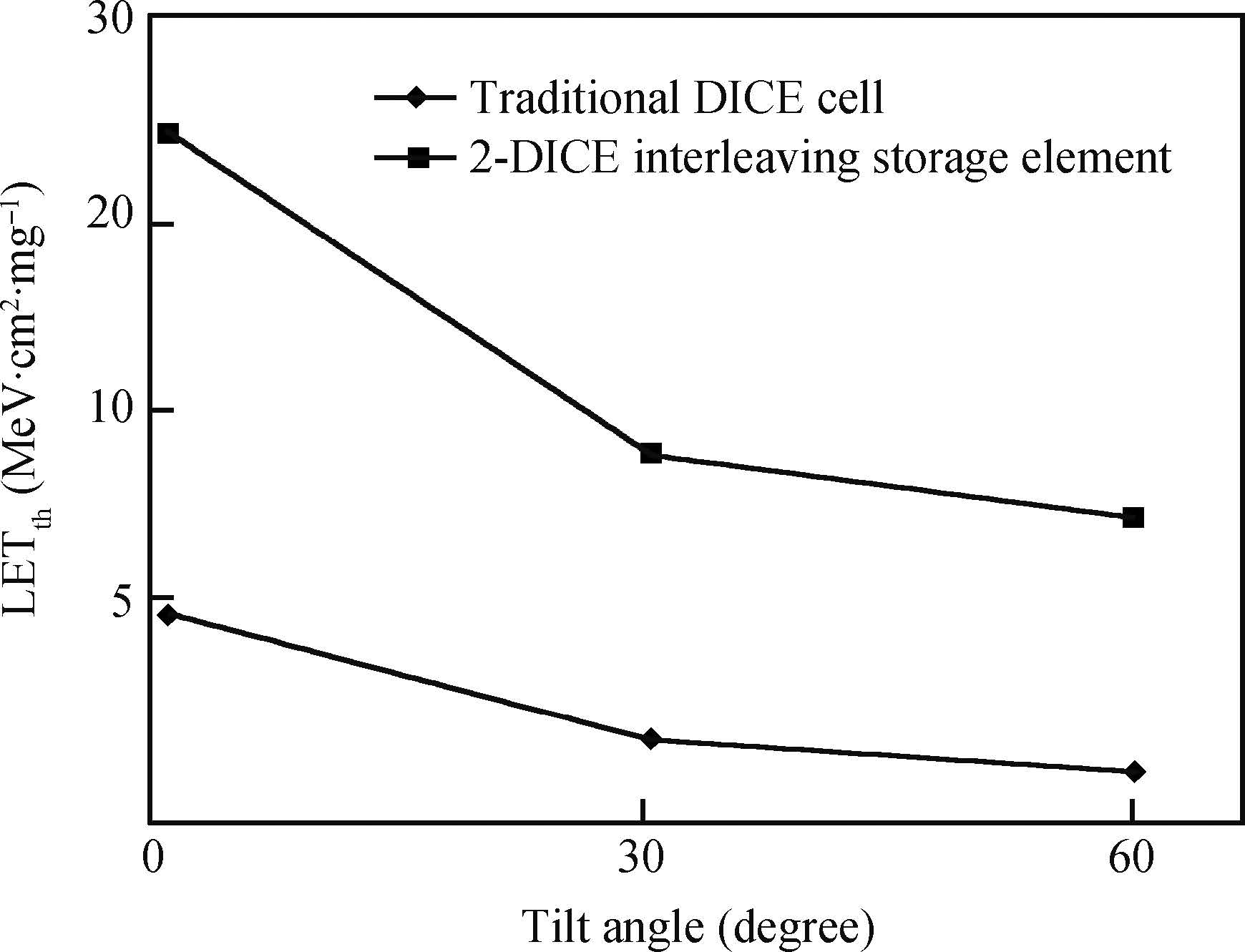

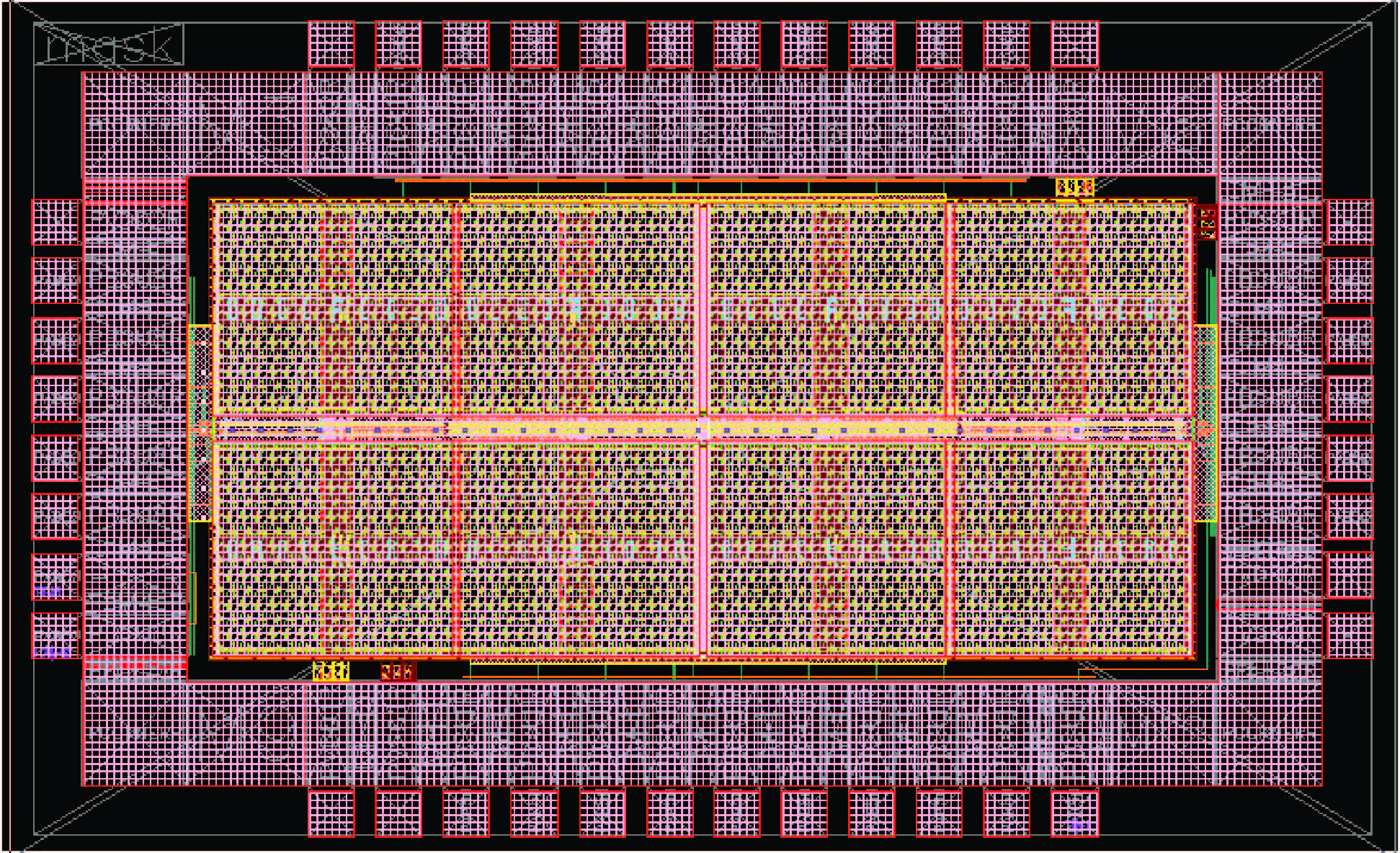

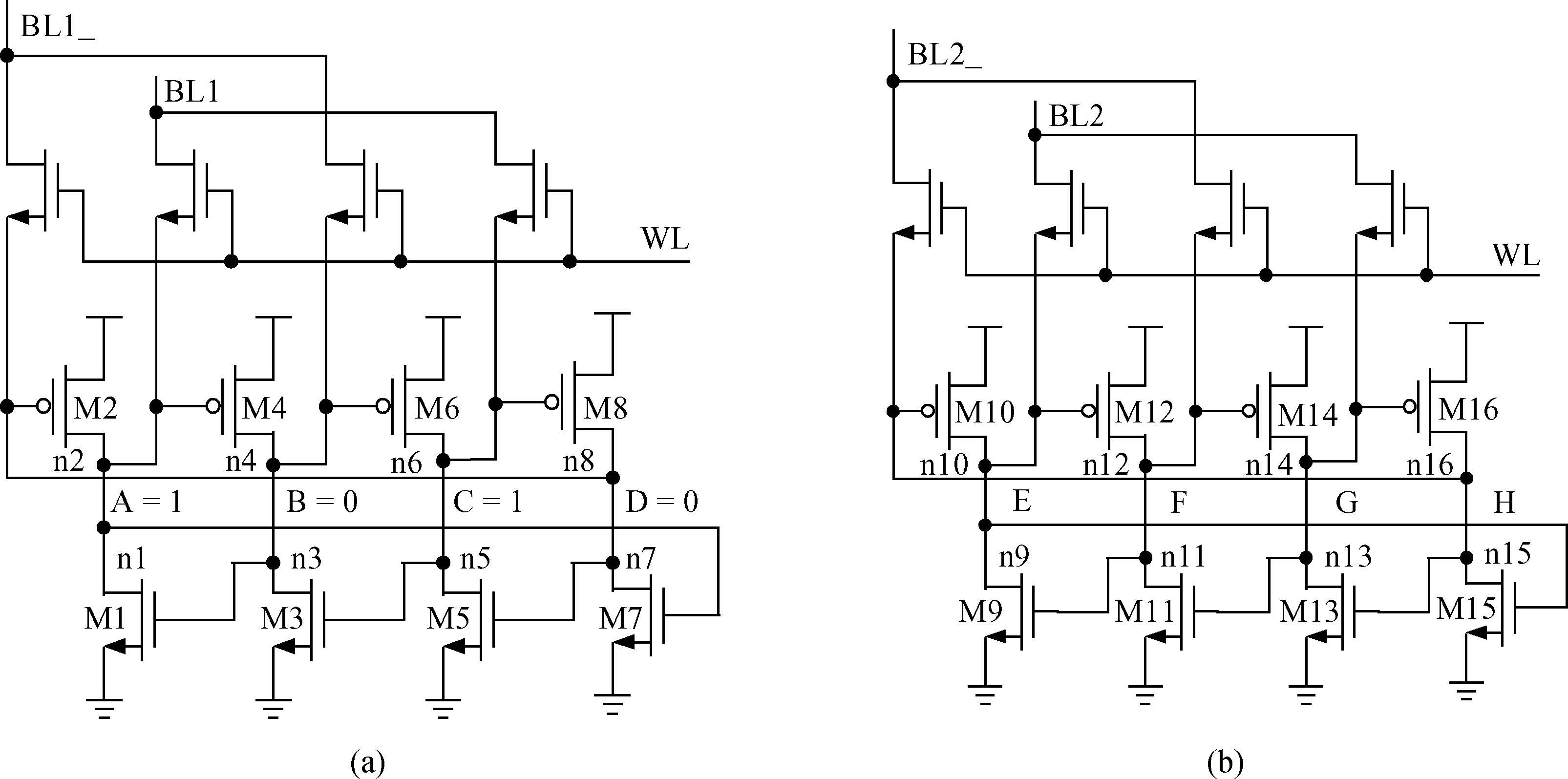

A 4-interleaving cell of 2-dual interlocked cells (DICE) is proposed, which reduces single event induced multiple node collection between the sensitive nodes of sensitive pairs in a DICE storage cell in 65 nm technology. The technique involves the 4-interleaving of dual DICE cells at a layout level to meet the required spacing between sensitive nodes in an area-efficient manner. Radiation experiments using a 65 nm CMOS test chip demonstrate that the LETth of our 4-interleaving cell of dual DICE encounters are almost 4× larger and the SEU cross section per bit for our proposed dual DICE design is almost two orders of magnitude less compared to the reference traditional DICE cell. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] -

Proportional views

DownLoad:

DownLoad: