| Citation: |

Ya Wang, Chunying Xue, Fule Li, Chun Zhang, Zhihua Wang. A low power 11-bit 100 MS/s SAR ADC IP[J]. Journal of Semiconductors, 2015, 36(2): 025003. doi: 10.1088/1674-4926/36/2/025003

****

Y Wang, C Y Xue, F L Li, C Zhang, Z H Wang. A low power 11-bit 100 MS/s SAR ADC IP[J]. J. Semicond., 2015, 36(2): 025003. doi: 10.1088/1674-4926/36/2/025003.

|

-

Abstract

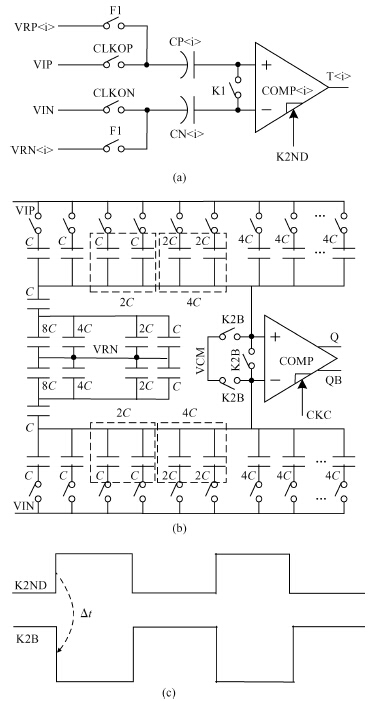

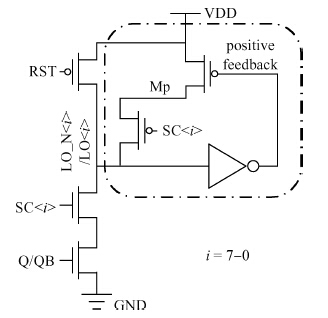

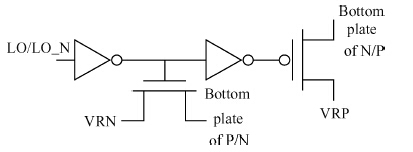

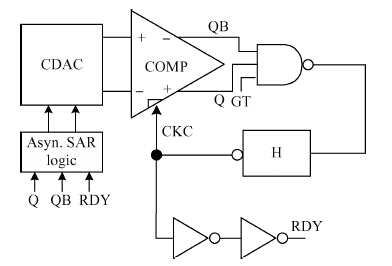

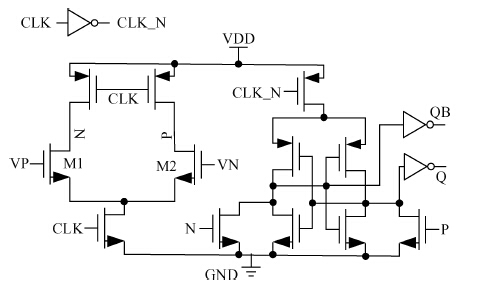

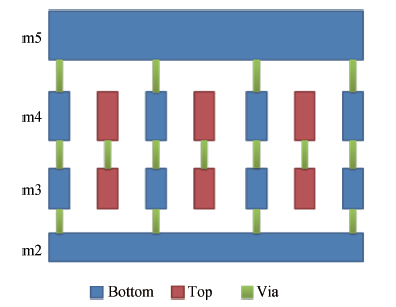

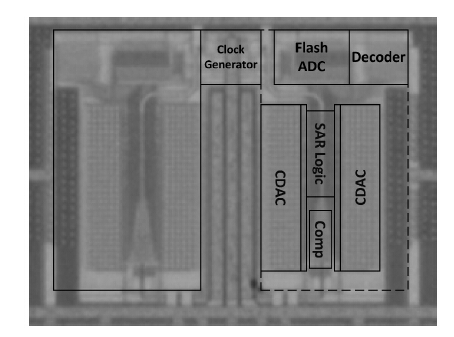

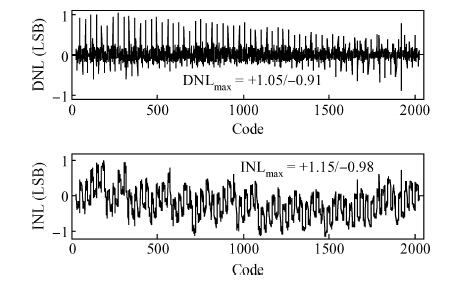

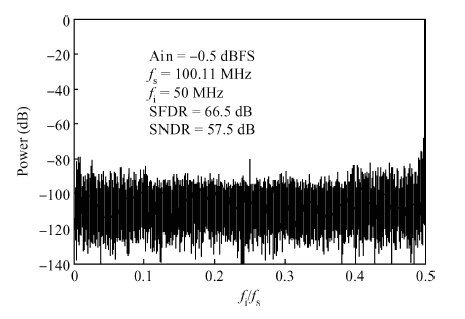

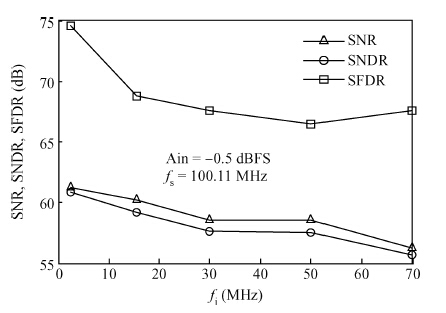

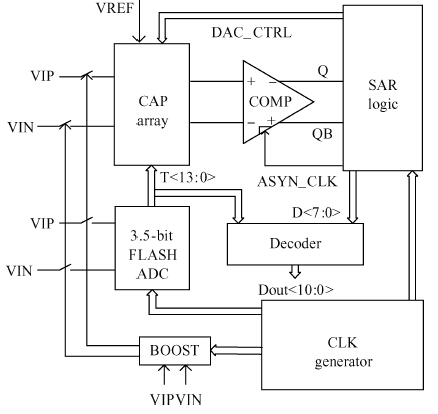

This paper presents a dual-channel 11-bit 100 MS/s hybrid SAR ADC IP. Each channel adopts flash-SAR architecture for high speed, low power and high linearity. Dynamic comparators in the coarse flash ADC and the fine SAR ADC further contribute to the reduction of power consumption. A gate-controlled ring oscillator generates a multi-phase clock for SAR logic, thereby allowing it to asynchronously trigger the comparator in the fine SAR ADC in high speed. MOM capacitors with a fully shielded structure provide enough matching accuracy without the need for calibration. This design was fabricated in SMIC 55 nm low leakage CMOS technology and the active area of dual-channel (I-Q) ADC is 0.35 mm2, while the core area is 0.046 mm2. It consumes 2.92 mA at a 1.2 V supply, for dual-channel too. The effective number of bits (ENOB) is 9.90 bits at 2.4 MHz input frequency, and 9.34 bits at 50 MHz, leading to a FOM of 18.3 fJ/conversion-step.-

Keywords:

- analog-to-digital converter,

- SAR,

- hybrid ADC

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] -

Proportional views

DownLoad:

DownLoad: