| Citation: |

D. Suresh, K. K. Nagarajan, R. Srinivasan. The impact of process variations on input impedance and mitigation using a circuit technique in FinFET-based LNA[J]. Journal of Semiconductors, 2015, 36(4): 045002. doi: 10.1088/1674-4926/36/4/045002

****

D. Suresh, K. K. Nagarajan, R. Srinivasan. The impact of process variations on input impedance and mitigation using a circuit technique in FinFET-based LNA[J]. J. Semicond., 2015, 36(4): 045002. doi: 10.1088/1674-4926/36/4/045002.

|

The impact of process variations on input impedance and mitigation using a circuit technique in FinFET-based LNA

DOI: 10.1088/1674-4926/36/4/045002

More Information

-

Abstract

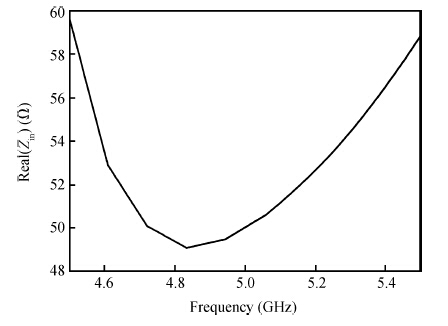

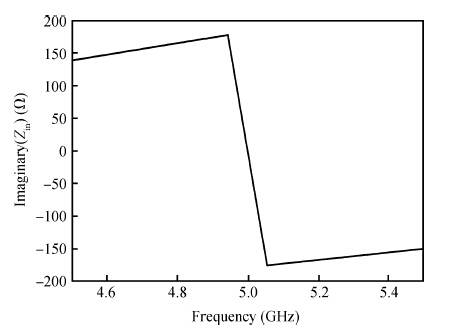

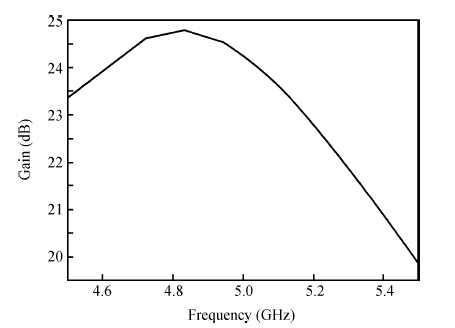

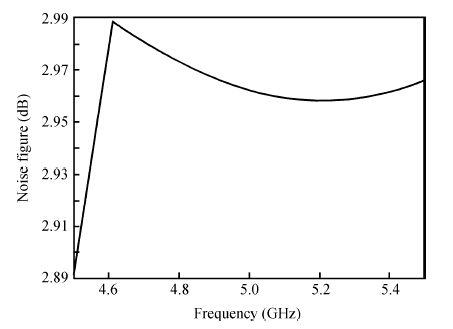

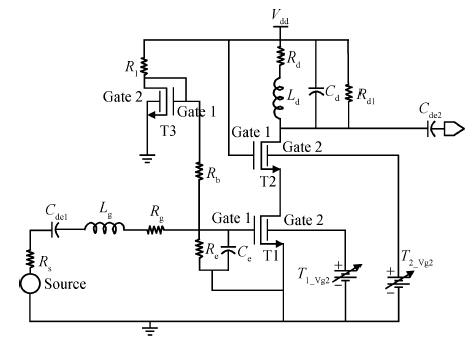

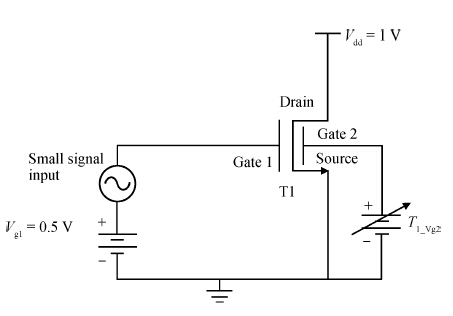

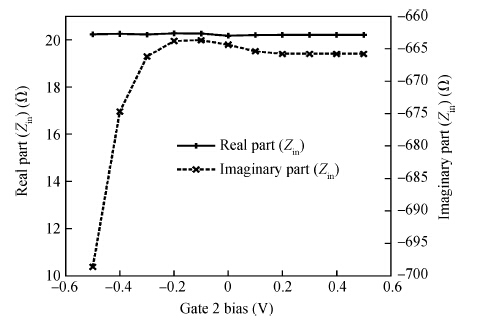

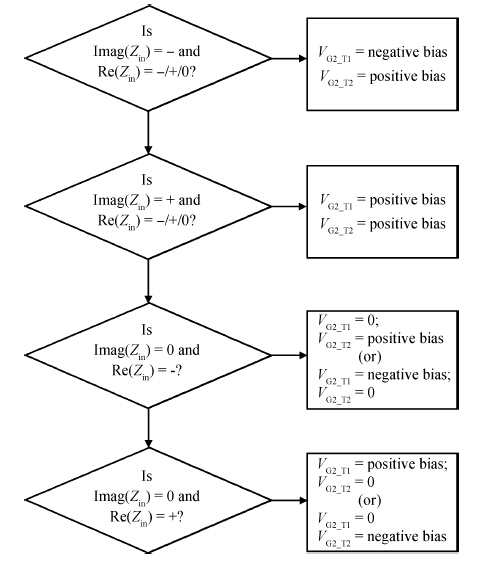

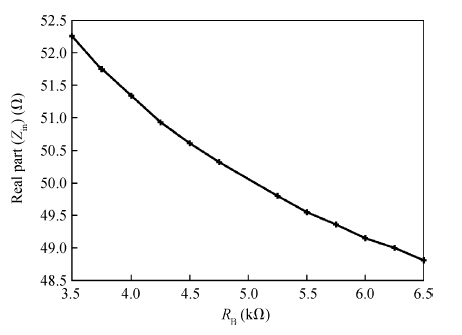

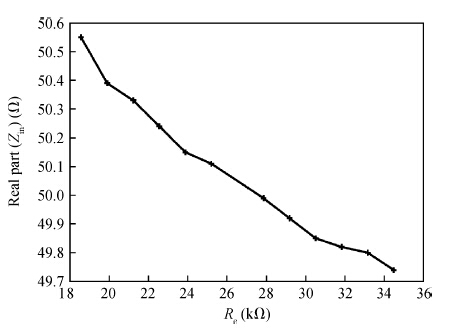

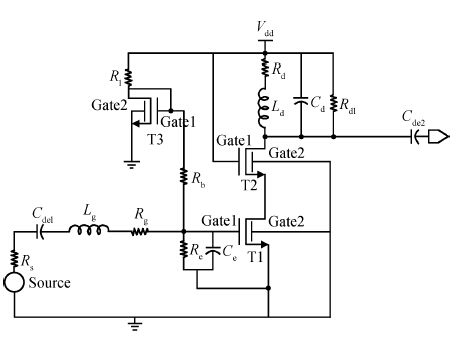

The effect of process variations of a FinFET-based low noise amplifier (LNA) are mitigated by using the device in an independently driven mode, i.e. an independently driven double gate (IDDG) FinFET. A 45 nm gate length IDDG FinFET-based cascoded LNA, operating at 5 GHz, is designed and studied to assess the impact of process variation on the LNA performance metrics such as input impedance, gain and noise figure. Four geometrical parameters, gate length, channel width, gate oxide thickness and fin width, and one non-geometrical parameter, channel doping concentration, are considered in the study. The effect of these variations on the input impedance (the desired value is 50 Ω purely real) of the LNA is compensated by the second gate bias of the IDDG FinFET.-

Keywords:

- FinFET,

- LNA,

- process variation,

- T-SPICE

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] -

Proportional views

DownLoad:

DownLoad: