| Citation: |

Xue Yang, Hao Yang, Haiying Zhang, Xinnian Zheng, Zhiwei Dai, Zhiqiang Li, Zebao Du. A monolithic 60 GHz balanced low noise amplifier[J]. Journal of Semiconductors, 2015, 36(4): 045003. doi: 10.1088/1674-4926/36/4/045003

****

X Yang, H Yang, H Y Zhang, X N Zheng, Z W Dai, Z Q Li, Z B Du. A monolithic 60 GHz balanced low noise amplifier[J]. J. Semicond., 2015, 36(4): 045003. doi: 10.1088/1674-4926/36/4/045003.

|

A monolithic 60 GHz balanced low noise amplifier

DOI: 10.1088/1674-4926/36/4/045003

More Information

-

Abstract

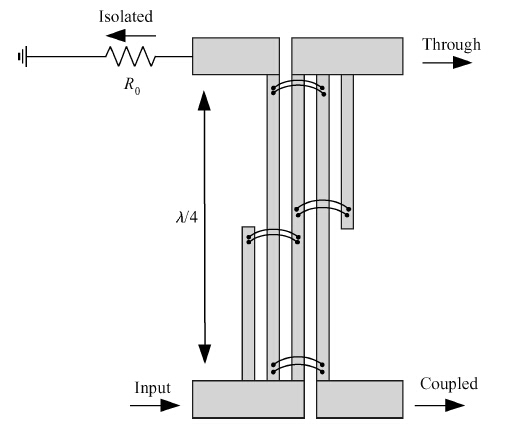

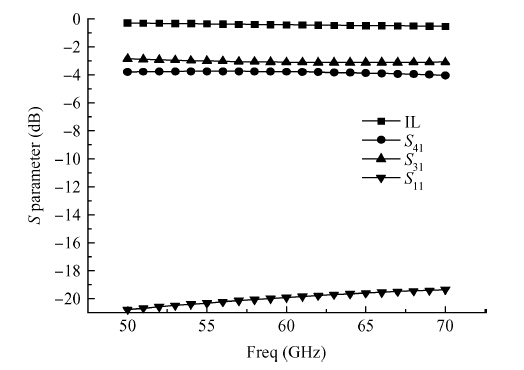

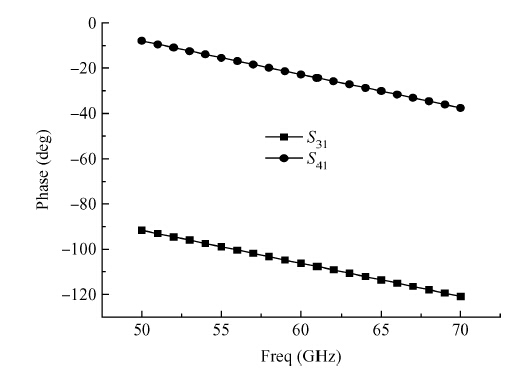

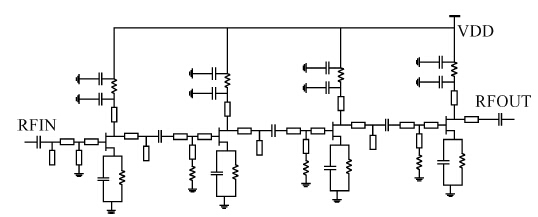

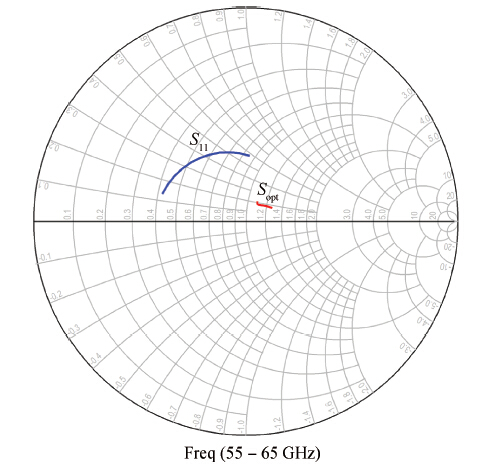

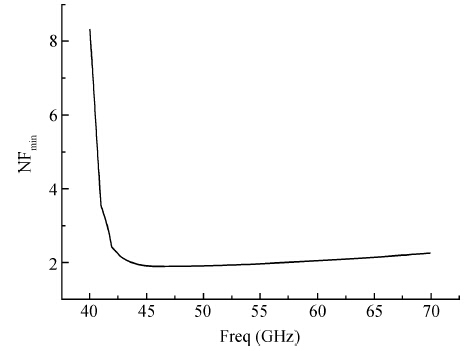

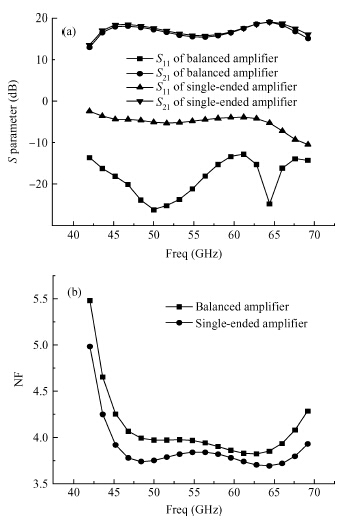

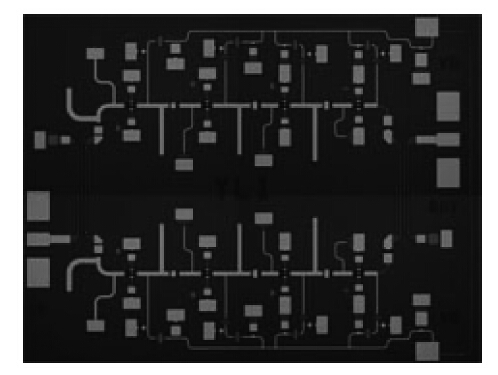

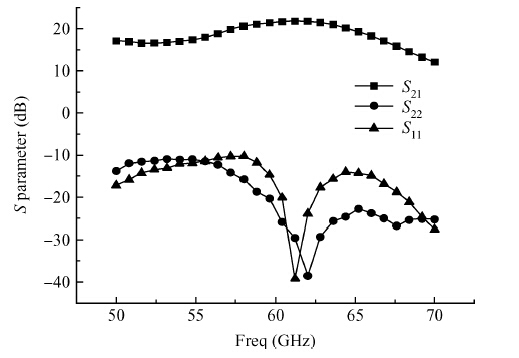

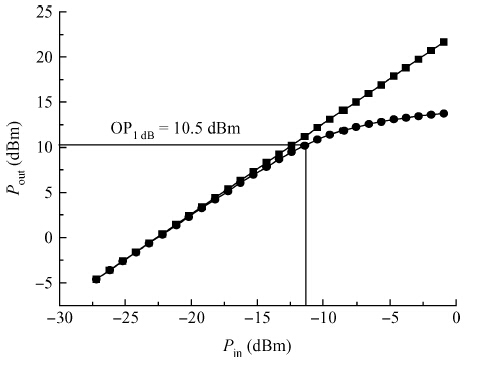

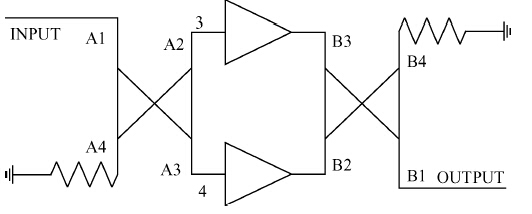

This paper presents a 60 GHz balanced low noise amplifier. Compared with single-ended structures, the balanced structure can obtain a better input/output return loss, a lower noise figure (NF), a 3 dB improvement of the 1 dB compression point, a 6 dB improvement of IM3 and a doubled dynamic range. Each single-ended amplifier in this paper uses a four-stage cascade structure to achieve a high gain in broadband. At the operating frequency range of 59-64 GHz, the small signal gain of the balanced amplifier is more than 20 dB. Both the input and output return losses are less than -12 dB. The output 1 dB compression power is 10.5 dBm at 60 GHz. The simulation result for the NF is better than 3.9 dB. The chip is fabricated using a 0.15 μm GaAs pHEMT process with a size of 2.25 × 1.7 mm2.-

Keywords:

- balanced amplifier,

- 60 GHz,

- low noise

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] -

Proportional views

DownLoad:

DownLoad: