| Citation: |

Xue Han, Qi Wei, Huazhong Yang, Hui Wang. A single channel, 6-bit 410-MS/s 3bits/stage asynchronous SAR ADC based on resistive DAC[J]. Journal of Semiconductors, 2015, 36(5): 055010. doi: 10.1088/1674-4926/36/5/055010

****

X Han, Q Wei, H Z Yang, H Wang. A single channel, 6-bit 410-MS/s 3bits/stage asynchronous SAR ADC based on resistive DAC[J]. J. Semicond., 2015, 36(5): 055010. doi: 10.1088/1674-4926/36/5/055010.

|

A single channel, 6-bit 410-MS/s 3bits/stage asynchronous SAR ADC based on resistive DAC

DOI: 10.1088/1674-4926/36/5/055010

More Information

-

Abstract

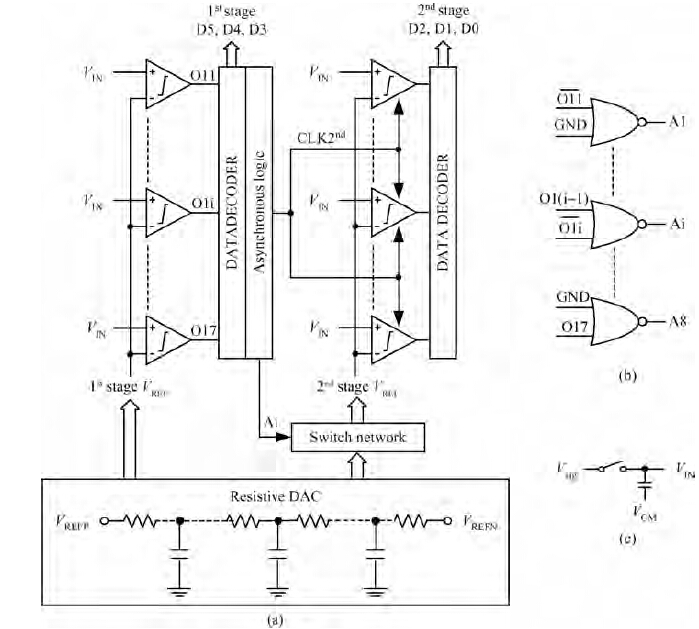

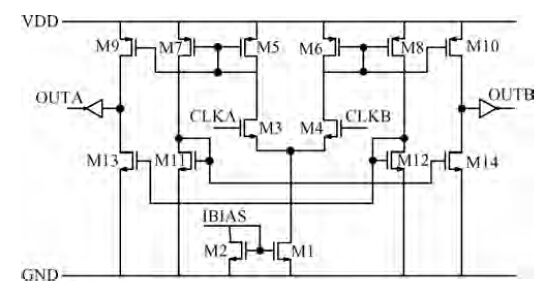

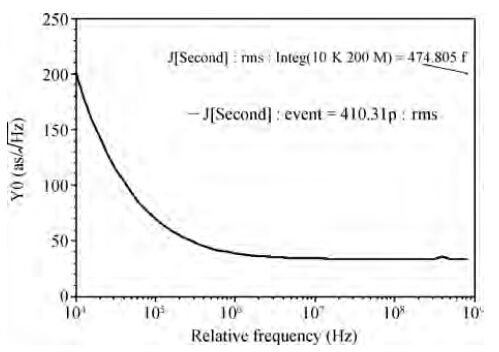

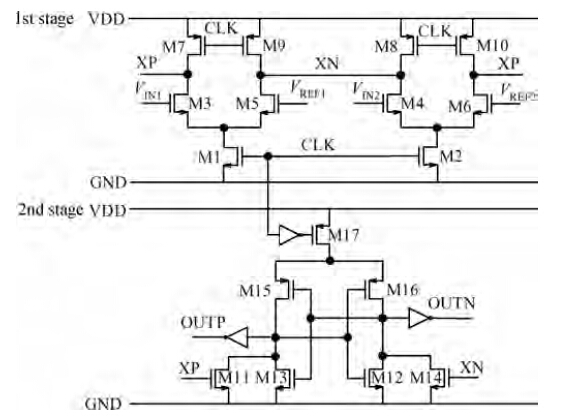

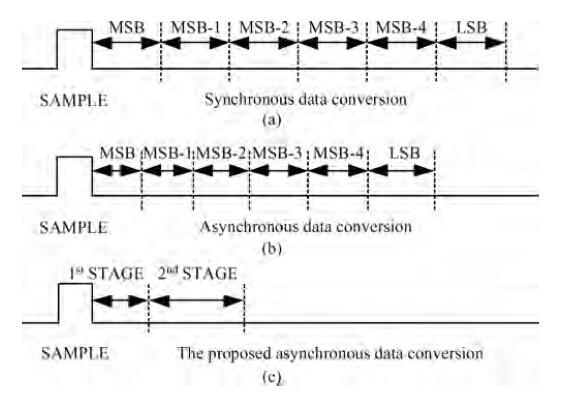

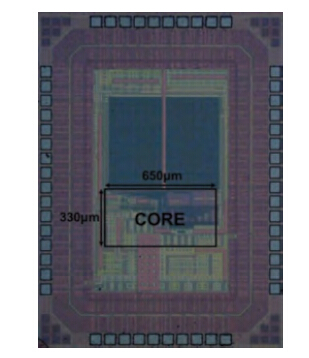

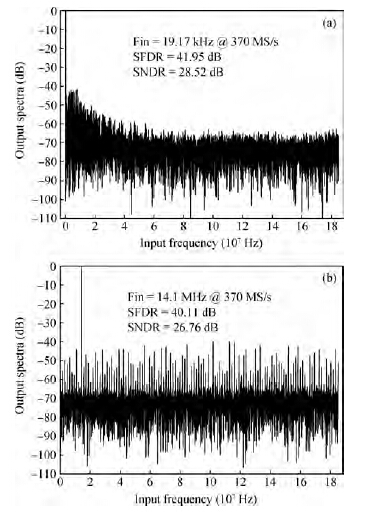

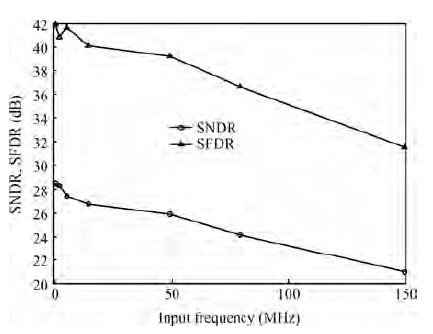

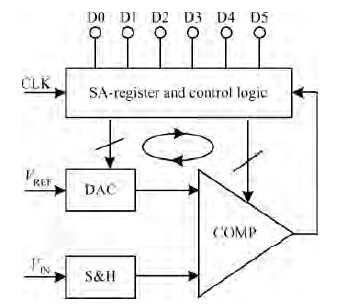

This paper presents a single channel, low power 6-bit 410-MS/s asynchronous successive approximation register analog-to-digital converter (SAR ADC) for ultrawide bandwidth (UWB) communication, prototyped in a SMIC 65-nm process. Based on the 3 bits/stage structure, resistive DAC, and the modified asynchronous successive approximation register control logic, the proposed ADC attains a peak spurious-free dynamic range (SFDR) of 41.95 dB, and a signal-to-noise and distortion ratio (SNDR) of 28.52 dB for 370 MS/s. At the sampling rate of 410 MS/s, this design still performs well with a 40.71-dB SFDR and 30.02-dB SNDR. A four-input dynamic comparator is designed so as to decrease the power consumption. The measurement results indicate that this SAR ADC consumes 2.03 mW, corresponding to a figure of merit of 189.17 fJ/step at 410 MS/s. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] -

Proportional views

DownLoad:

DownLoad: