| Citation: |

Chixiao Chen, Jixuan Xiang, Huabin Chen, Jun Xu, Fan Ye, Ning Li, Junyan Ren. A capacitive DAC with custom 3-D 1-fF MOM unit capacitors optimized for fast-settling routing in high speed SAR ADCs[J]. Journal of Semiconductors, 2015, 36(5): 055011. doi: 10.1088/1674-4926/36/5/055011

****

C X Chen, J X Xiang, H B Chen, J Xu, F Ye, N Li, J Y Ren. A capacitive DAC with custom 3-D 1-fF MOM unit capacitors optimized for fast-settling routing in high speed SAR ADCs[J]. J. Semicond., 2015, 36(5): 055011. doi: 10.1088/1674-4926/36/5/055011.

|

A capacitive DAC with custom 3-D 1-fF MOM unit capacitors optimized for fast-settling routing in high speed SAR ADCs

DOI: 10.1088/1674-4926/36/5/055011

More Information

-

Abstract

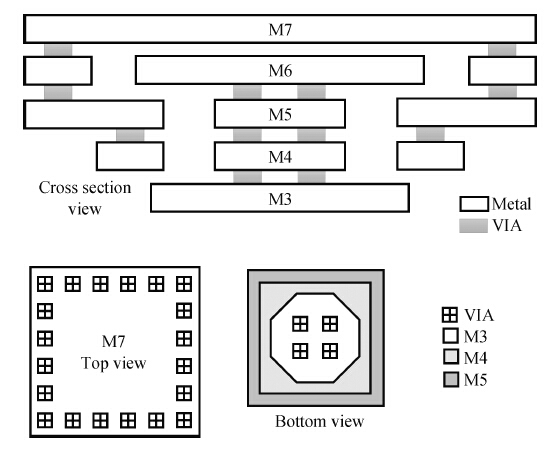

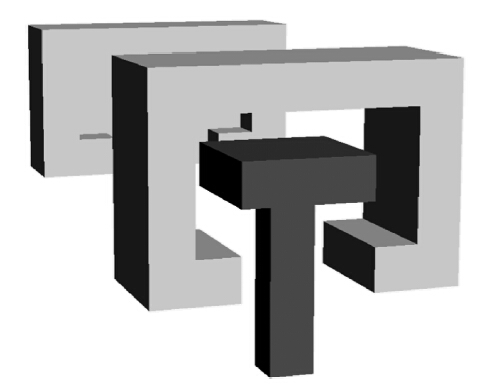

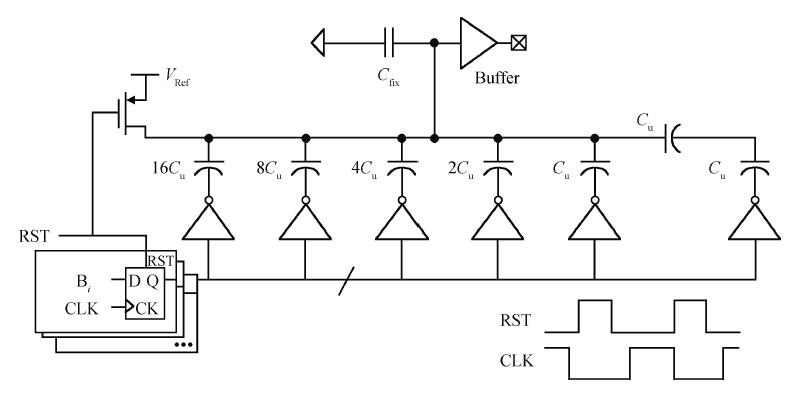

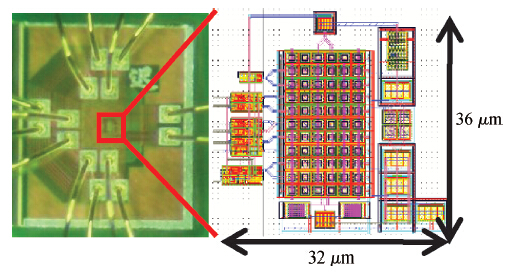

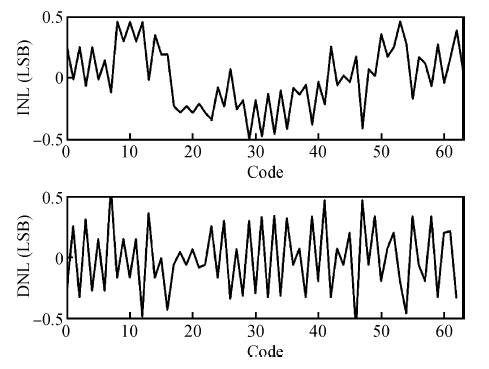

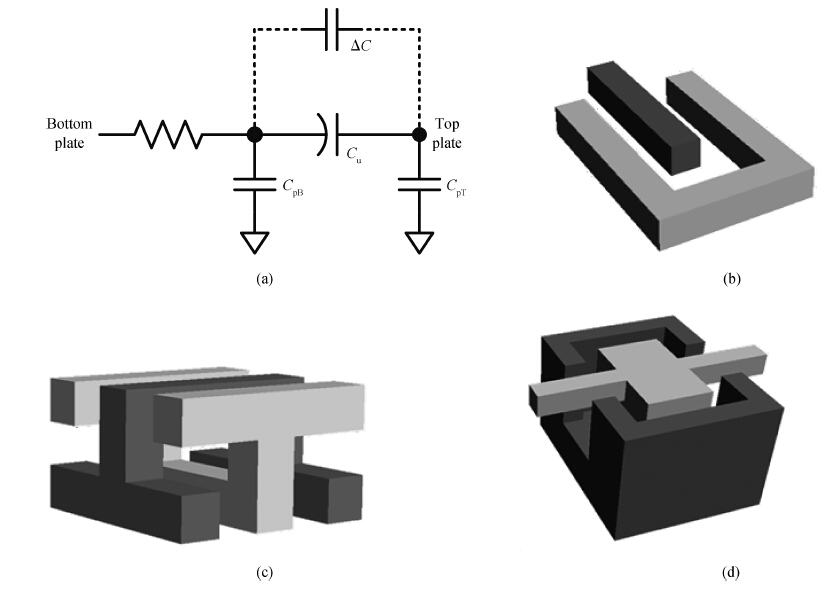

Asynchronous successive approximation register (SAR) analog-to-digital converters (ADC) feature high energy efficiency but medium performance. From the point of view of speed, the key bottleneck is the unit capacitor size. In this paper, a small size three-dimensional (3-D) metal-oxide-metal (MOM) capacitor is proposed. The unit capacitor has a capacitance of 1-fF. It shapes as an umbrella, which is designed for fast settling consideration. A comparison among the proposed capacitor with other 3-D MOM capacitors is also given in the paper. To demonstrate the effectiveness of the MOM capacitor, a 6-b capacitive DAC is implemented in TSMC 1P9M 65 nm LP CMOS technology. The DAC consumes a power dissipation of 0.16 mW at the rate of 100 MS/s, excluding a source-follower based output buffer. Static measurement result shows that INL is less than ± 1 LSB and DNL is less than ± 0.5 LSB. In addition, a 100 MS/s 9-bit SAR ADC with the proposed 3-D capacitor is simulated. -

References

[1] [2] [3] [4] [5] [6] -

Proportional views

DownLoad:

DownLoad: