| Citation: |

Yue Han, Shushan Qiao, Yong Hei. A high-linearity and high-resolution delay line structure with a calibration algorithm in delay-based LINC transmitters[J]. Journal of Semiconductors, 2016, 37(1): 015003. doi: 10.1088/1674-4926/37/1/015003

****

Y Han, S S Qiao, Y Hei. A high-linearity and high-resolution delay line structure with a calibration algorithm in delay-based LINC transmitters[J]. J. Semicond., 2016, 37(1): 015003. doi: 10.1088/1674-4926/37/1/015003.

|

A high-linearity and high-resolution delay line structure with a calibration algorithm in delay-based LINC transmitters

DOI: 10.1088/1674-4926/37/1/015003

More Information

-

Abstract

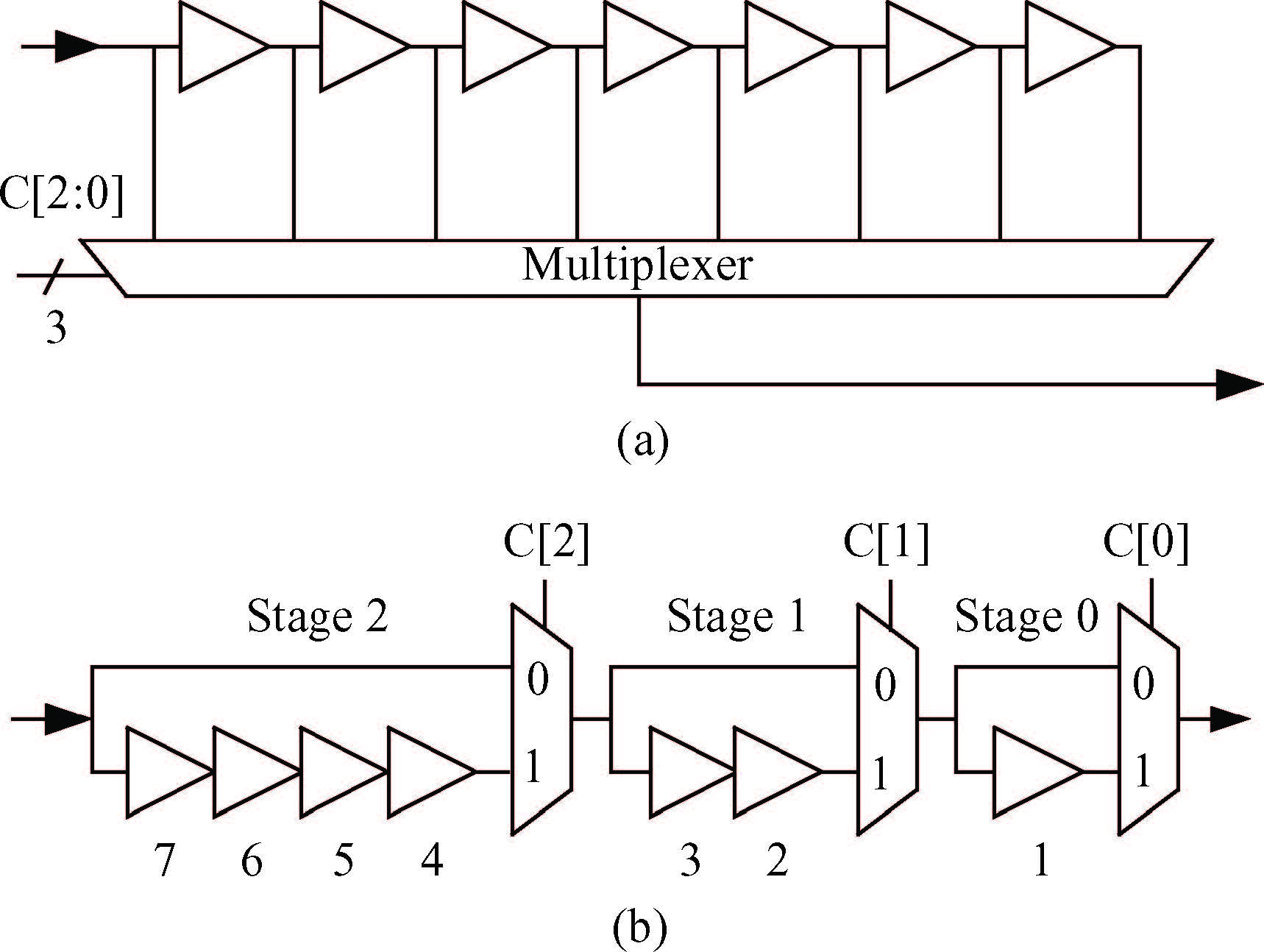

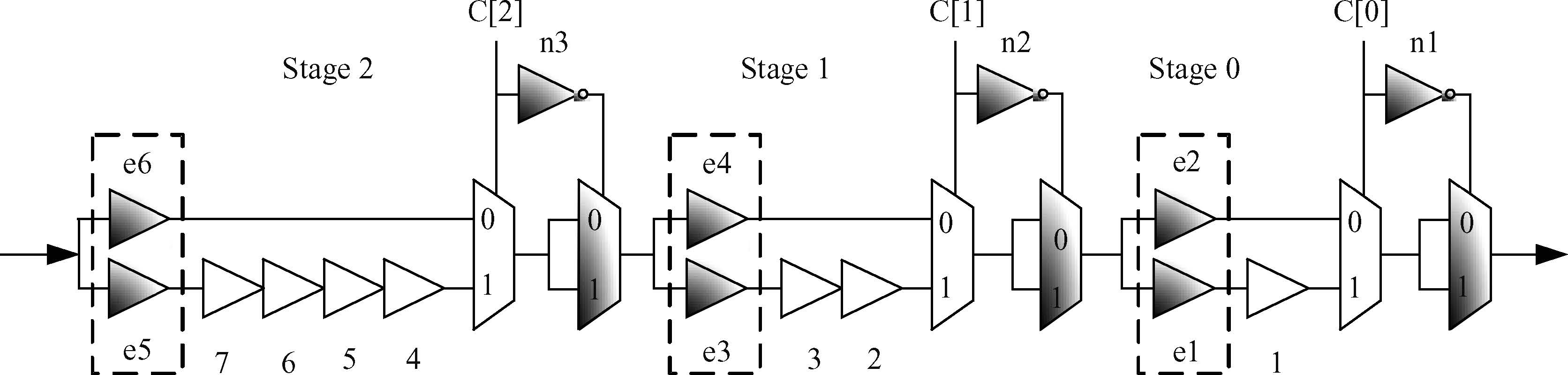

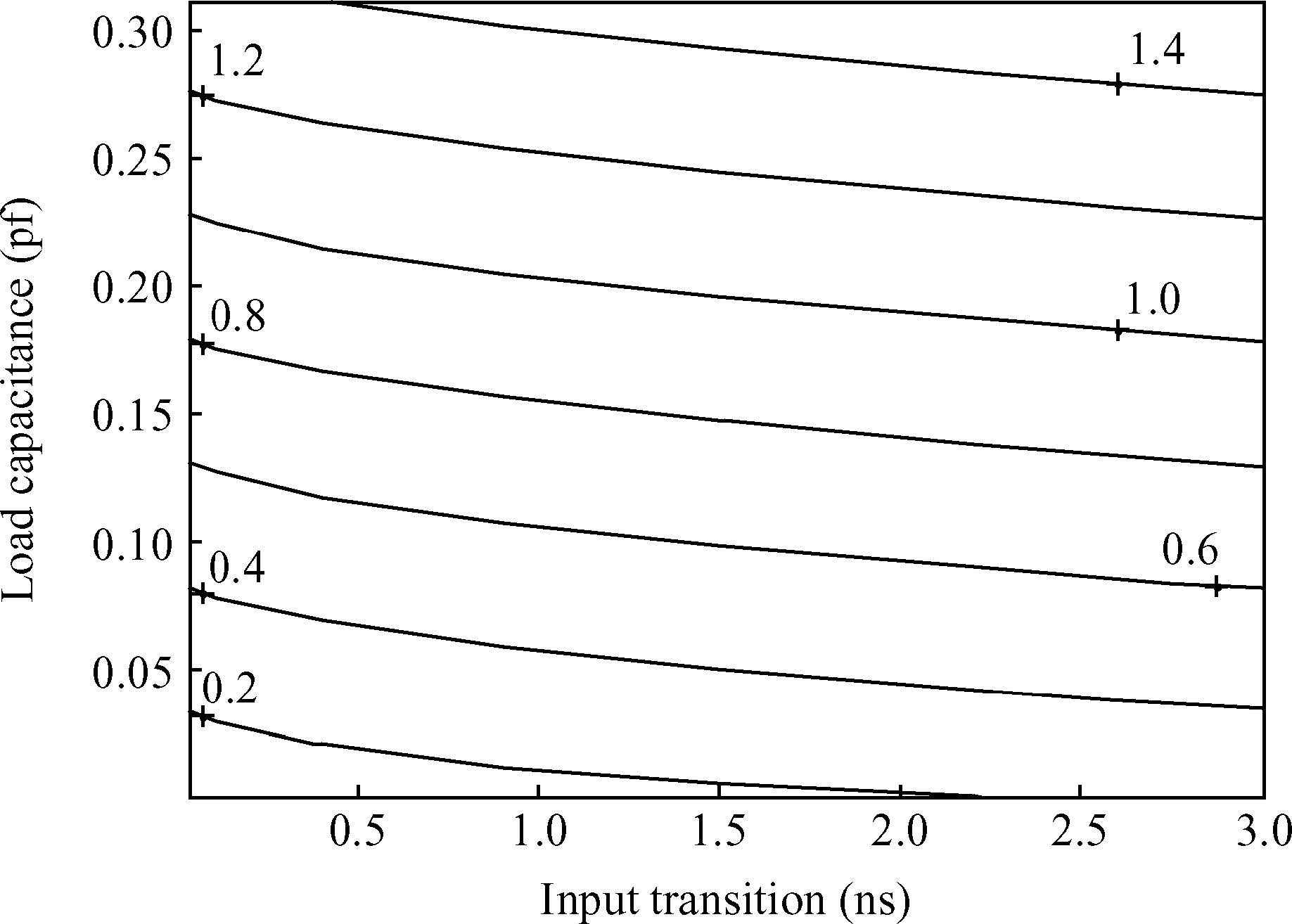

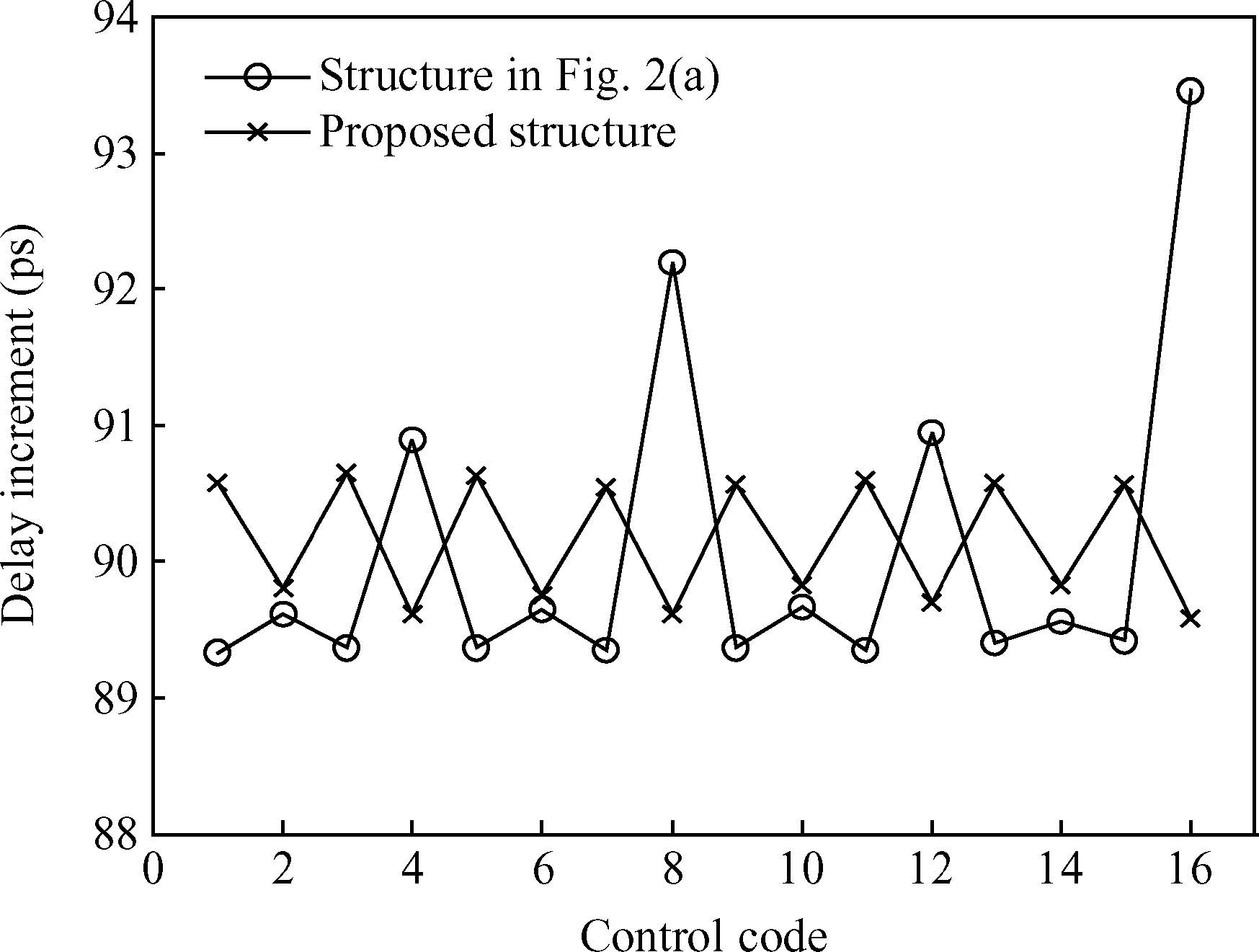

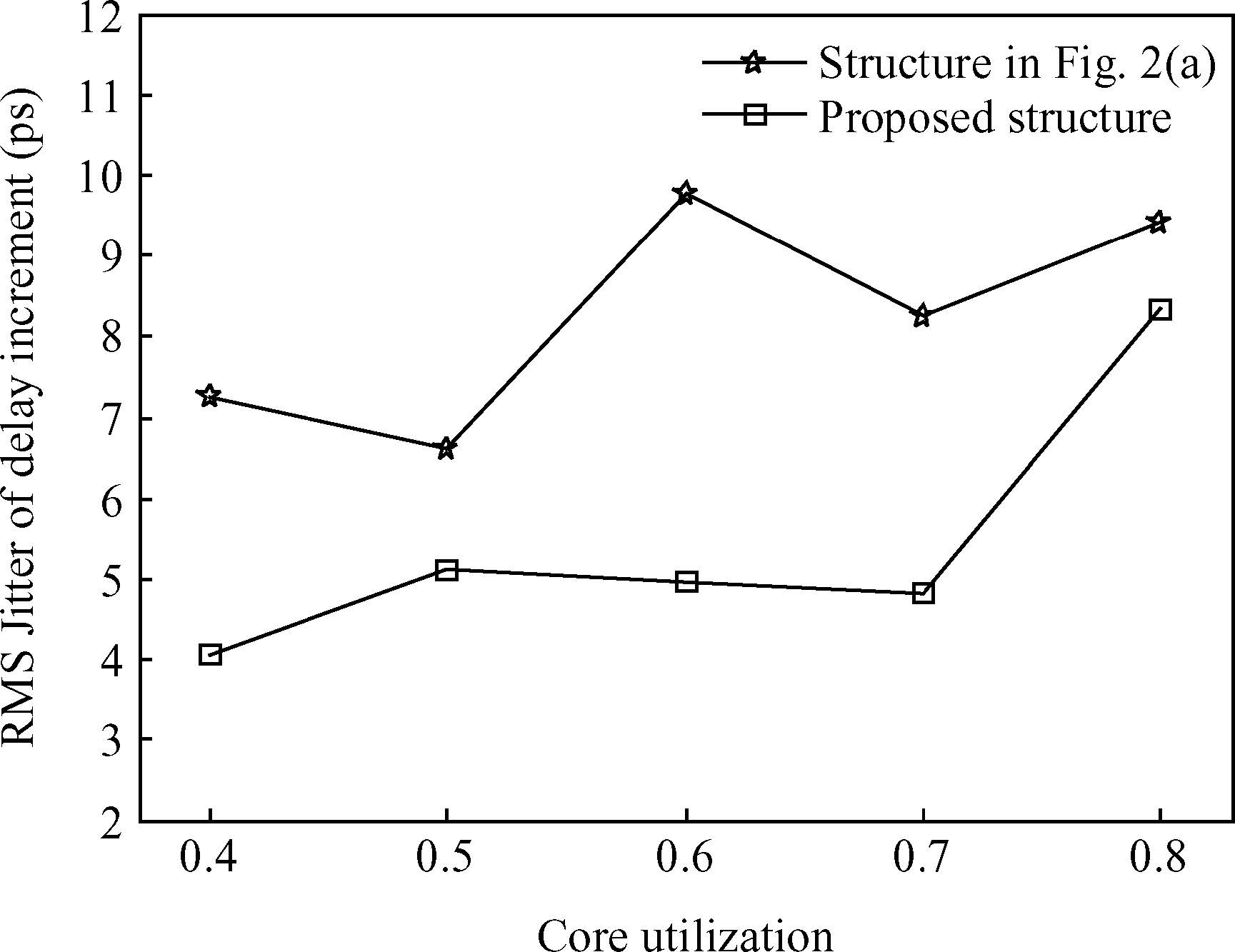

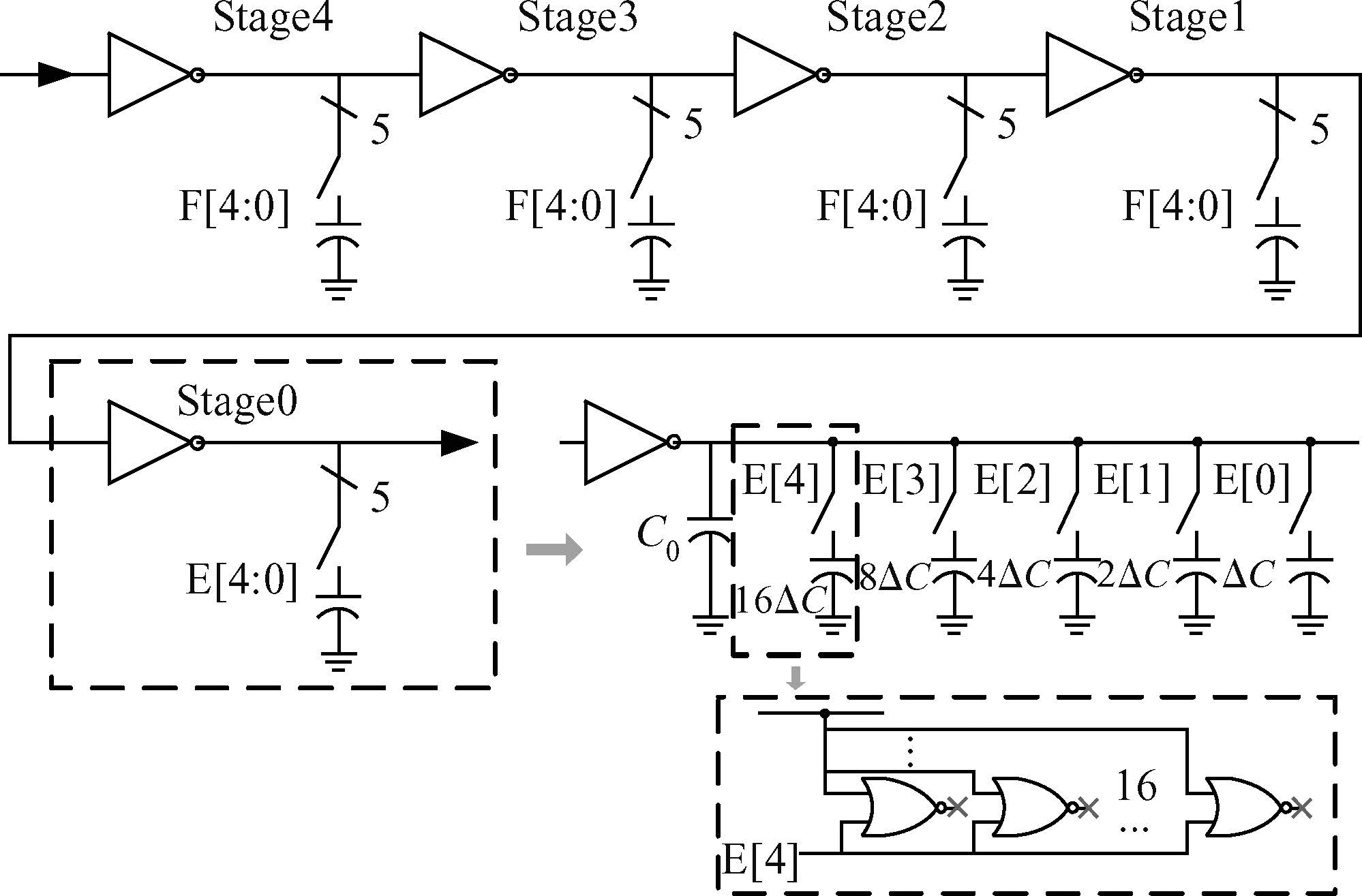

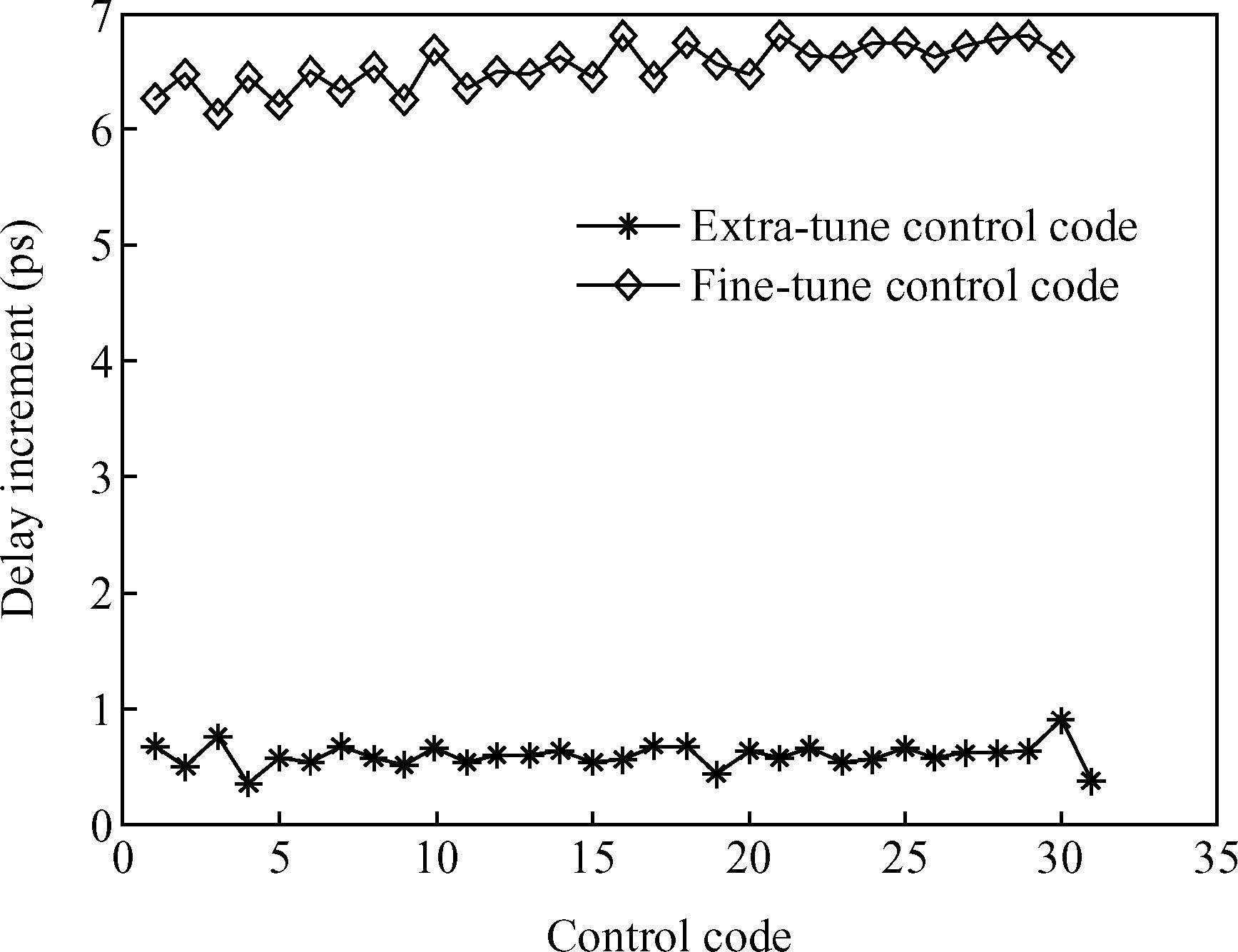

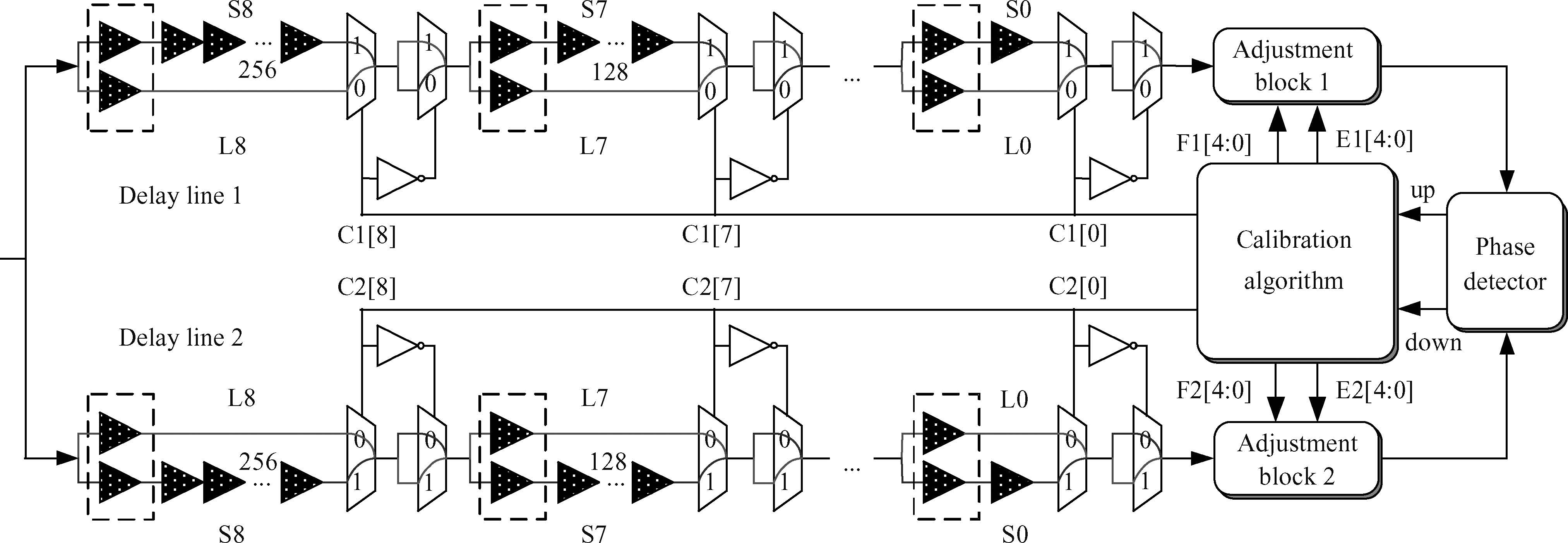

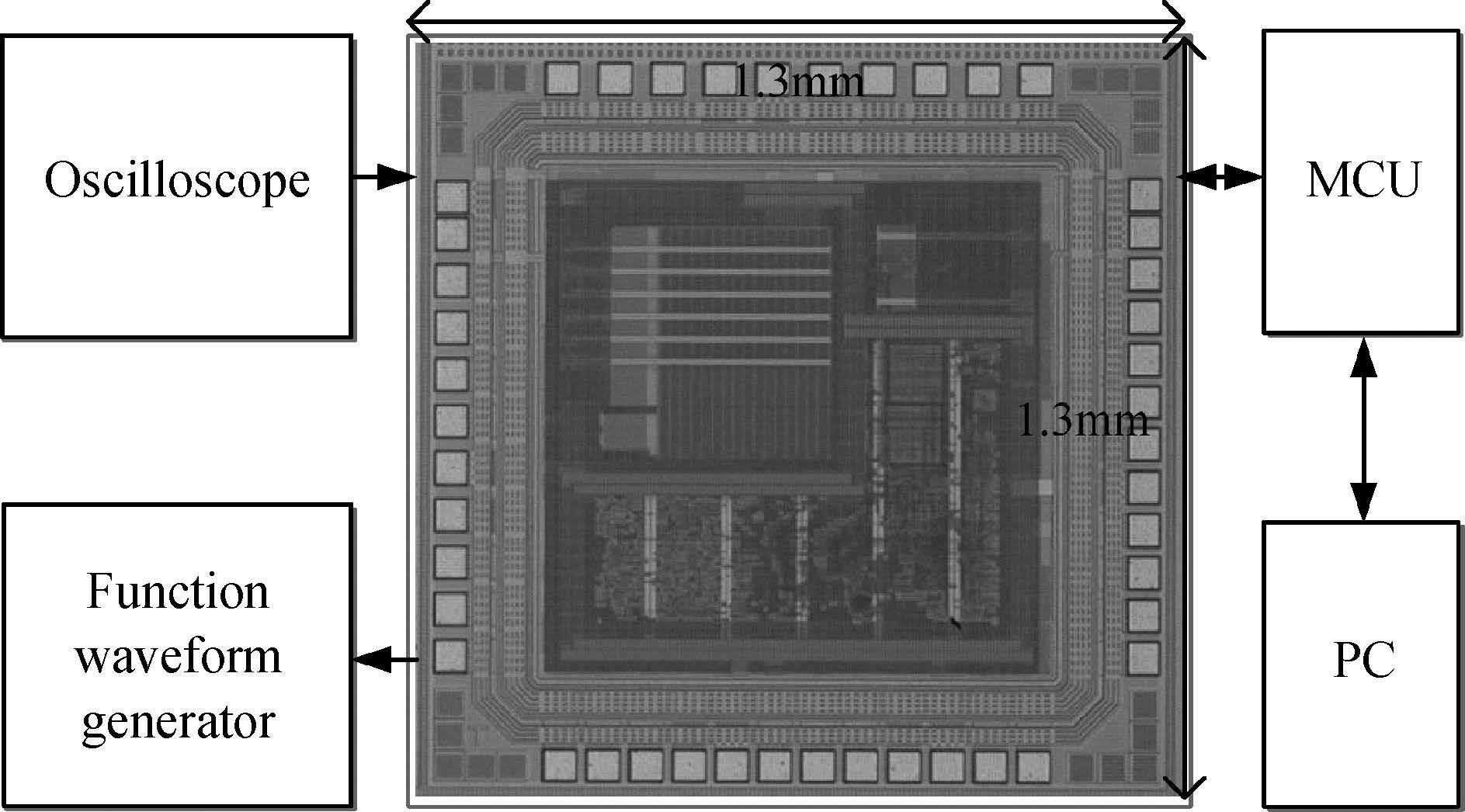

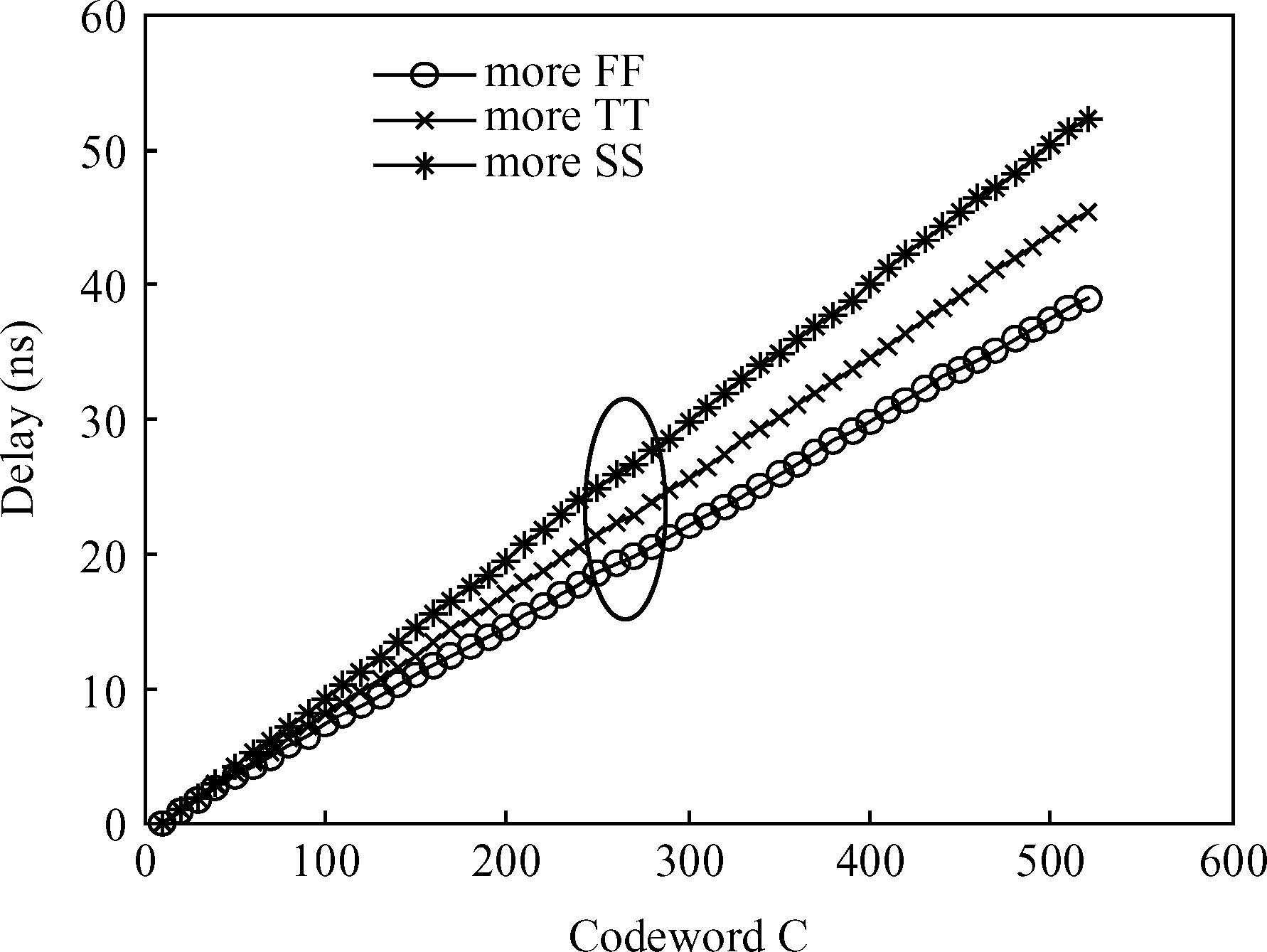

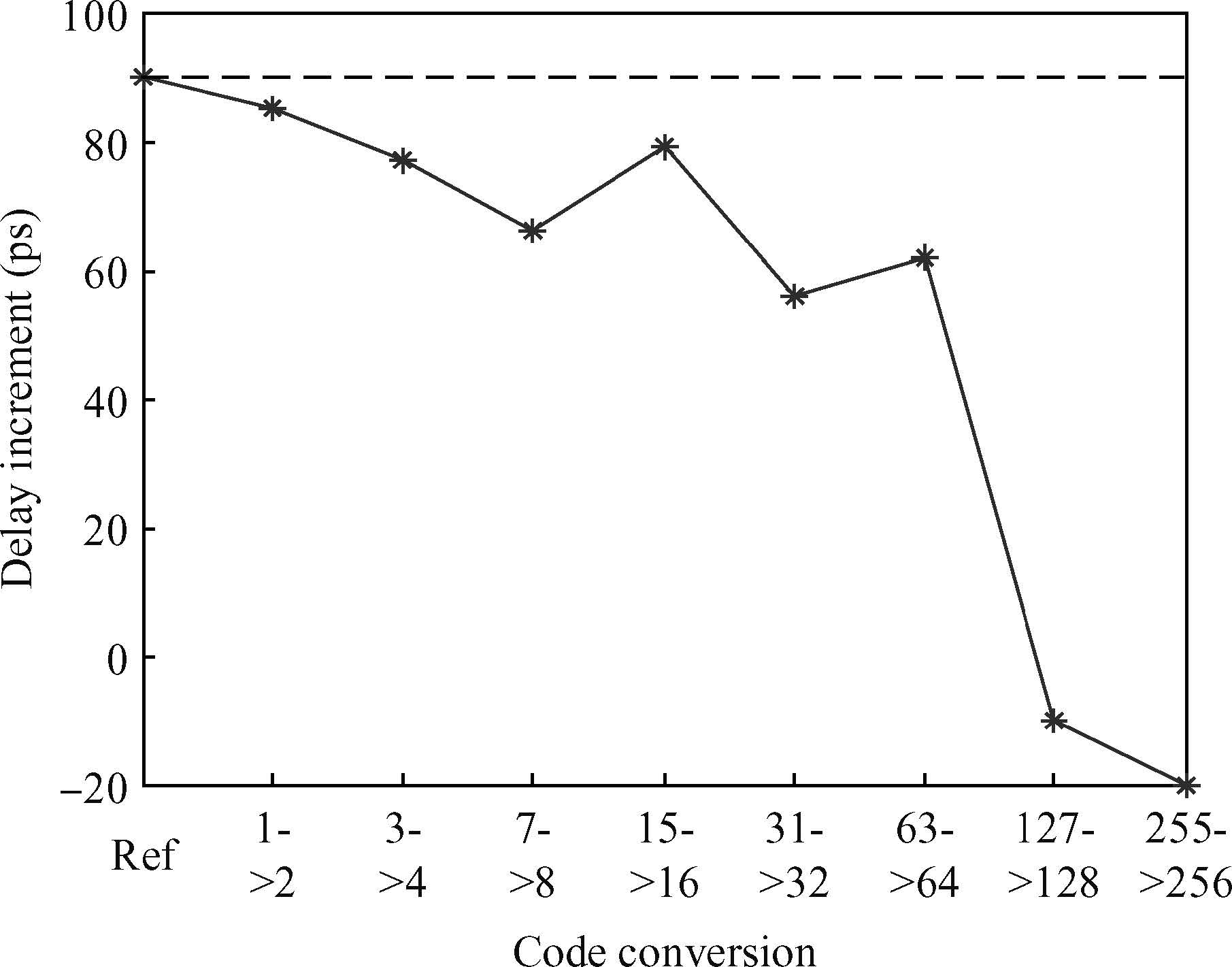

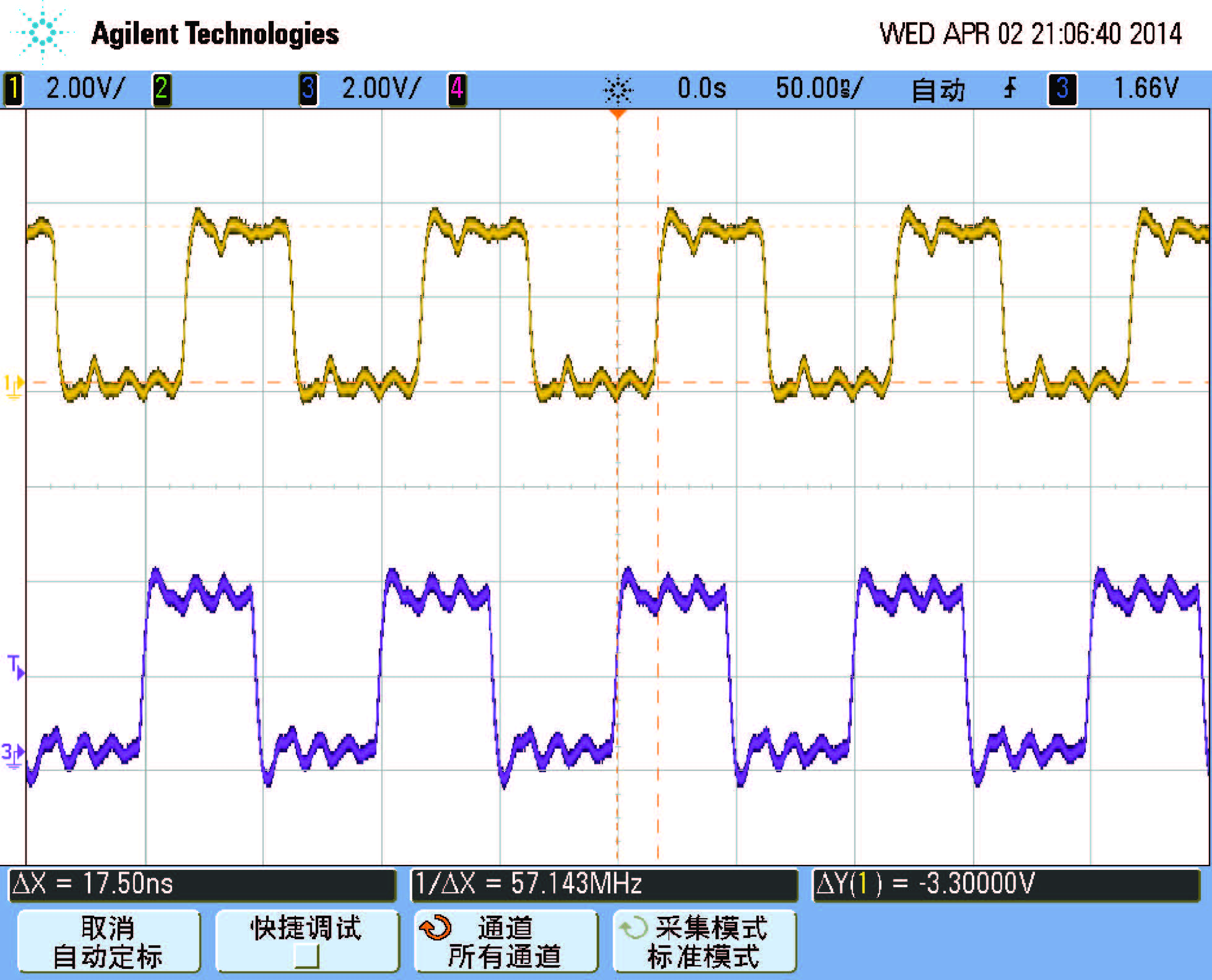

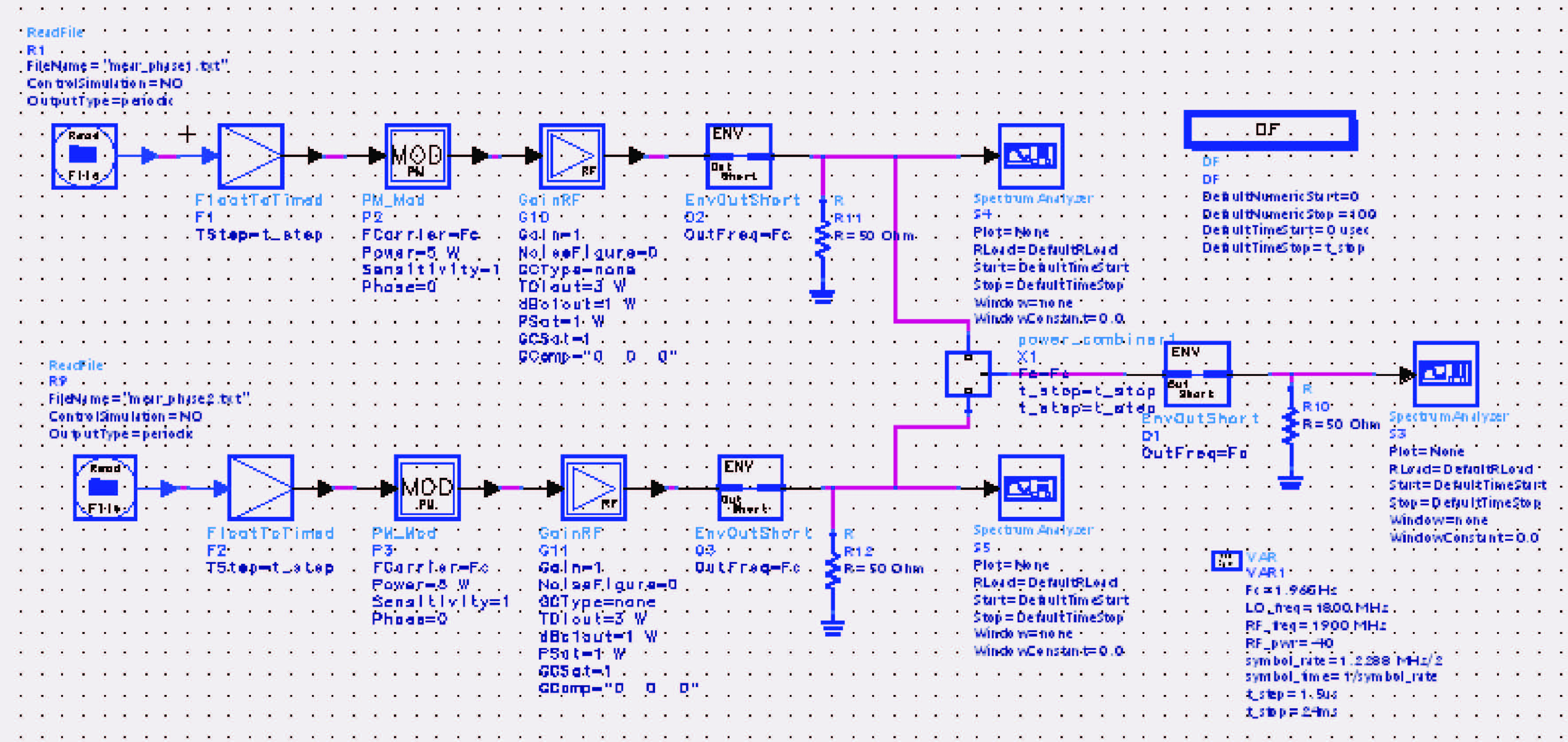

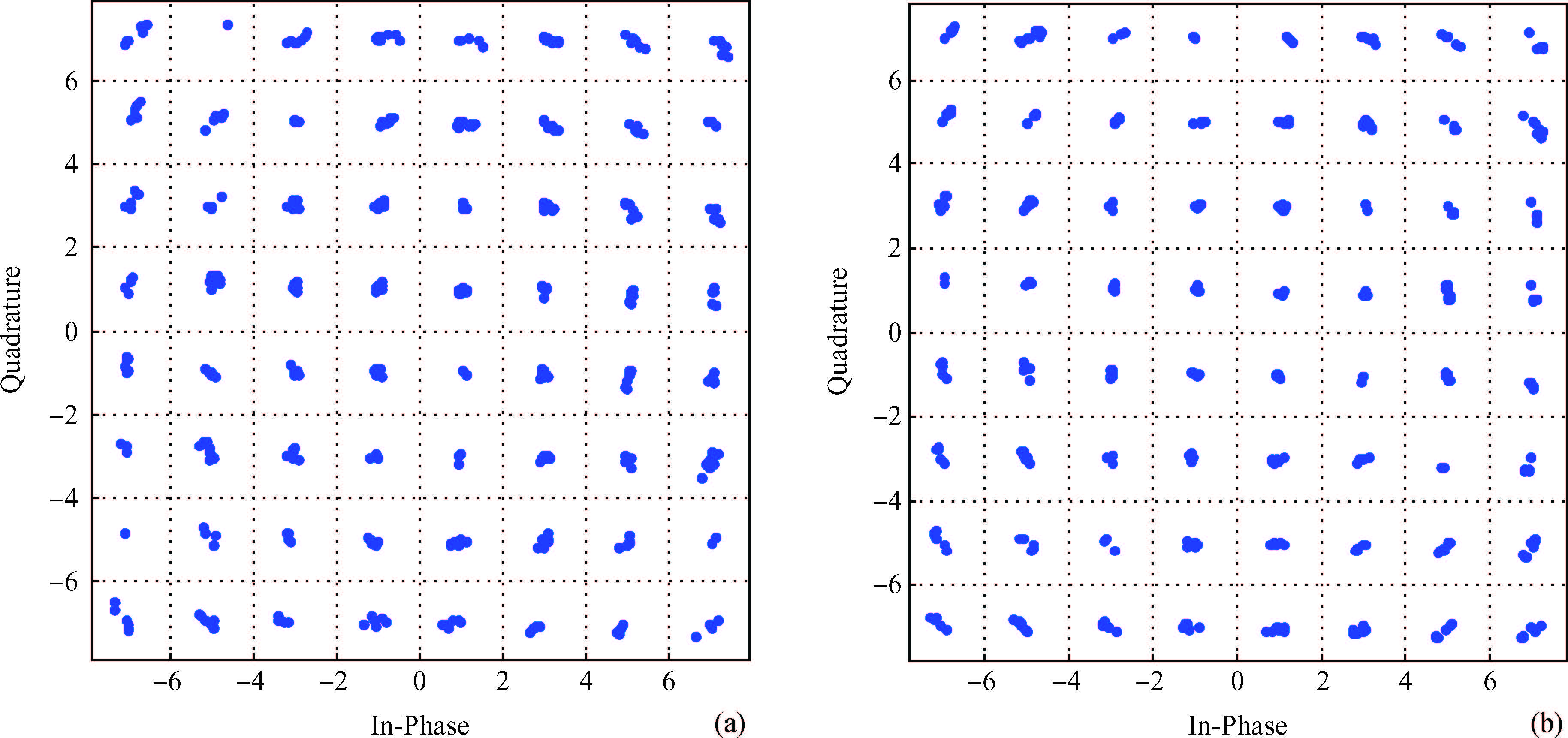

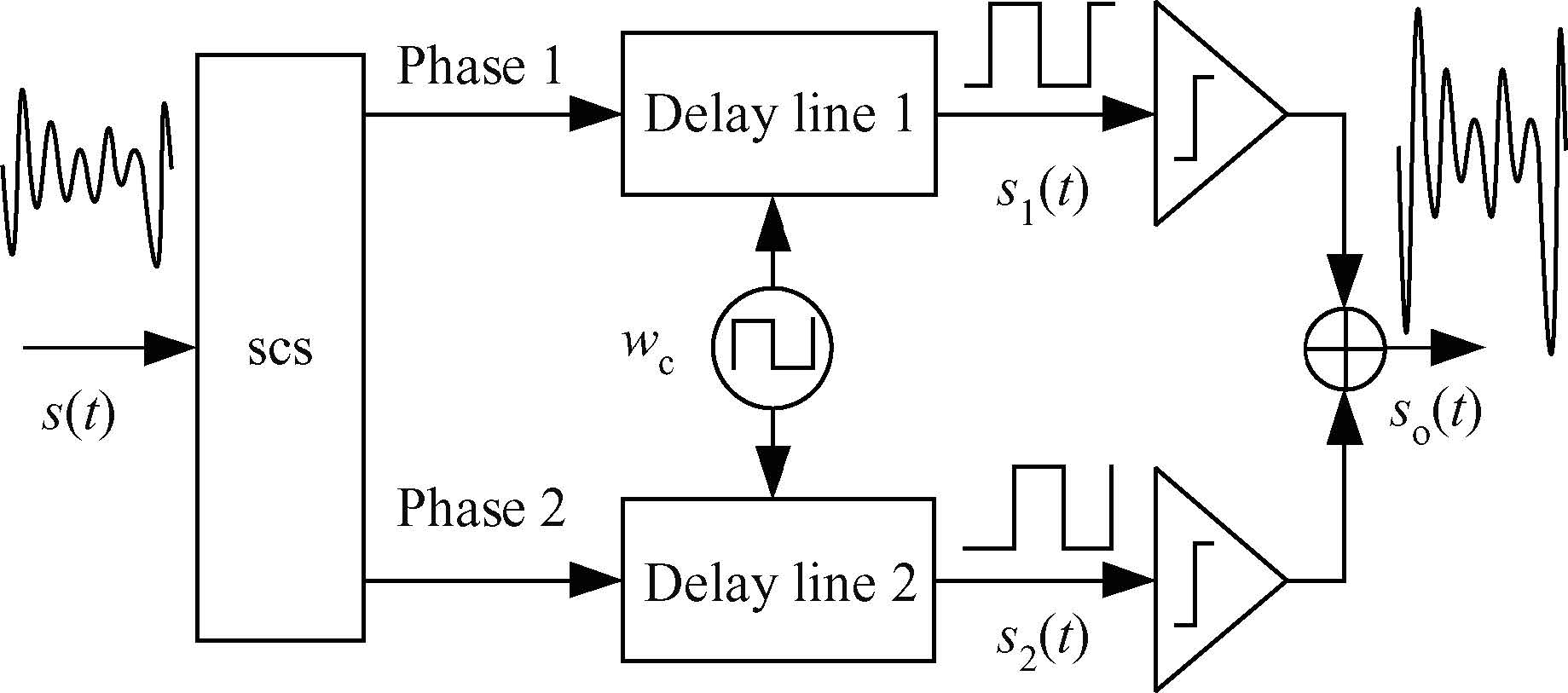

In order to overcome the bottleneck of low linearity and low resolution, an improved delay line structure is proposed with a calibration algorithm to conquer PVT (process, voltage and temperature) variations for an all-digital design. The chip is implemented in 0.13 μ m CMOS technology. Measurement results show that the proposed structure with the calibration algorithm can evidently improve the linearity and resolution of the delay line. The delay resolution is 2 ps and the root mean square jitter of the delay is 4.71 ps, leading to an error vector magnitude enhancement of 1.32 dB. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] -

Proportional views

DownLoad:

DownLoad: