| Citation: |

Dong Li, Qiao Meng, Fei Li. A 10 bit 50 MS/s SAR ADC with partial split capacitor switching scheme in 0.18 μm CMOS[J]. Journal of Semiconductors, 2016, 37(1): 015004. doi: 10.1088/1674-4926/37/1/015004

****

D Li, Q Meng, F Li. A 10 bit 50 MS/s SAR ADC with partial split capacitor switching scheme in 0.18 μm CMOS[J]. J. Semicond., 2016, 37(1): 015004. doi: 10.1088/1674-4926/37/1/015004.

|

A 10 bit 50 MS/s SAR ADC with partial split capacitor switching scheme in 0.18 μm CMOS

DOI: 10.1088/1674-4926/37/1/015004

More Information

-

Abstract

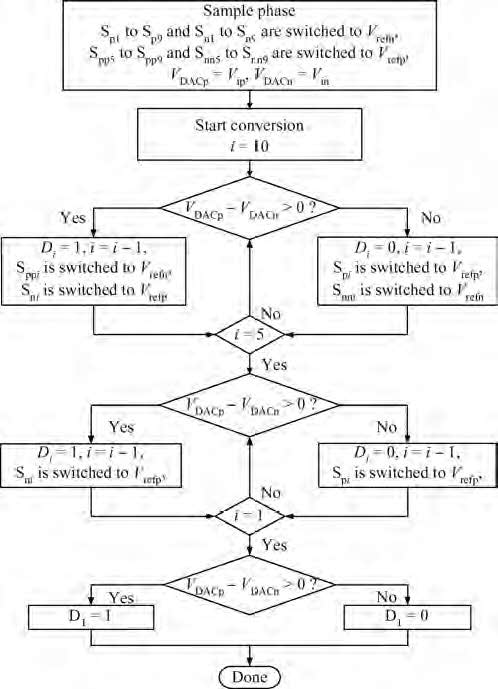

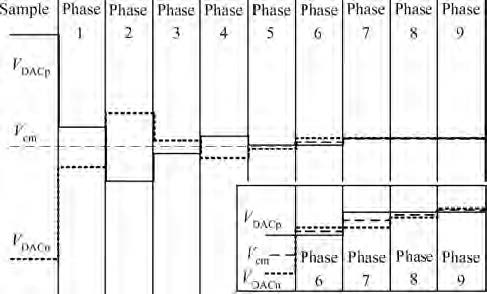

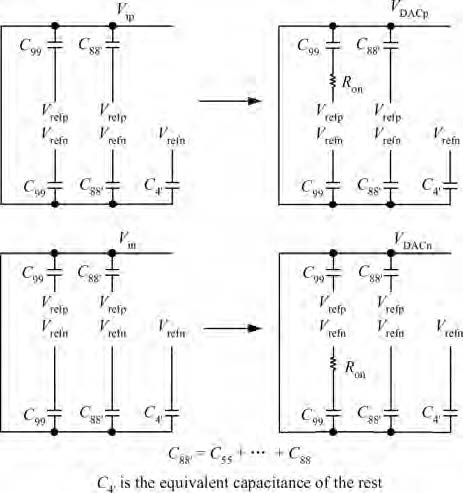

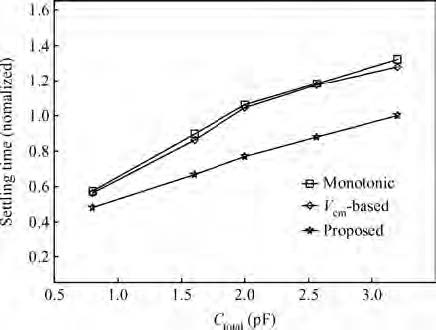

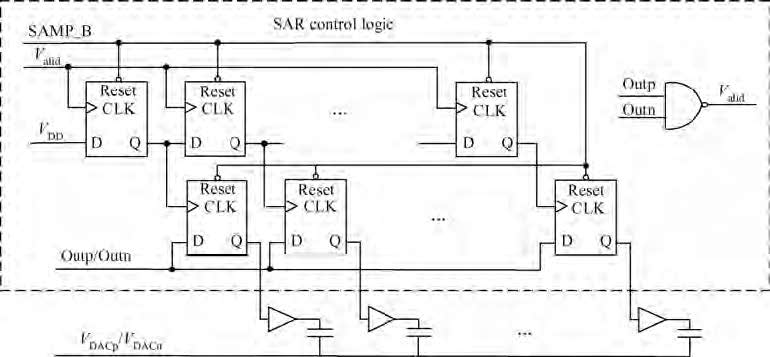

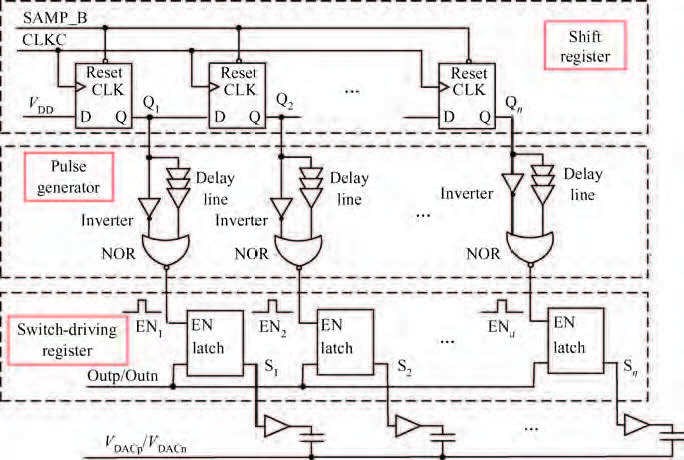

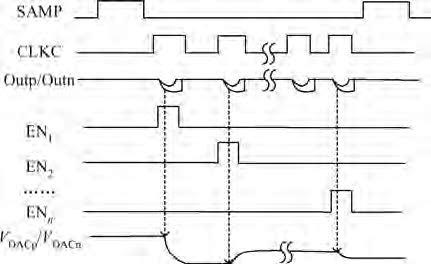

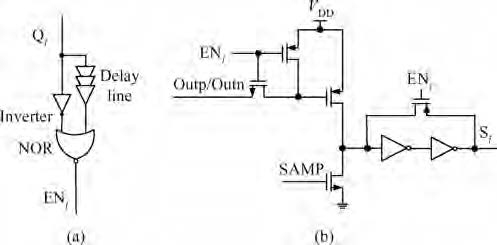

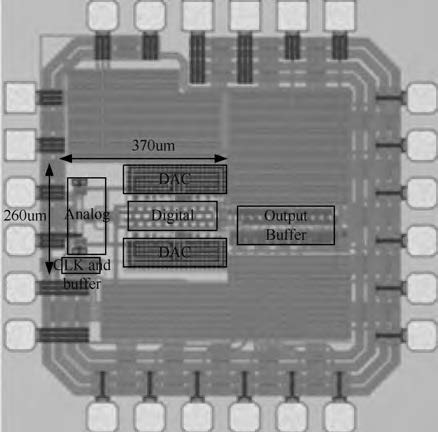

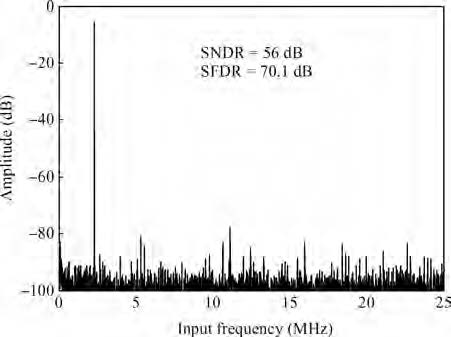

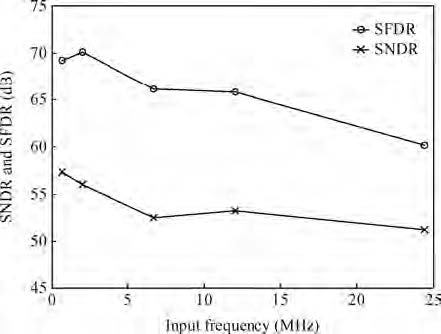

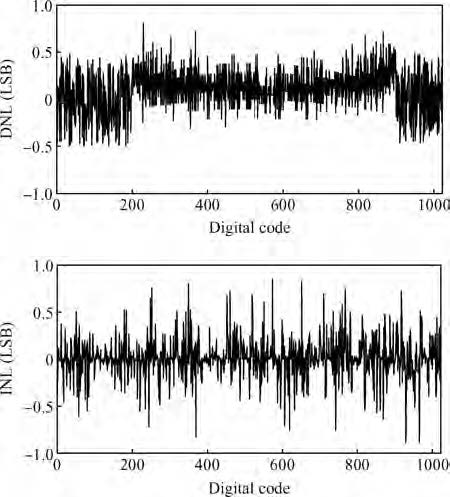

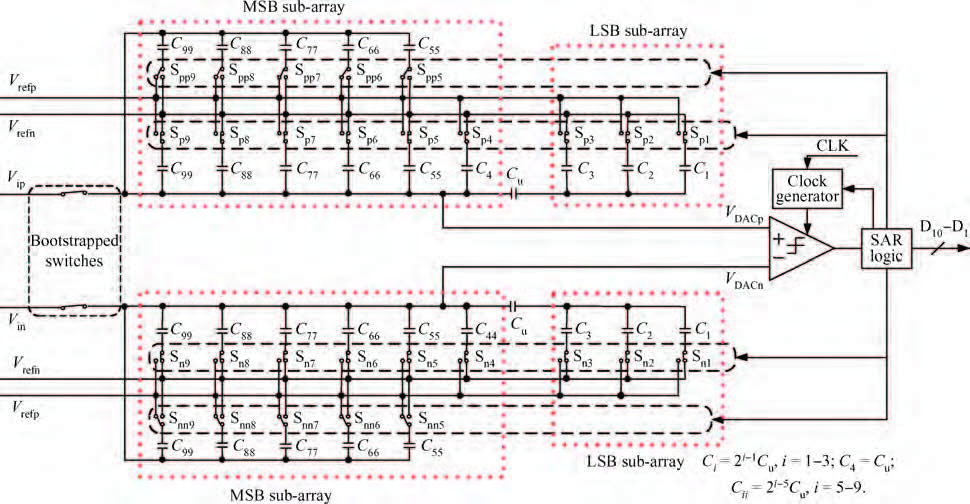

This paper presents a 10 bit successive approximation register (SAR) analog-to-digital converter (ADC) in 0.18 μ m 1P6M CMOS technology with a 1.8 V supply voltage. To improve the conversion speed, a partial split capacitor switching scheme is proposed. By reducing the time constant of the bit cycles, the proposed technique shortens the settling time of a capacitive digital-to-analog converter (DAC). In addition, a new SAR control logic is proposed to reduce loop delay to further enhance the conversion speed. At 1.8 V supply voltage and 50 MS/s the SAR ADC achieves a signal-to-noise and distortion ratio (SNDR) of 57.5 dB and spurious-free dynamic range (SFDR) of 69.3 dB. The power consumption is 2.26 mW and the core die area is 0.096 mm2.-

Keywords:

- SAR ADC,

- switching scheme,

- SAR control logic,

- DAC,

- comparator

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] -

Proportional views

DownLoad:

DownLoad: