| Citation: |

Patrick W. C. Ho, Haider Abbas F. Almurib, T. Nandha Kumar. Memristive SRAM cell of seven transistors and one memristor[J]. Journal of Semiconductors, 2016, 37(10): 104002. doi: 10.1088/1674-4926/37/10/104002

****

P. W. C. Ho, H. A. F. Almurib, T. N. Kumar. Memristive SRAM cell of seven transistors and one memristor[J]. J. Semicond., 2016, 37(10): 104002. doi: 10.1088/1674-4926/37/10/104002.

|

Memristive SRAM cell of seven transistors and one memristor

DOI: 10.1088/1674-4926/37/10/104002

More Information

-

Abstract

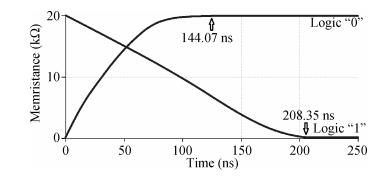

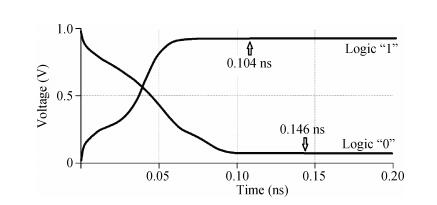

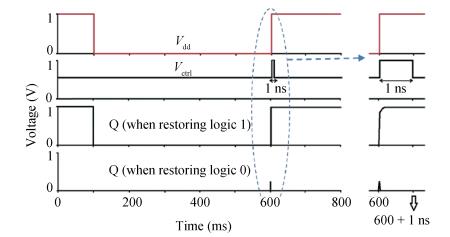

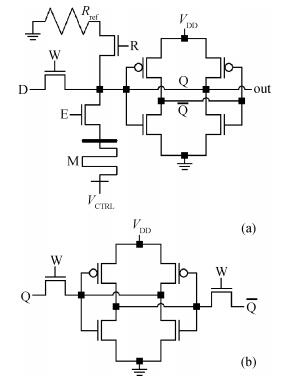

In this work, a novel memristive SRAM cell is designed using seven transistors and one memristor (7T1M). In this 7T1M SRAM cell, the non-volatile functionality is achieved by adding a single memristor and a transistor to the design of a volatile SRAM cell. The designing of the 7T1M SRAM cell also introduces VCTRL which allows bidirectional current flowing through the memristor, instead of relying on complementary input sources which would require more design components. In this article, memristive SRAM cells available from the literature are simulated using the same simulation environment for a fair comparison. Simulations show that the 7T1M SRAM cell has the least power consumption against other memristive SRAM cells in the literature. The 7T1M SRAM cell operates with an average switching speed of 176.21 ns and an average power consumption of 2.9665 μW. The 7T1M SRAM cell has an energy-delay-area product value of 1.61, which is the lowest among the memristive SRAM cells available in the literature.-

Keywords:

- memristor,

- memristive SRAM cell,

- EDAP,

- non-volatile memory cell

-

References

[1] Cai Jiangzheng, Zhang Sumin, Yuan Jia, et al. A 320 mV, 6 kb subthreshold 10 T SRAM employing voltage lowering techniques.Journal of Semiconductors, 2015, 36(6): 065007 doi: 10.1088/1674-4926/36/6/065007[2] Sharma V K, Pattanaik M. VLSI scaling methods and low power CMOS buffer circuit. Journal of Semiconductors, 2013, 34(9): 095001 doi: 10.1088/1674-4926/34/9/095001[3] Seo H, Song D, Lee J, et al. A study on the memristor-based non-volatile 4 T static RAM cell. International Technical Conference on Circuits/Systems, Computers and Communications, 2011[4] Sheu S, Kuo C, Chang M, et al. A ReRAM integrated 7T2R non-volatile SRAM for normally-off computing application. IEEE Asian Solid-State Circuits Conference (A-SSCC), 2013: 245[5] Shuto Y, Yamamoto S, Sugahara S. Comparative study of power-gating architectures for nonvolatile SRAM cells based on spintronics technology. 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), 2014: 699[6] Wang L, Zhang C, Chen L, et al. A novel memristor-based rSRAM structure for multiple-bit upsets immunity. IEICE Electron Express, 2012, 9(9): 861 doi: 10.1587/elex.9.861[7] Kumar T N, Almurib H A F, Lombardi F. A novel design of a memristor-based look-up table (LUT) for FPGA. IEEE Asia Pacific Conference on Circuits & Systems, 2013: 703[8] Duan S, Hu X, Wang L, et al. Memristor-based RRAM with applications. Sci China Inf Sci, 2012, 55(6): 1446 doi: 10.1007/s11432-012-4572-0[9] Lakys Y, Zhao W, Klein J O, et al. MRAM crossbar based configurable logic block. IEEE International Symposium on Circuits and Systems (ISCAS), 2012: 2945[10] Predictive Technology Model. [Online]. Available: http://ptm.asu.edu/.[11] Ho P W C, Hatem F O, Almurib H A F, et al. Enhanced SPICE memristor model with dynamic ground. IEEE International Circuits and Systems Symposium (ICSyS), 2015: 130[12] Pickett M D, Strukov D B, Borghetti J L, et al. Switching dynamics in titanium dioxide memristive devices. J Appl Phys, 2009, 106(7): 074508 doi: 10.1063/1.3236506 -

Proportional views

DownLoad:

DownLoad: